Dynamic Coprocessor Management for

FPGA-Enhanced Compute Platforms

Chen Huang and Frank Vahid*

Department of Computer Science and Engineering University of

California, Riverside {chuang/vahid}@cs.ucr.edu

*also with the Center for Embedded Computer Systems, Univ. of

California, Irvine

ABSTRACT

Various commercial programmable compute platforms have their processor

architecture enhanced with field-programmable gate arrays (FPGAs). In a

common usage scenario, an application loads custom processors into the

FPGA to speed up application execution compared to processor-only

execution. Transient applications, changing application workloads, and

limited FPGA capacity have led to a new problem of

operating-system-controlled dynamic management of the loading of

coprocessors into the FPGAs for best overall performance or energy. We

define the Dynamic Coprocessor Management problem and provide a mapping

to an online optimization problem known as Metrical Task Systems. We

introduce a robust heuristic, called the adjusting cumulative benefit

(ACBenefit) heuristic, that outperforms other heuristics, including a

previously developed one for MTS. For two distinct application sets, we

generate numerous workloads and show that the ACBenefit heuristic to

provide best results across all considered workloads. In our

simulations, the heuristic’s results were within 9% of the offline

optimal for performance, and within 3% for energy. The heuristic may be

applicable to a wide variety of dynamic architecture management

problems.

Problem overview:

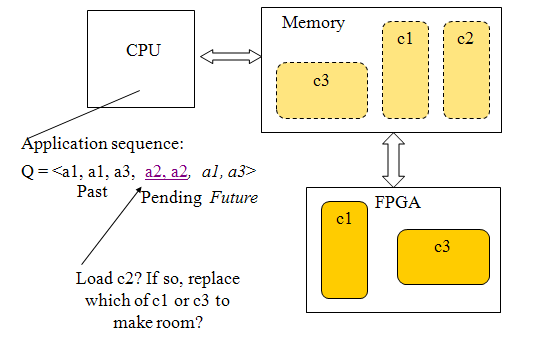

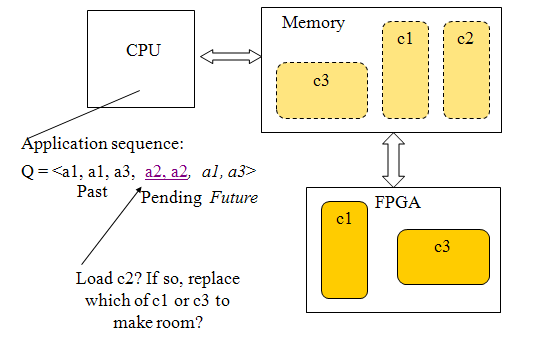

The dynamic coprocessor management (DCM) problem

for time is defined as an online problem: For each application in the

application queue, using only knowledge of prior and current applications

in the queue, determine whether to load that

application’s coprocessor, such that time for the entire queue

(including future applications) is minimized.

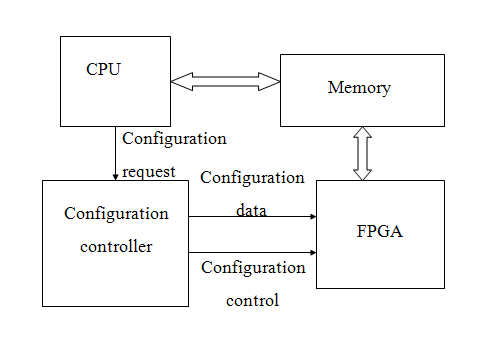

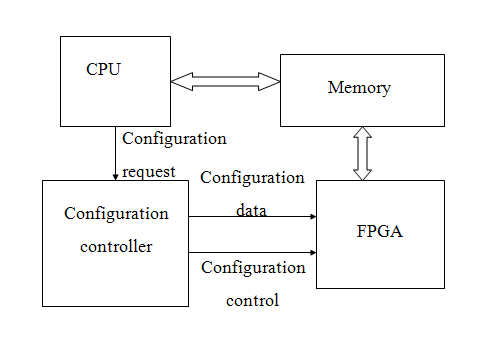

Figure 1: The architecture overview

Figure 2: Online replacement decision

Resources:

- The entire paper. (PDF)

- The data. (EXCEL)

- The source code. (dcm.cpp)

Copyright

2008 UC

Regents. Permission to use or modify is granted for education and

research

purposes only.

Any other use

requires explicit permission. Contact Frank Vahid at vahid@cs.ucr.edu

with

questions.

For publications

derived from these materials, kindly cite the following:

C. Huang and F.

Vahid. Dynamic Coprocessor Management for FPGA-Enhanced Compute

Platforms.

IEEE/ACM Int. Conf.

on Compilers, Architectures, and Synthesis for Embedded Systems

(CASES), Oct

2008.