#### UNIVERSITY OF CALIFORNIA RIVERSIDE

The SpiceC Parallel Programming System

#### A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Computer Science

by

Min Feng

September 2012

Dissertation Committee:

Dr. Rajiv Gupta, Chairperson Dr. Laxmi N. Bhuyan Dr. Iulian Neamtiu

Copyright by Min Feng 2012 The Dissertation of Min Feng is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

This thesis would not have been possible without all people who have supported and inspired me during my doctoral study.

I own my deepest gratitude to my advisor, Dr. Rajiv Gupta, for his continuous support of my research and study. I always feel motivated by his perpetual enthusiasm in research and unshakable belief in my potential. He guided and inspired me to find and pursue my own ideas, which made research life enjoyable and rewarding for me. I could not have imagined having a better advisor for my doctoral study.

Dr. Laxmi N. Bhuyan and Dr. Iulian Neamtiu deserve a thank as my thesis committee members. I am grateful to them for their help in this dissertation. I would also like to thank them for their guidance and help in our joint work.

I would like to express my gratitude to all my lab buddies: Chen Tian, Dennis Jeffrey, Vijay Nagarajan, Changhui Lin, Yan Wang, Kishore K. Pusukuri, Li Tan, and Sai Charan for helping me in many ways during these years. In particular, I would like to thank Chen Tian for his help to get my research started.

Finally, I would like to thank my family, particularly my wife Yi Hu, and my parents Huiyuan Feng and Huixue Cai. Their unconditional support help me overcome all kinds of difficulties I encoutered during my doctoral study. To my wife and parents for all the support.

#### ABSTRACT OF THE DISSERTATION

The SpiceC Parallel Programming System

by

Min Feng

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, September 2012 Dr. Rajiv Gupta, Chairperson

As parallel systems become ubiquitous, exploiting parallelism becomes crucial for improving application performance. However, the complexities of developing parallel software are major challenges. Shared memory parallel programming models, such as OpenMP and Thread Building Blocks (TBBs), offer a single view of the memory thereby making parallel programming easier. However, they support limited forms of parallelism. Distributed memory programming models, such as the Message Passing Interface (MPI), support more parallelism types; however, their low level interfaces require great deal of programming effort.

This dissertation presents the SpiceC system that simplifies the task of parallel programming while supporting different forms of parallelism and parallel computing platforms. SpiceC provides easy to use directives to express different forms of parallelism, including DOALL, DOACROSS, and pipelining parallelism. SpiceC is based upon an intuitive computation model in which each thread performs its computation in isolation from other threads using its *private space* and communicates with other threads via the *shared*  *space.* Since, all data transfers between shared and private spaces are explicit, SpiceC naturally supports both shared and distributed memory platforms with ease.

SpiceC is designed to handle the complexities of real world applications. The effectiveness of SpiceC is demonstrated both in terms of delivered performance and the ease of parallelization for applications with the following characteristics. Applications that cannot be statically parallelized due to presence of dependences, often contain large amounts of input dependent and dynamic data level parallelism. SpiceC supports *speculative parallelization* for exploiting dynamic parallelism with minimal programming effort. Applications that operate on large data sets often make extensive use of *pointer-based dynamic data structures.* SpiceC provides support for partitioning dynamic data structures across threads and then distributing the computation among the threads in a partition sensitive fashion. Finally, due to large input sizes, many applications repeatedly perform I/O operations that are interspersed with the computation. While traditional approach is to execute loops contain I/O operations serially, SpiceC introduces support for *parallelizing computations in the presence of I/O operations.*

Finally, this dissertation demonstrates that SpiceC can handle the challenges posed by the memory architectures of modern parallel computing platforms. The memory architecture impacts the manner in which data transfers between private and shared spaces are implemented. SpiceC does not place the the burden of data transfers on the programmer. Therefore portability of SpiceC to different platforms is achieved by simply modifying the handling of data transfers by the SpiceC compiler and runtime. First, it is shown how SpiceC can be targeted to shared memory architectures both with and without hardware support for cache coherence. Next it is shown how accelerators such as GPUs present in heterogeneous systems are exploited by SpiceC. Finally, the ability of SpiceC to exploit the scalability of a distributed-memory system, consisting of a cluster of multicore machines, is demonstrated.

# Contents

| List of Figures | xiii |

|-----------------|------|

| List of Tables  | xvi  |

| 1 Introduction  | 1    |

| 1        | Inti | roduction 1                      |                                |    |

|----------|------|----------------------------------|--------------------------------|----|

|          | 1.1  | Dissertation Overview            |                                | 3  |

|          |      | 1.1.1 SpiceC System for Multice  | ores                           | 4  |

|          |      | 1.1.2 Support for Dynamic Link   | ked Data Structures            | 5  |

|          |      | 1.1.3 Support for Parallelism in | the Presence of I/O Operations | 7  |

|          |      | 1.1.4 SpiceC on Heterogeneous    | Multicores with GPUs           | 9  |

|          |      | 1.1.5 SpiceC on Distributed Me   | emory Clusters                 | 11 |

|          | 1.2  | Dissertation Organization        |                                | 12 |

| <b>2</b> | Spie | ceC on Multicore Systems         | 1                              | 13 |

|          | 2.1  | Č,                               |                                | 14 |

|          |      |                                  |                                | 14 |

|          |      |                                  |                                | 17 |

|          |      |                                  |                                | 19 |

|          |      |                                  |                                | 21 |

|          |      | _                                |                                | 23 |

|          |      |                                  |                                | 26 |

|          | 2.2  | -                                |                                | 29 |

|          |      |                                  |                                | 30 |

|          |      |                                  |                                | 33 |

|          | 2.3  | _                                |                                | 35 |

|          |      |                                  |                                | 36 |

|          |      | 2.3.2 Performance of the Relaxe  | ed Model                       | 38 |

|          |      |                                  |                                | 40 |

|          | 2.4  |                                  |                                | 43 |

| 3 | Sup | oport for Speculative Execution                           | 44               |

|---|-----|-----------------------------------------------------------|------------------|

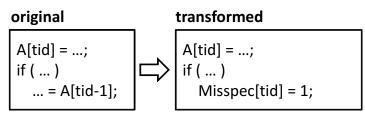

|   | 3.1 | Code Generation for Speculative Execution                 | 46               |

|   |     |                                                           | 48               |

|   |     | 3.1.2 Code Instrumentation                                | 49               |

|   | 3.2 | Support for Library Functions                             | 53               |

|   | -   | 3.2.1 Precompiled Library Functions                       | 53               |

|   |     | 3.2.2 Irreversible Functions                              | 58               |

|   | 3.3 |                                                           | 60               |

|   | 0.0 |                                                           | 62               |

|   |     |                                                           | 63               |

|   |     |                                                           | 64               |

|   | 3.4 | -                                                         | 66               |

|   | 0.1 | U U                                                       | 66               |

|   |     | 0                                                         | 67               |

|   | 3.5 |                                                           | 68               |

|   | 0.0 |                                                           | 68               |

|   |     | 3.5.2       Real Applications                             | 74               |

|   | 3.6 |                                                           | 77               |

|   | 5.0 |                                                           | 11               |

| 4 | -   | 1 0                                                       | 79               |

|   | 4.1 |                                                           | 80               |

|   | 4.2 | Partitioning Support                                      | 83               |

|   |     | 4.2.1 Graph Partitioning                                  | 84               |

|   |     | 4.2.2 Tree Partitioning                                   | 86               |

|   |     |                                                           | 91               |

|   | 4.3 | 0 0 11                                                    | 93               |

|   |     | 1 8                                                       | 94               |

|   |     | 1 0                                                       | 97               |

|   |     | 4.3.3 Speculative Parallelism                             | 02               |

|   | 4.4 | Evaluation                                                | .08              |

|   |     | 1                                                         | .09              |

|   |     |                                                           | .09              |

|   |     | 4.4.3 Performance                                         | .12              |

|   |     | 4.4.4 Effectiveness of Conditional Speculation            | 13               |

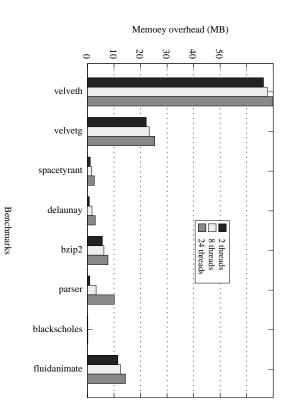

|   |     | 4.4.5 Overhead                                            | 15               |

|   | 4.5 | Summary                                                   | 16               |

| 5 | S   | oport for Parallelism in the Presence of I/O Operations 1 | 17               |

| J | 5.1 | ·                                                         | <b>1</b> 7<br>19 |

|   | 0.1 |                                                           | .19              |

|   |     |                                                           | .23<br>.26       |

|   |     |                                                           |                  |

|   | E O | , 1 0                                                     | .27              |

|   | 5.2 |                                                           | .28              |

|   |     | 5.2.1 Programming Parallel Hybrid Loops                   | 28               |

|   |      | 5.2.2  | Implementation                                                                                                                                         | 38 |

|---|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 5.3  | Evalua | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $14$                                                                                                | 42 |

|   |      | 5.3.1  | Benchmarks                                                                                                                                             | 43 |

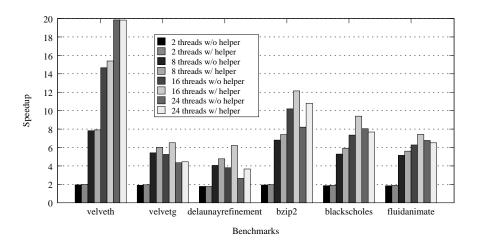

|   |      | 5.3.2  | Performance                                                                                                                                            | 45 |

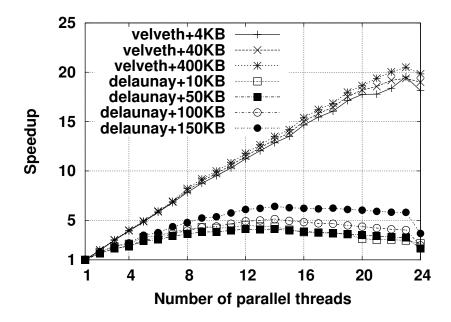

|   |      | 5.3.3  | Impact of Helper Threading                                                                                                                             | 17 |

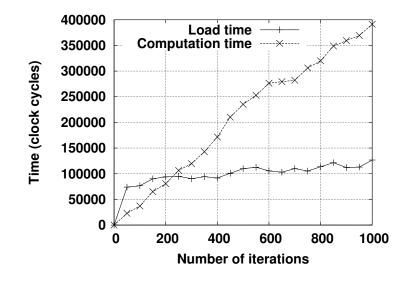

|   |      | 5.3.4  | Overhead                                                                                                                                               | 50 |

|   | 5.4  | Summ   | ary                                                                                                                                                    | 52 |

| 6 | Spic | ceC on | Heterogeneous Multicores with GPUs 15                                                                                                                  | 53 |

|   | 6.1  | Execut | tion Framework                                                                                                                                         | 55 |

|   | 6.2  | Specul | lative Execution on GPUs                                                                                                                               | 57 |

|   |      | 6.2.1  | Irregular memory accesses                                                                                                                              | 58 |

|   |      | 6.2.2  | Irregular Control Flows 16                                                                                                                             | 64 |

|   | 6.3  | Comm   | it and Recovery $\ldots \ldots \ldots$ | 38 |

|   | 6.4  | Schedu | ıling                                                                                                                                                  | 70 |

|   | 6.5  | Progra | amming Speculative Parallel Loops on GPUs                                                                                                              | 72 |

|   |      | 6.5.1  | Irregular Memory Accesses 17                                                                                                                           | 73 |

|   |      | 6.5.2  | Irregular Control Flows 17                                                                                                                             | 74 |

|   | 6.6  | Evalua | $tion \ldots 17$                | 77 |

|   |      | 6.6.1  | Benchmarks                                                                                                                                             | 78 |

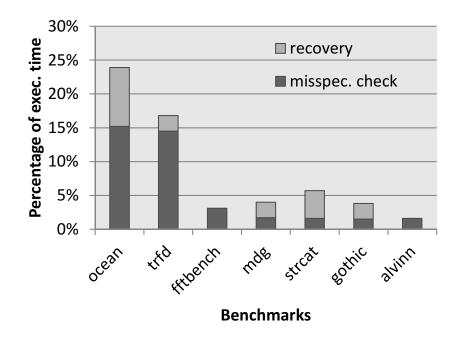

|   |      | 6.6.2  | Performance Overview                                                                                                                                   | 80 |

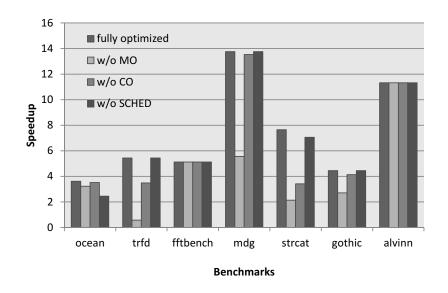

|   |      | 6.6.3  | Effectiveness of the Optimizations                                                                                                                     | 31 |

|   |      | 6.6.4  | Overhead                                                                                                                                               | 33 |

|   | 6.7  | Summ   | ary                                                                                                                                                    | 86 |

| 7 | Spie | ceC on | Distributed Memory Clusters 18                                                                                                                         | 37 |

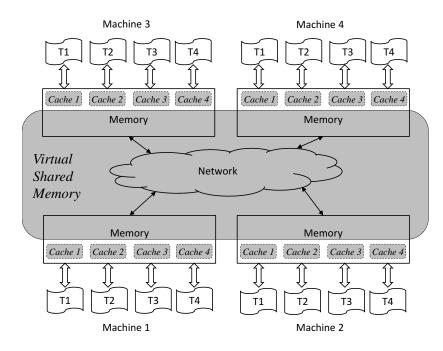

|   | 7.1  | Shared | l Memory Abstraction                                                                                                                                   | 39 |

|   |      | 7.1.1  | Definition of Shared Data 18                                                                                                                           | 39 |

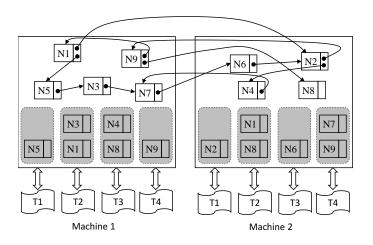

|   |      | 7.1.2  | Data Distribution                                                                                                                                      | 91 |

|   |      | 7.1.3  | Data Reference                                                                                                                                         | 91 |

|   |      | 7.1.4  | Sequential Consistency                                                                                                                                 | 92 |

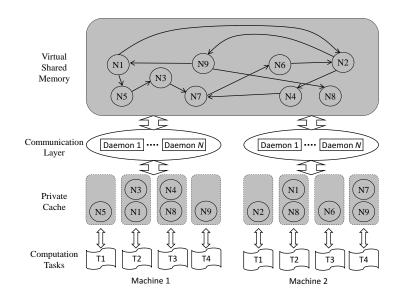

|   | 7.2  | Proact | vive Data Communication                                                                                                                                | )3 |

|   | 7.3  | SpiceC | C Programming on Clusters                                                                                                                              | 95 |

|   | 7.4  | Evalua | $tion \ldots 19$                | 97 |

|   |      | 7.4.1  | Benchmarks                                                                                                                                             | 98 |

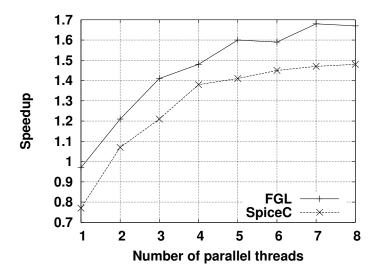

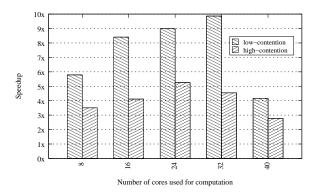

|   |      | 7.4.2  | Scalability                                                                                                                                            | 99 |

|   |      | 7.4.3  | Impact of Copying and Commit Model                                                                                                                     | 00 |

|   |      | 7.4.4  |                                                                                                                                                        | )1 |

|   |      | 7.4.5  | Impact of Data Contention                                                                                                                              | )2 |

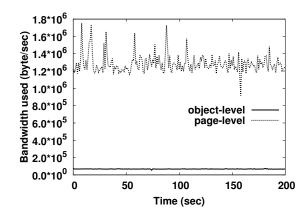

|   |      | 7.4.6  | Bandwidth Consumption                                                                                                                                  | )3 |

|   | 7.5  | Summ   | ary                                                                                                                                                    | )4 |

| 8 | Rela | ated W  | /ork                                  | 205 |

|---|------|---------|---------------------------------------|-----|

|   | 8.1  | Paralle | el Programming                        | 205 |

|   |      | 8.1.1   | Shared Memory Systems                 | 206 |

|   |      | 8.1.2   | Distributed Memory Systems            | 208 |

|   |      | 8.1.3   | Heterogeneous Systems With GPUs       | 211 |

|   | 8.2  | Specul  | ation Execution                       | 212 |

|   |      | 8.2.1   | Automatic Speculative Parallelization | 212 |

|   |      | 8.2.2   | Transactional Memory Based Compilers  | 213 |

|   | 8.3  | Other   | Works on Enhancing Performance        | 216 |

|   |      | 8.3.1   | Enhancing Performance on GPUs         | 216 |

|   |      | 8.3.2   | Enhancing I/O Performance             | 216 |

| 9 | Con  | clusio  | ns                                    | 219 |

|   | 9.1  | Contri  | butions                               | 219 |

|   | 9.2  | Future  | Direction                             | 222 |

#### Bibliography

# List of Figures

| 1.1  | An overview of SpiceC                                                                  |

|------|----------------------------------------------------------------------------------------|

| 1.2  | Misspeculation rates of four applications that use dynamic data structures. 6          |

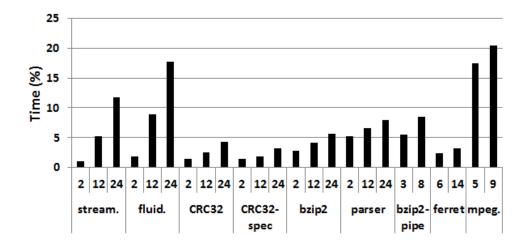

| 1.3  | The percentage of total execution time taken by the hybrid loops in eight applications |

| 1.4  | Potential loop speedups of three applications achieved on a GPU 10                     |

| 1.5  | Percentage of the execution time taken by network communication 12                     |

| 2.1  | SpiceC Computation Model                                                               |

| 2.2  | Communicating parallel threads written in SpiceC                                       |

| 2.3  | K-means clustering algorithm written in SpiceC                                         |

| 2.4  | A typical stream decoder written in SpiceC                                             |

| 2.5  | Stream decoder parallelized using pipelining parallelism                               |

| 2.6  | Kernel of benchmark telecomm-CRC32                                                     |

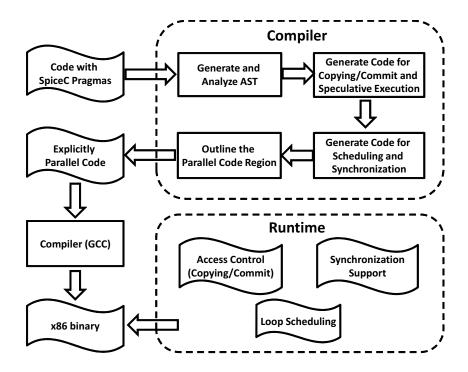

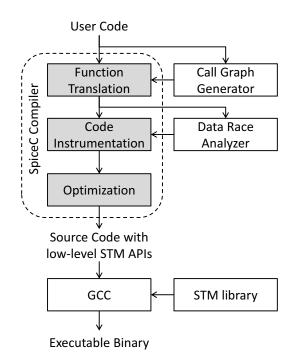

| 2.7  | Overview of SpiceC implementation                                                      |

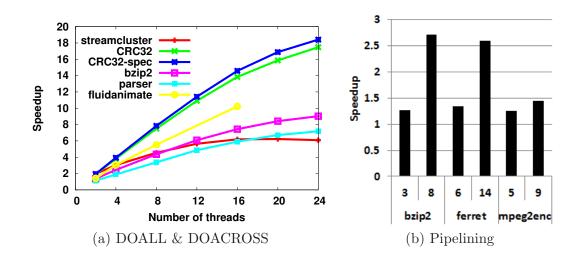

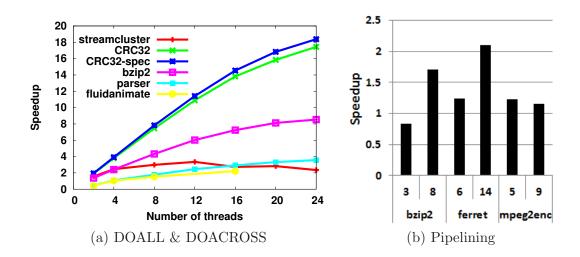

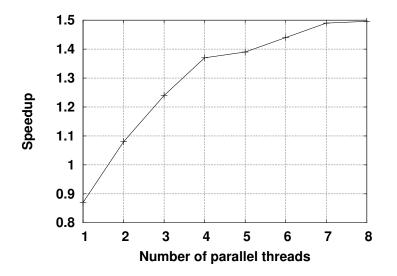

| 2.8  | Speedup with the relaxed model                                                         |

| 2.9  | Parallelization overhead with the relaxed model                                        |

| 2.10 | Speedup with the strict model                                                          |

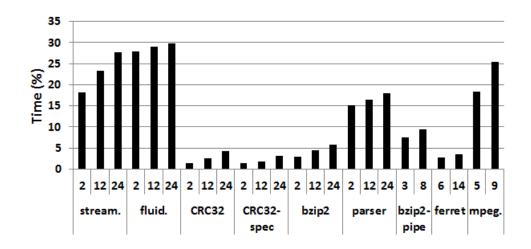

| 2.11 | Time overhead with the strict model. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $43$          |

| 3.1  | Overview of code generation                                                            |

| 3.2  | Code translation for a dynamically-called function                                     |

| 3.3  | Syntax of the precompiled construct                                                    |

| 3.4  | Using the precompiled construct to annotate function declarations 54                   |

| 3.5  | Using the precompiled construct to annotate function call sites                        |

| 3.6  | The translated call to precompiled function memcpy                                     |

| 3.7  | Using the suspend construct to annotate function declarations                          |

| 3.8  | Using the suspend construct to annotate function call sites                            |

| 3.9  | Translated call to irreversible function putchar                                       |

| 3.10 | An example of intermediate code with read/write barriers                               |

|      | Intermediate code with temporary variables                                             |

| 3.12 | Final code after redundancy elimination                                                |

|            | Busy waiting inside a transaction.                                           | 65           |

|------------|------------------------------------------------------------------------------|--------------|

| 3.14       | Busy waiting using the beforevalidate construct                              | 66           |

| 3.15       | An example of aliasing.                                                      | 67           |

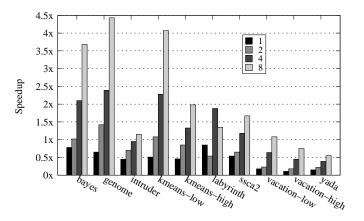

| 3.16       | Speedups over sequential versions of the same programs achieved by the       |              |

|            | SpiceC compiler using 1, 2, 4, and 8 threads.                                | 70           |

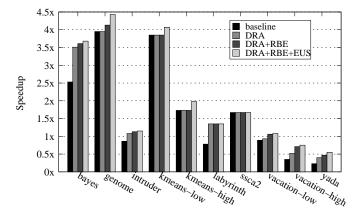

| 3.17       | Performance with different optimizations.                                    | 72           |

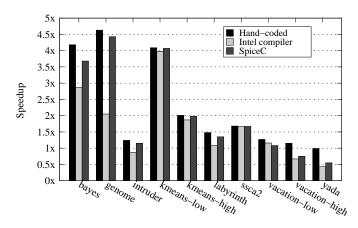

| 3.18       | Performance comparison of the hand-coded transactional code, the Intel STM   |              |

|            | compiler, and the SpiceC compiler                                            | 73           |

|            | Speedups of Velvet over its sequential version                               | 76           |

| 3.20       | Speedup of ITI over its sequential version                                   | 77           |

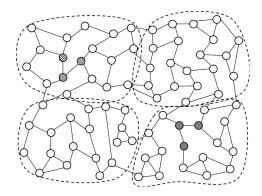

| 4.1        | Parallel computation in a graph with spatial locality.                       | 85           |

| 4.2        | Breadth first search - an example of parallel computation in a graph without |              |

|            | spatial locality.                                                            | 85           |

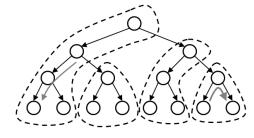

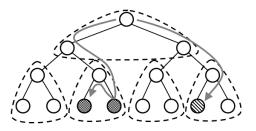

| 4.3        | Parallel computations starting at an internal/leaf node.                     | 88           |

| 4.4        | Parallel computations starting from the root node                            | 88           |

| 4.5        | Asymmetric tree partitioning algorithm.                                      | 89           |

| 4.6        | Symmetric tree partitioning algorithm.                                       | 92           |

| 4.7        | Example of manual partitioning.                                              | 93           |

| 4.8        | Pseudocode for parallel BFS with graph partitioning                          | 95           |

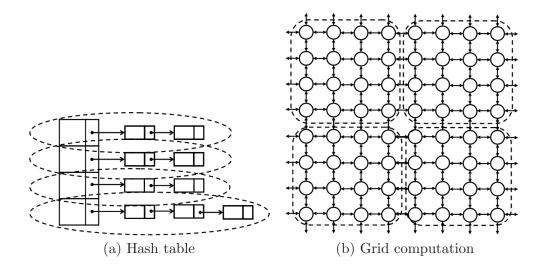

| 4.9        | Parallel hash table lookup with partitioning                                 | 98           |

|            | Pseudocode for parallel binary search with tree partitioning                 | 100          |

|            | Pseudocode for parallel recursion computation with tree partitioning         | 101          |

|            | Parallel Delaunay Mesh Refinement with graph partitioning.                   | 104          |

|            | Pseudocode for building cavity in Delaunay Mesh Refinement                   | 107          |

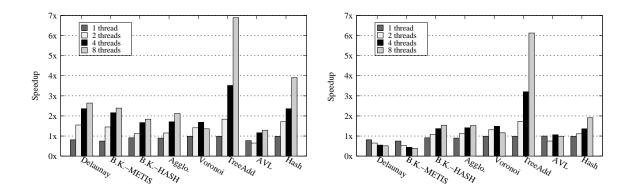

|            | Speedup with partitioning                                                    | 112          |

|            | Speedup without partitioning                                                 | 112          |

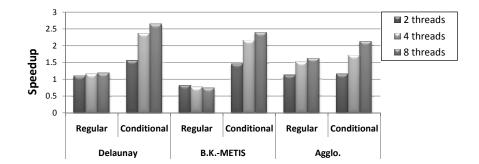

|            | Regular speculation vs. Conditional speculation                              | 113          |

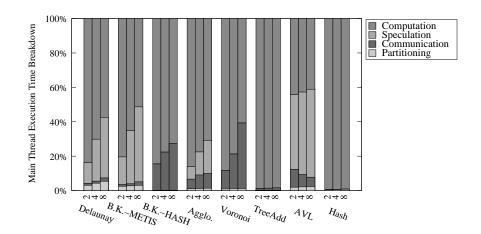

|            | Time breakdown of the master thread.                                         | 115          |

| F 1        |                                                                              | 190          |

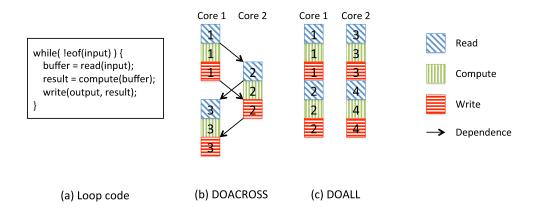

| 5.1<br>5.2 | Execution of the loop example                                                | $120 \\ 121$ |

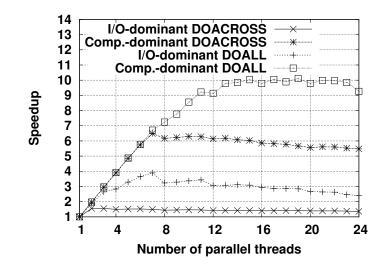

| 5.2<br>5.2 | Performance comparison of DOACROSS and DOALL on the example loop.            | 121          |

| 5.3        | Performance of reading a 1 GB file using different numbers of parallel I/O   | 100          |

| F 4        | requests                                                                     | 122          |

| 5.4        | Commonly used file access patterns of loops and strategies for locating the  | 100          |

|            | starting file position for each parallel thread.                             | 123          |

| 5.5        | Strategies for flushing the output buffer                                    | 126          |

| 5.6        | An input loop of benchmark <i>DelaunayRefinement</i> .                       | 131          |

| 5.7        | An output loop of bioinformatics application Velvet                          | 133          |

| 5.8        | Speculative parallelization of a kernel from <i>Parser</i>                   | 135          |

| 5.9        | Example of using I/O helper threads                                          | 137          |

| 5.10       | Example of code transformation.                                              | 139          |

|            | Buffer layout.                                                               | 141          |

| 5.12       | Absolute parallelized application speedup over sequential programs           | 146          |

| 5.13 | Relative speedup: with hybrid loop parallelization vs. without hybrid loop                        |     |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | parallelization.                                                                                  | 148 |

| 5.14 | Impact of helper threading.                                                                       | 149 |

| 5.15 | Speedup by varying buffer size                                                                    | 149 |

| 5.16 | Computation time vs. data load time of benchmark <i>DelaunayRefinement</i>                        | 150 |

| 5.17 | Breakdown of hybrid loop execution time                                                           | 151 |

| 5.18 | Memory overhead.                                                                                  | 151 |

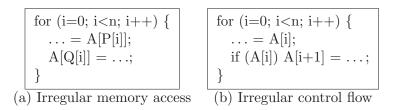

| 6.1  | Examples of dynamic irregularities that cause cross-iteration dependences                         | 154 |

| 6.2  | Execution framework of a speculative parallel loop with GPUs                                      | 155 |

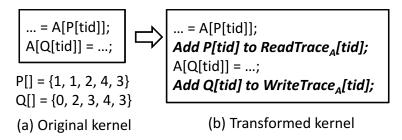

| 6.3  | Code transformation of a loop with irregular memory accesses                                      | 158 |

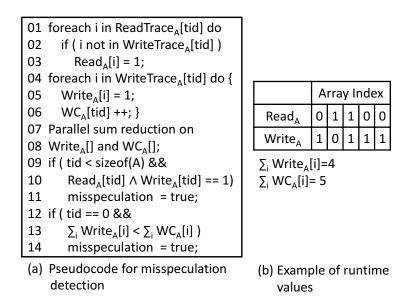

| 6.4  | Misspeculation detection.                                                                         | 160 |

| 6.5  | Misspeculation localization.                                                                      | 162 |

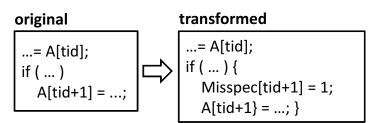

| 6.6  | Loops with irregular control flows.                                                               | 165 |

| 6.7  | The pseudocode of commit and misspeculation recovery for the example given                        |     |

|      | in Figure 6.3                                                                                     | 168 |

| 6.8  | A speculatively parallel loop from benchmark ocean                                                | 173 |

| 6.9  | A loop with irregular control flow from benchmark mdg                                             | 176 |

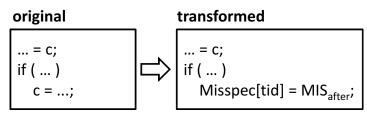

| 6.10 | Loop speedups for different optimization.                                                         | 181 |

| 6.11 | Time overhead.                                                                                    | 184 |

| 6.12 | Memory overhead for misspeculation check                                                          | 185 |

| 7.1  | Memory hierarchy of SpiceC-DSM on a modern cluster.                                               | 190 |

| 7.2  | An example of dynamic data structure stored in SpiceC-DSM                                         | 191 |

| 7.3  | Data communication in SpiceC-DSM.                                                                 | 193 |

| 7.4  | Pseudocode for graph coloring.                                                                    | 196 |

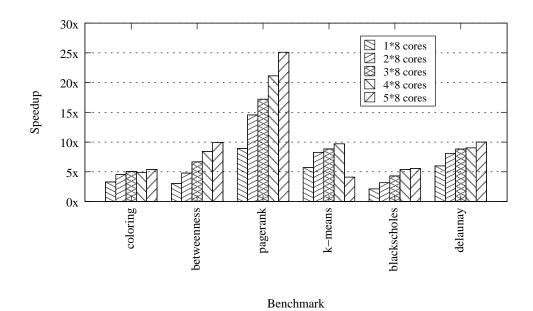

| 7.5  | Application speedups                                                                              | 200 |

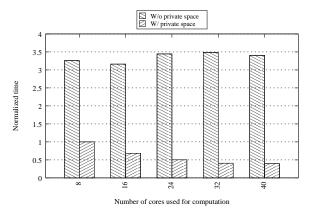

| 7.6  | Execution time of <b>blackscholes</b> with and without private spaces                             | 201 |

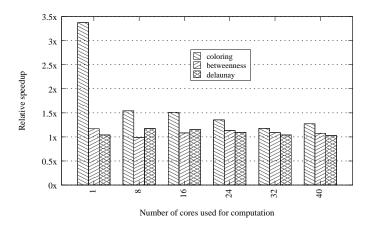

| 7.7  | Relative speedup: with proactive communication vs. without proactive com-                         | 001 |

| 7 0  | munication.                                                                                       | 201 |

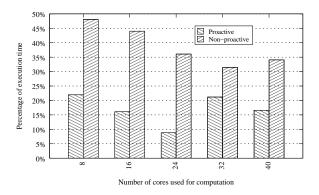

| 7.8  | Speculation overhead in the execution of graph coloring with and without proactive communication. | 202 |

| 7.9  | Speedups of ${\tt k-means}$ with high data contention and low data contention.                    | 203 |

| 7.10 | Comparison of page-level and object-level data transfer.                                          | 203 |

# List of Tables

| 2.1        | Compiler directives implemented by SpiceC                                                                                                                                                                                                                                                                                                                                                   | 20       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2<br>2.3 | Dell PowerEdge R905 machine details                                                                                                                                                                                                                                                                                                                                                         | 35<br>36 |

| 3.1        | A comparison of programming burden for writing speculatively executed code. <i>Manual</i> — tasks done manually by the programmer; <i>Auto</i> — tasks done automatically by the compiler.                                                                                                                                                                                                  | 45       |

| 3.2        | The low-level STM API used in translated code.                                                                                                                                                                                                                                                                                                                                              | 50       |

| 3.3        | Machine details.                                                                                                                                                                                                                                                                                                                                                                            | 68       |

| 3.4        | Benchmark summary and programming effort (number of constructs) when<br>using the low-level STM API, the Intel STM compiler, and the SpiceC com-<br>piler. Programming effort using the low-level STM API is split into con-<br>structs used for read/write barriers and others, while programming effort<br>using the SpiceC compiler is split into constructs used for transaction bound- |          |

| 3.5        | aries, precompiled functions, and irreversible functions                                                                                                                                                                                                                                                                                                                                    | 69<br>72 |

| 4.1        | Summary of partitioning strategies.                                                                                                                                                                                                                                                                                                                                                         | 83       |

| 4.2        | Machine details.                                                                                                                                                                                                                                                                                                                                                                            | 108      |

| 4.3        | Benchmark details. From left to right: benchmark name; function where the parallel region is located and type of parallelism (homogeneous and hetero-<br>geneous); lines of code in the function and number of pragmas introduced; type of data structure used in the benchmark; partitioning strategy employed;                                                                            |          |

|            | whether speculation is used and whether conditional speculation is used                                                                                                                                                                                                                                                                                                                     | 111      |

| 4.4        | Comparison of misspeculation rates with 8 threads. From left to right: bench-<br>mark name, misspeculation rate without partitioning, and misspeculation                                                                                                                                                                                                                                    |          |

|            | rate with partitioning                                                                                                                                                                                                                                                                                                                                                                      | 113      |

| 4.5        | Postpone rate.                                                                                                                                                                                                                                                                                                                                                                              | 114      |

| 5.1        | Examples of the <i>pinput</i> clause                                                                                                                                                                                                                                                                                                                                           | 130 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2        | APIs for programming I/O helper thread                                                                                                                                                                                                                                                                                                                                         | 136 |

| 5.3        | Low-level functions for buffering outputs.                                                                                                                                                                                                                                                                                                                                     | 138 |

| 5.4        | Dell PowerEdge R905 machine details.                                                                                                                                                                                                                                                                                                                                           | 142 |

| 5.5        | Benchmark summary. From left to right: benchmark name, number of par-<br>allelized hybrid loops, input file access pattern, whether output buffering is<br>used, whether speculative parallelization is used, whether helper threading is<br>used, percentage of total execution time taken by the hybrid loops, number<br>of statements added or modified for parallelization | 143 |

| 6.1<br>6.2 | Machine details                                                                                                                                                                                                                                                                                                                                                                | 177 |

|            | and number of pragmas inserted for parallelization                                                                                                                                                                                                                                                                                                                             | 178 |

| 7.1        | Machine details.                                                                                                                                                                                                                                                                                                                                                               | 198 |

| 7.2        | Benchmark summary.                                                                                                                                                                                                                                                                                                                                                             | 198 |

### Chapter 1

### Introduction

Parallel systems are currently evolving towards massive parallelism and heterogeneity for performance and power efficiency. This trend has created exciting opportunities for achieving increased performance with multithreaded software. Meanwhile, the increasing complexity and variety of parallel systems has made it difficult to efficiently realize the benefits of their computing power via parallelism, as it has also raised many new challenges in software development.

Two types of parallel programming models have been proposed to facilitate the development of parallel applications for modern parallel systems: shared memory programming models; and distributed memory programming models. Existing systems based upon these models have their drawbacks that greatly limit their ability to deal with the complexity of developing multithreaded code for real world applications.

Existing shared memory programming models such as OpenMP [36] and Threading Building Blocks (TBB) [108] have been widely used because they offer a single view of the memory. Developers do not have to be aware of the location of data, thereby making parallel programming easier. However, these parallel programming models have limited applicability. First, they can only be applied to certain types of applications as they only support limited forms of parallelism and are unable to handle parallelism in the presence of popular programming features such as pointer-based linked dynamic data structures and I/O operations. Second, these programming models do not support distributed memory systems since they require a shared physical memory. Although the shared memory programming models are easy to use, they cannot be adopted in many real applications due to the lack of support for various application types and platforms.

Distributed memory programming models such as MPI [52], on the other hand, are more versatile. They do not require any physical shared memory and can be used to exploit more forms of parallelism. They are often used in large-scale applications that demand better scalability. However, the distributed memory programming models are hard to use since their interfaces tend to be low level. Developers need to spend significant effort to explicitly program distribution of workload among threads as well as communication and synchronization of threads. Moreover, to achieve efficient implementation of parallel applications, developers must understand the underlying hardware and undertake the error-prone task of programming optimizations [60]. Even though the distributed memory programming models are more versatile, the programmability issue often prevents them from being used.

This dissertation overcomes the above drawbacks by developing a parallel programming system that combines the programmability of the shared memory programming models and the versatility and portability of the distributed memory programming models. While developing such a system is challenging, its benefit in facilitating parallel programming for wide range of applications and platforms is clear. Developers can exploit parallelism while focusing on high-level algorithmic issues. They do not need to understand the underlying hardware to run their programs on different platforms.

#### 1.1 Dissertation Overview

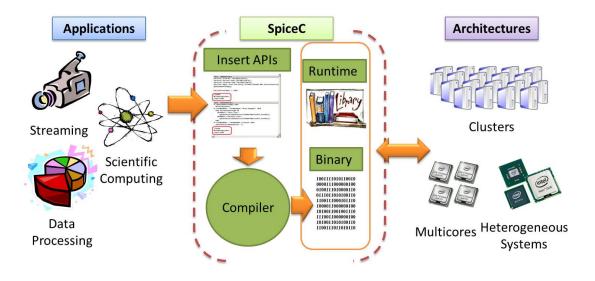

This dissertation presents the SpiceC parallel programming system that enables development of parallel software for various types of applications and platforms with ease. Figure 1.1 provides an overview of SpiceC. The key issues addressed by this system are briefly described next.

Figure 1.1: An overview of SpiceC.

#### 1.1.1 SpiceC System for Multicores

As commercial processors transition from single-core to multicore, parallel programming becomes a challenge on commercial processors. To meet this challenge, programming systems should address the programmability, versatility, and portability issues of parallel programming on multicore processors.

Programmability. The complexity of parallel programming hinders its use by developers. To make programmers more productive, a parallel programming system should use high-level programming style. For example, instead of having the developers write new parallel programs, they could simply add parallelization primitives into the text of an existing sequential program. Parallelism can be exploited by the compiler based on the added primitives.

Versatility. To efficiently parallelize applications, a parallel programming system should support various forms of parallelism as different computations contain different forms of parallelism to exploit. Since the parallelism in many real applications cannot be guaranteed at compile time, speculative parallelization should be supported for dynamically exploiting the parallelism.

Performance portability. A parallel programming system should be able to adapt to different types of multiprocessors. As multiprocessors evolve towards manycores, the scalability of traditional cache coherence protocols, such as snoopy- or directory-based protocols, becomes a problem. Recently, Intel Labs has created their new Tera-scale multiprocessor – "Single-chip Cloud Computer (SCC)" which is a 48-core processor with no cache coherence support. Therefore, in the long term, a parallel programming model should support not only multicore processors with cache coherence but also manycore processors without cache coherence.

The core SpiceC system presented in this dissertation is designed to address the above parallel programming issues for multicore processors. It has a high-level programming model, which is easy to use and designed to exploit multiple forms of parallelism. The compiler translates SpiceC code into explicitly parallel code, exploiting parallelism based on the high-level programming primitives. Its computation model makes it portable across multiprocessors that may or may not support cache coherence.

#### 1.1.2 Support for Dynamic Linked Data Structures

Recently, parallelization of computations in the presence of dynamic data structures has shown promise. Efficient parallel execution in the presence of large dynamic data structures requires exploiting data locality of and speculative parallelism.

Data locality. Data partitioning-based computation distribution [9] has been proposed to exploit data locality on distributed systems. The overall approach involves partitioning the data, assigning the partitions to threads, and finally assigning computations to threads such that the thread that owns the data required by a computation performs the computation. Programming the above strategy is not a trivial task. Developers need to write code for: partitioning and assigning the data to threads; and distributing computation among threads based on the partitioning. They also program required synchronizations between computations for different partitions.

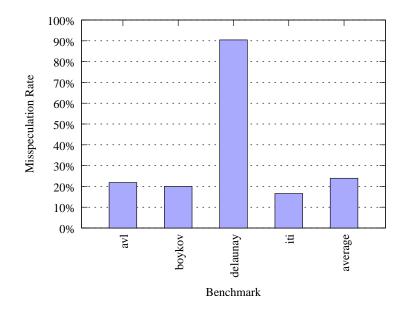

Figure 1.2: Misspeculation rates of four applications that use dynamic data structures.

Speculative parallelism. Mostly each thread works on its assigned partition; however, occasionally multiple threads need to simultaneously access the same data elements of a dynamic data structure. In such situations, the threads are designed to speculatively operate on same elements. However, if the parallel accesses are found to violate data dependences present in sequential version, then misspeculation is detected and the application must be designed to recover from them. It has been observed that the misspeculation rates of applications that use dynamic data structures can be very high. Figure 1.2 shows the misspeculation rates of four applications on a 8-core machine. Since these misspeculation rates are very high (exceeding 15% for all applications), very high recovery overhead will be incurred. To efficiently exploit speculative parallelism, it is necessary to optimize speculative execution to reduce the misspeculation overhead.

This dissertation presents the SpiceC support for dynamic data structures, which

addresses both of the above issues.

#### 1.1.3 Support for Parallelism in the Presence of I/O Operations

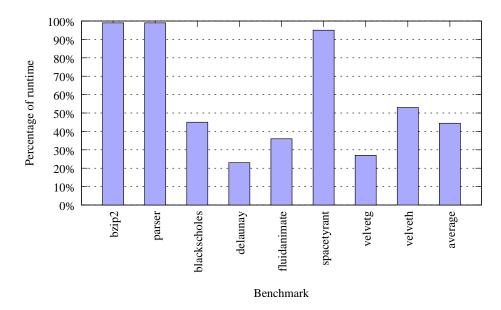

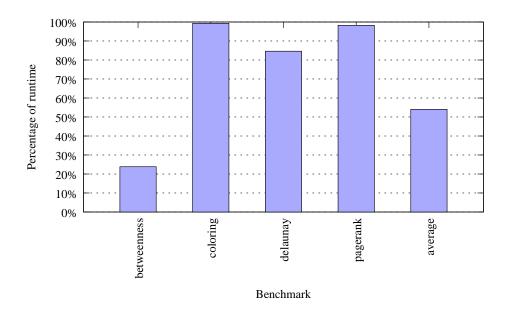

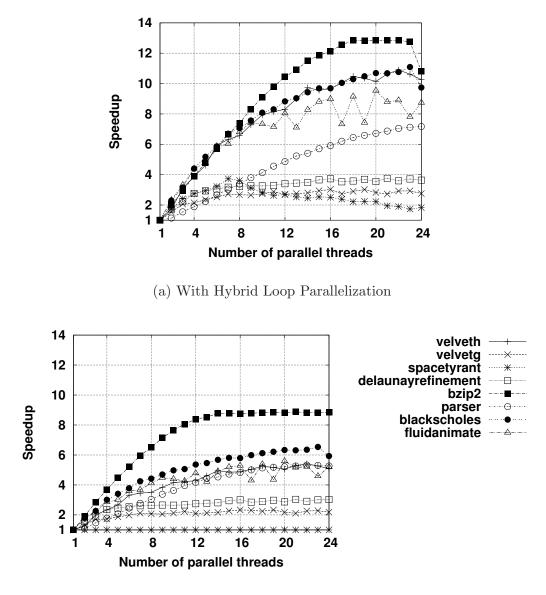

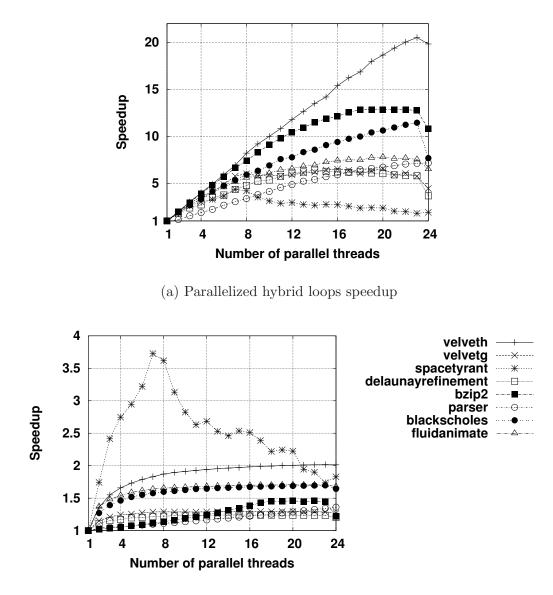

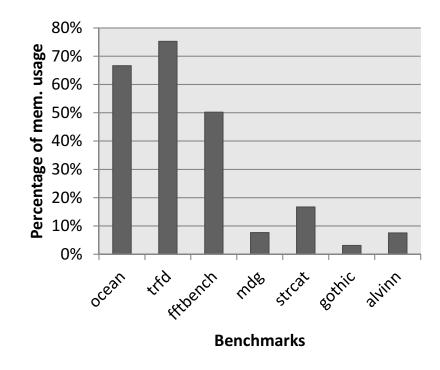

Existing parallel programming models only target loops that contain pure computations, i.e., they are free of I/O operations. Since applications that work on large data sets contain many computatation loops which also contain I/O operations, they fail to yield much speedup when these loops are executed serially. Therefore, it is highly desirable to support parallel programming models which allow parallel execution of *hybrid loops*, i.e., loops with both computation and I/O operations. Figure 1.3 shows the percentage of total execution time taken by the hybrid loops in eight applications on a 24-core machine. We can see that a significant portion of the total execution time is taken by the hybrid loops in all these applications. Therefore, to further improve the performance of these applications, developers must exploit the parallelism in hybrid loops.

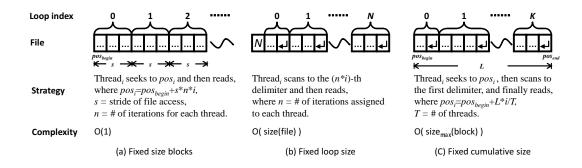

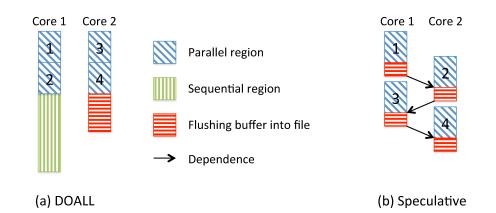

The presence of I/O operations raises the following challenges for parallel programming. First, a hybrid loop has cross-iteration dependences caused by the I/O operations as the file read/write operations from different iterations move the same file pointer. Usually when the computation within a loop does not involve cross-iteration dependences, maximum parallelism can be exploited via DOALL parallelization where all loop iterations can be executed in parallel. However, in a hybrid loop, even when the computation does not involve cross-iteration dependences, DOALL parallelization is not possible due to the crossiteration dependences caused by the I/O operations. Fully exploiting the parallelism in the loop requires a way to break the cross-iteration dependences due to I/O operations.

Figure 1.3: The percentage of total execution time taken by the hybrid loops in eight applications.

Second, cross-iteration dependences may exist in the computation part of a hybrid loop. It is impossible to perform DOALL parallelization of such loops even without the dependences introduced by I/O operations. Speculative parallelization has proven to be an effective approach to handling cross-iteration dependences in the computation part when these dependences manifest themselves infrequently. Previous works on speculative parallelization [126, 43] assume that the loops do not contain I/O operations. To apply speculative parallelization to the hybrid loops, the speculative execution of the I/O operations must be enabled.

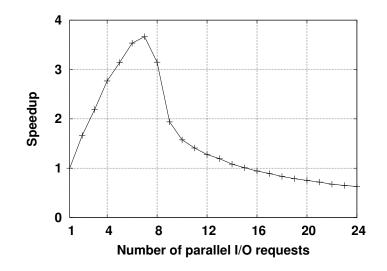

Finally, after a hybrid loop is parallelized, multiple parallel threads may access the I/O bus at the same time. The contention on the I/O bus is increased with the increased parallelism in the hybrid loop. The increased I/O contention may lead to performance degradation. Therefore, techniques for reducing I/O bus contention must be developed to

effectively parallelize hybrid loops.

This dissertation presents the SpiceC support for hybrid loops, which meets the above challenges.

#### 1.1.4 SpiceC on Heterogeneous Multicores with GPUs

Graphics processing units (GPUs) provide an inexpensive, highly parallel system to perform computations that are traditionally handled by CPUs. SpiceC can be easily extended to support GPUs since its computational model can naturally handle the host/device memory hierarchy in heterogeneous systems with GPUs.

A few high-level programming models [76, 10, 14] have been proposed to explore loop-level parallelism using GPUs. To run a loop using the GPU, the programmer or compiler must ensure that there is no cross-iteration dependence. This prevents GPUs from executing loops that may encounter cross-iteration dependences at runtime.

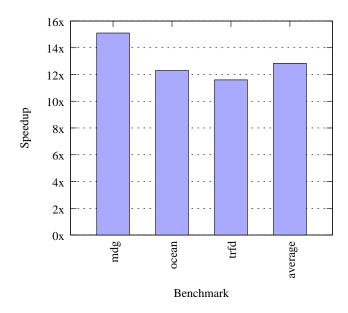

The cross-iteration dependences in many loops rarely manifest themselves at runtime. Although these loops cannot be parallelized statically by any existing programming model, they are good candidates to be executed on GPUs when no cross-iteration dependence happens at runtime. Figure 1.4 shows the loop speedups of three applications achieved on a GPU by assuming the absence of cross-iteration dependence at runtime. These speedups are quite substantial, exceeding a factor of 10x in all cases. Thus, finding a method for running such loops on GPUs is higher desirable.

Speculative parallelization techniques based upon thread level speculation [126, 43], although applicable to CPUs, cannot be directly used on GPUs. This is due to the

Figure 1.4: Potential loop speedups of three applications achieved on a GPU.

architectural differences between CPUs and GPUs. First, they require the results of each speculatively executed iteration to be stored in a logically separate space. GPUs do not have enough memory space to create a separate space for every thread due to thousands of threads. Second, these techniques commit the results of each iteration in a sequential order to preserve the original sequential semantics of the loop. Once misspeculation is detected in an iteration, these techniques require the iteration to be re-executed before committing the results of subsequent iterations. This requires complicated synchronization between threads, which cannot be efficiently implemented on GPUs due to very high GPU synchronization overhead [32].

This dissertation presents an extension to the programming model and runtime support of SpiceC, that enables speculative parallelism on GPUs.

#### 1.1.5 SpiceC on Distributed Memory Clusters

Modern applications from important domains (e.g., data mining, machine learning, and computational geometry) have high processing demands and a *very large memory footprint*. To meet the demands of such applications, it is natural to consider the use of clusters of multicore machines. Clusters can not only scale to a large number of processing cores, they also provide a large amount of memory. They are especially attractive for modern applications because, with the advances in network technology, a cluster can provide an application with a faster storage system than a disk based storage system.

SpiceC can be extended for clusters since its computation model does not necessarily require shared memory. This dissertation addresses the following issues to port SpiceC to a cluster of multicore machines.

Data distribution. To support distributed memory clusters, the SpiceC runtime should be able to spread shared data across different machines. When a parallel thread accesses a shared data item, the runtime must locate the shared data item in the cluster. In case that dynamic linked data structures are used, the runtime should support reference to shared data via pointers.

Tolerating network latency. Network communication on clusters can be time-consuming. Figure 1.5 shows the percentage of the execution time taken by network communication for four applications running on a cluster of five multicore machines. The applications were executed sequentially using the memory from the five machines. In all four applications, network communication takes a significant portion of the execution time. Therefore, to efficiently run programs on clusters, the the network latency must be hidden by being kept

Figure 1.5: Percentage of the execution time taken by network communication. off the critical path of the program execution.

#### 1.2 Dissertation Organization

The rest of this dissertation is organized as follows. Chapter 2 describes the core features of the SpiceC system and its implementation. Chapter 3 discusses the compiler support for efficiently allowing speculative execution in SpiceC. Chapters 4 and 5 present the SpiceC support for parallelization in the presence of dynamic linked data structures and I/O operations. Chapters 6 and 7 describe how SpiceC is extended to take advantage of parallel systems other than multicore processors, i.e., systems with GPUs and distributed memory cluster of multicores. Related work is given in Chapter 8. Chapter 9 summarizes the contributions of this dissertation and identifies directions for future work.

### Chapter 2

### SpiceC on Multicore Systems

Shared memory parallel systems such as multicore processors have been widely used because they offer a single view of the memory thereby making parallel programming easier. Developers do not have to be aware of the location of data. A few shared memory parallel programming models, e.g., OpenMP [36] and Threading Building Blocks (TBB) [108], have been proposed to facilitate the development of parallel applications on shared memory multiprocessors. However, the above models have limitations in the forms of parallelism and the platforms they support.

To overcome the limitations of above models this dissertation introduces SpiceC for shared-memory multicore systems that is aimed at meeting the following demands:

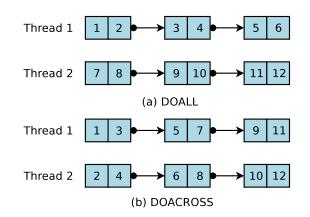

I. Different forms of parallelism. A shared memory programming model must support various forms of parallelisms for successfully handling a wide range of applications. DOALL parallelism can be easily expressed using existing shared memory parallel programming models. However, more forms of parallelism (such as DOACROSS and pipelining) are needed and even support for speculative parallelism is required to enable parallelization in the presence of cross-iteration dependences.

II. Different forms of multicore platforms. A shared memory programming model should support not only multicore processors with cache coherence but also manycore processors without cache coherence. Existing shared memory programming model only works for processors with cache coherence. However, as multiprocessors transition from multicores to manycores, the scalability of traditional cache coherence protocols becomes a problem. Intel Labs has created their new Tera-scale multiprocessor – "Single-chip Cloud Computer (SCC)" which is a 48-core processor without support for cache coherence. Other similar manycore processors may be created in the future.

This chapter presents a shared memory programming model, called SpiceC (*S*calable *p*arallelism via *i*mplicit *c*opying and *e*xplicit *C*ommit), which is the core of the SpiceC system. It is designed to satisfy the aforementioned demands. The chapter also describes the implementation of the SpiceC programming model, which consists of a source-to-source compiler and a runtime library.

#### 2.1 The Design of SpiceC

#### 2.1.1 The SpiceC Computation Model

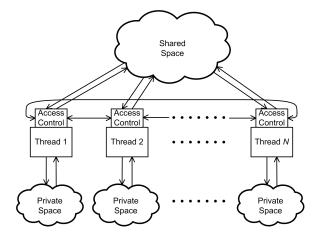

The SpiceC computation model represents a simple view of a parallel computation that serves as the basis for the programmer interface as well as corresponding implementation. In this model a parallel computation consists of multiple threads where each thread maintains a *private space* for data. In addition, a *shared space* is also maintained that holds shared data and provides a means for threads to communicate data to each other. A thread cannot access the private space belonging to other threads.

Figure 2.1: SpiceC Computation Model.

Each thread carries out its computation as follows: using *copying* operations it transfers data to its private space from shared space; it *operates* on the data in private space and produce results that are also written to the private space; and finally the thread affects the transfer of results to shared space using a **commit** operation thus allowing all threads to see the computed results. Thus, in this model, a thread performs its computation in *isolation* from other threads. Associated with each thread is an *access control* module which manages all accesses a thread makes to shared space. The access control modules of different threads perform actions on the shared space in coordination with each other.

A variable in shared space may be accessed by a thread by simply referring to it. A thread's first access to a shared space variable results in an image of that variable being created in its private space and this image is initialized by *copying* the value of the variable from shared space to private space. After copying, all subsequent accesses to the variable, including both read and write accesses, refer to the variable's image in the private space. In other words, the thread can manipulate the value of the variable in isolation, free of contention with other threads. Most importantly, the above semantics is enforced automatically by the implementation of SpiceC model – the programmer simply refers to the variable by its name without having to distinguish between first or subsequent accesses. Therefore the above copying is referred to as *implicit copying* as it is automatically performed without help from the programmer. There will be times when the private space of a thread space. The clearing of private space, like its setup through copying, is also *implicit.* The private space of a thread is cleared at program points that correspond to boundaries of *code regions* (e.g., iteration boundaries of parallel loops, boundaries separating pipeline stages, synchronization points).

When a thread has finished a block of computation and wishes to expose its results to other threads, it performs an *explicit commit* operation. This results in the transfer of variable's values from private space to shared space. The programmer is provided with an Application Programming Interface (API) using which he/she can specify points in the program where the values of variable's need to be committed to shared space. SpiceC supports two types of commit operations. The first type of commit operation simply copies all copied variables to the shared space after acquiring the write permission to the shared space. The second type of commit operation checks for *atomicity violation* before committing, that is, it checks to see if any of the copied variables was updated by another thread after being copied into the private space of the committing thread. An *atomic commit* enables programmers to express speculative computations with little effort.

#### 2.1.2 SpiceC Design Choices

This section briefly describes how the design of SpiceC addresses the following issues: programmability (i.e., reducing the burden of parallel programming), versatility (i.e., providing means to program different types of parallelism), and performance portability (i.e., programs deliver performance on different platforms without having to rewrite them).

1. Programmability. The complexity of parallel programming hinders developers from using it. To make programming easier, SpiceC uses programming style similar to OpenMP [36]. Developers do not write new parallel programs but simply add *SpiceC directives* into the text of a sequential program. Parallelism is exploited by the compiler based upon the directives. SpiceC model can be used to cause selected portions of the code to be executed in parallel while the remaining code remains serial.

To ensure that the programmer can easily reason about a program, a form of *sequential consistency* is employed as follows. In SpiceC, the *copy* and *commit* operations naturally divide code in parallel regions into chunks. These chunks can be executed with atomicity and in isolation as specified by developers. Sequential consistency is then enforced by the software at the coarse grain level of chunks. For performance, the compiler can freely reorder instructions within a chunk without the risk of violating coarse grain sequential consistency.

SpiceC removes the need to explicitly specify communication between threads. The work of *copying* and *commit* is done by the compiler and the implementation of supporting API functions. Developers only need to insert *commit* calls in their codes. This greatly reduces developer burden of programming explicit communication in a message-passing model such as Message Passing Interface (MPI). For example, in a message-passing model, developers need to write the following three functions to transfer a linked list from a thread to another: the first converting the linked list to a binary string, the second transferring the string to another thread, and the last for reconstructing the linked list from the string. In SpiceC, after a thread commits the linked list, other threads can access it as any other shared space variable. Developers do not need to write any special code to handle the linked list.

II. Versatility. To efficiently parallelize applications, SpiceC supports multiple forms of parallelism: DOALL, DOACROSS, pipelining, and speculative parallelism. It is difficult to use existing parallel programming model to implement some forms of parallelism while ensuring correctness and delivering high performance. For example, speculation must be expressed using low level primitives in existing languages [101]. Speculative computation, misspeculation check, and misspeculation recovery must be programmed by the user which can be a non-trivial programming exercise. In contrast, SpiceC supports high level primitives and developer only needs to specify the parallelism and the coarse-grained dependences in the program. Compilers and runtime systems take care of the tedious part of parallel code generation. SpiceC provides other benefits to parallel program developers. First, since a thread only updates variables in its private space before committing, it is easy to reverse the computation by simply discarding the content in the private space. In addition, the *commit* operation provided by SpiceC can check atomicity violation at runtime before committing. This makes it easy for developers to write programs with speculative parallelism. Secondly, parallel programming is error-prone. In SpiceC, an error in one thread does not affect other threads until it is committed. Therefore, it is easy to realize *fault tolerance* in SpiceC model. For example, developers can capture all fatal exceptions in thread T and reset Twhen exceptions happen. This enables other threads to continue operating even in the presence of errors in T.

III. Performance Portability. SpiceC can be implemented on any multicore or manycore system that has a logically shared memory with or without cache coherence. The portability of SpiceC makes it attractive alternative for developers who want their programs deployed on multiple platforms. Moreover, since current cache coherence protocols may not scale to manycore systems [11, 22], SpiceC makes it possible to scale shared-memory programs (e.g., OpenMP programs) to manycore systems.

#### 2.1.3 **Programming Interface**

SpiceC aims to provide a portable standard for writing parallel programs while hiding the complexity of parallel programming from developers. This section presents directives supported by SpiceC.

SpiceC compiler directives enable the programmer to mark and parallelize a section

| Directive                                         | Description                        |

|---------------------------------------------------|------------------------------------|

| #pragma SpiceC parallel [parallelism]             | specify a parallel region          |

| #pragma SpiceC region [name] [order]              | specify a subregion                |

| #pragma SpiceC commit [check_type] [order]        | perform commit operation           |

| #pragma SpiceC barrier [for_variable (variables)] | clear variables from private space |

Table 2.1: Compiler directives implemented by SpiceC

of code that is meant to be run in parallel just as is the case in OpenMP [36]. A compiler directive in C/C++ is called a pragma (pragmatic information). Compiler directives specific to SpiceC model in C/C++ start with **#pragma SpiceC**. Table 2.1 shows the compiler directives supported by SpiceC.

- #pragma SpiceC parallel is used to specify the parallel region of the program. The parallel region must be a loop, written in for, while, or do ... while form. Developers must specify in what form of parallelism the parallel region is to be executed. SpiceC supports three types of parallelism: DOALL, DOACROSS, and pipelining.

- **#pragma SpiceC region** is used to specify a subregion in the parallel region. Developers can assign a name to the subregion and specify the execution order of different instances of the subregion or different subregions. By default, the whole loop body of the parallel region is one subregion.

- #pragma SpiceC commit is used to call the commit operation, which commits all variables that are updated in the subregion to the shared space. Developers can specify whether to perform *atomicity* check before the commit operation. If the atomicity check fails, the subregion is re-executed. Developers can also specify the execution order of the commit operation which can be used to enforce the sequential semantics the parallel

region. By default, a commit operation is placed at each exit of a subregion if no explicit commit is specified.

**#pragma SpiceC barrier** is used to insert a barrier in the parallel region. In the SpiceC model, each thread clears its private space when it encounters a barrier. Developers can optionally specify which variables to clear to enable avoidance of unnecessary copying overhead.

The following sections illustrate the use of directives in marking code regions and expressing different forms of parallelism. A few examples written in SpiceC are presented to show how different forms of parallelism can be expressed with little effort by the programmer.

#### 2.1.4 Data Transfers in SpiceC

Figure 2.2 shows an example of explicit parallel code written in SpiceC that illustrates how shared space may be used by threads to communicate values to each other. The parallel code is executed by two threads. It is divided into two phases. In the first phase the two threads calculate values of variables a and b respectively. The programmer does not specify that a and b are to be copied into the private spaces – they are automatically copied upon their first uses. At the end of the first phase, a and b need to be committed into the shared space so that their new values are accessible to other threads. The programmer need not identify a and b in the commit operation – this is handled automatically which makes it easy to use. In other words, developer only specifies "when" to commit but need not specify "what" to commit. At the barrier, the two threads clear variable a and b in

```

#pragma SpiceC parallel {

int tid = spicec_get_thread_id();

if (tid == 0)

a = calculate_a();

else

b = calculate_b();

#pragma SpiceC commit

#pragma SpiceC barrier for_variable(a,b)

if (tid == 0)

c = calculate_c(a,b);

else

d = calculate_d(a,b);

}

```

Figure 2.2: Communicating parallel threads written in SpiceC.

their private spaces and wait for each other. When both threads reach the synchronization point, they continue their computation and copy the value of a and b from the shared space again when they are used. Developers may or may not specify which variables to clear at the barrier. If variables are not specified at the barrier, the entire private space is cleared.

#### 2.1.5 Non-speculative Parallelism

```

#pragma SpiceC parallel doall {

for(i=0;i<nodes;i++)

nodes[i].cluster = closest_cluster(nodes[i], clusters);

#pragma SpiceC commit

} //implicit barrier

#pragma SpiceC parallel doall {

for(i=0;i<clusters;i++)

clusters[i].mean = calculate_mean(clusters[i], nodes);

#pragma SpiceC commit

}</pre>

```

Figure 2.3: K-means clustering algorithm written in SpiceC.

I. DOALL Parallelism in SpiceC. Figure 2.3 shows a K-means clustering program written in SpiceC. This program looks very similar to an OpenMP program. Without the directives, the program can still be compiled as a sequential program. The K-means clustering algorithm has two steps: the first step assigns each node to the cluster with the closest mean and the second step calculates the new means to be the centroid of the nodes for each cluster. Each step is parallelized using DOALL parallelism. Commit operations are inserted at the end of each parallel region. By using DOALL, workloads are divided and assigned among the threads at the beginning of the parallel region. No execution order is specified in this example. Therefore each thread executes fully in parallel with other threads. All threads join at the end of the parallel region, which acts as a implicit barrier.

II. DOACROSS Parallelism in SpiceC. Figure 2.4 shows a typical stream decoding program written in SpiceC model. The program repeatedly does the three steps: read a stream from the input buffer, decode the stream, and write the stream back to the output buffer. There are two cross-iteration dependences in the loop. In each iteration, the read\_stream function reads a stream from the input buffer and moves the input buffer pointer to the next stream. Therefore, the read\_stream in the current iteration dependence on itself in the previous iteration. Similarly, write\_stream also has cross-iteration dependence on itself. To parallelize this program, the loop is annotated with DOACROSS parallelism. By using DOACROSS, consecutive iterations are assigned to different threads to allow them to be executed in parallel. The loop is divided into three subregions with each step forming one subregion. Subregion R1/R3 in the current iteration is specified to only be executed after R1/R3 in the previous iteration finishes. The keyword "ITER" used in the SpiceC pragmas refers to the current iteration and "ITER-1" refers to the preceding iteration. No execution

```

#pragma SpiceC parallel doacross {

for(i=0;i<n;i++) {

#pragma SpiceC region R1 order_after(ITER-1, R1)

{

job = read_stream(input_buffer);

#pragma SpiceC commit

}

\#pragma SpiceC region R2 no_order

{

decode(job);

#pragma SpiceC commit

}

#pragma SpiceC region R3 order_after(ITER-1, R3)

{

write_stream(output_buffer, job);

#pragma SpiceC commit

}

}

}

```

Figure 2.4: A typical stream decoder written in SpiceC.

order is specified for R2 since it does not have cross-iteration dependence.

III. Pipelined Parallelism in SpiceC. Figure 2.5 shows the same stream decoder as shown in Figure 2.4. But in this example, it is parallelized using pipelined parallelism. The loop body is still divided into three subregions. Each subregion is a stage of the pipeline. By using pipelining, each subregion is executed in one thread, similar to Decoupled Software Pipelining [106]. In this program, the subregion R2 needs data from R1 and R3 needs data from R2. Therefore, R2 is specified to be executed after R1 and R3 after R2. In this case, it is not necessary to specify the cross-iteration execution order (e.g., R1 in the current iteration should be executed after R1 in the previous iteration) since it is ensured by the very nature of pipelining. Unlike the model of producer and consumer, SpiceC model commits data to the same place every time. Therefore, subsequent commit may overwrite the value from previous commit. To avoid this problem, the scalar variable job is expanded into an array and make each iteration compute using different memory locations.

#### 2.1.6 Speculative Parallelism

SpiceC also supports speculative parallelization for exploiting parallelism between code regions that occasionally involve dependences although mostly they can be safely executed in parallel. With the SpiceC programming model, speculation can be easily applied to all forms of parallelism described in the preceding section. Users just need to add an atomicity\_check clause if the regions are being speculatively executed in parallel.

Figure 2.6 shows an example of using speculation in context of a DOACROSS loop. The code in the example is the kernel of benchmark telecomm-CRC32 in MiBench

```

#pragma SpiceC parallel pipelining {

for(i=0;i<n;i++) {

\#pragma SpiceC region R1 {

job[i] = read\_stream(input\_buffer);

#pragma SpiceC commit

}

#pragma SpiceC region R2 order_after(ITER, R1) {

decode(job[i]);

\# {\rm pragma} SpiceC commit

}

#pragma SpiceC region R3 order_after(ITER, R2) {

write_stream(output_buffer, job[i]);

\#pragma SpiceC commit

}

}

}

```

Figure 2.5: Stream decoder parallelized using pipelining parallelism.

```

error=0;

i = 0;

#pragma SpiceC parallel doacross {

while(i<n) {

#pragma SpiceC region R1 order_after(ITER-1, R1) {

string = read_file(file[i++]);