# FREQUENT VALUE LOCALITY AND ITS APPLICATIONS TO ENERGY EFFICIENT MEMORY DESIGN

by Jun Yang

A Dissertation Submitted to the Faculty of the DEPARTMENT OF COMPUTER SCIENCE

In Partial Fulfillment of the Requirements

For the Degree of

DOCTOR OF PHILOSOPHY

In the Graduate College

THE UNIVERSITY OF ARIZONA

Get the official approval page from the Graduate College before your final defense.

#### STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at The University of Arizona and is deposited in the University Library to be made available to borrowers under rules of the Library.

Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgment of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the head of the major department or the Dean of the Graduate College when in his or her judgment the proposed use of the material is in the interests of scholarship. In all other instances, however, permission must be obtained from the author.

| SIGNED: |  |  |

|---------|--|--|

| DIGNED. |  |  |

## ACKNOWLEDGEMENTS

I want to express my gratefulness to my adviser, Professor Rajiv Gupta. He is such a rare researcher who pursues his goal constantly and tirelessly. As a student, I am indebted most to his hard-to-find spirit. During the development of this dissertation, Professor Gupta provided me unlimited help and guidance. He has led me through the darkness and pointed me at the right direction to keep me away from confusion. And he is always there to help, no matter how far he goes and how long he goes. Without those, I would never complete this thesis on time. I gained precious experience from him which I could never get anywhere else.

I also wish to give my deepest appreciation to the care, support, encouragement and love from my mother and father. They have taught me how to live a life with difficulties, how to face ups and downs, how to make decisions and how to stay up with happiness. They are my lifetime teachers. I am thankful to them for giving me their knowledge, wisdom and their love.

Thanks also go to Professor Richard Snodgrass and Professor Christian Collberg. They have provided me scientific discussions and comments that helped me develop a refined manuscript. I also appreciate all those who helped answer my questions, who reviewed my papers and provided insightful comments. You helped me conduct better research during the development of this dissertation.

Last but not least, I want to thank my husband Youtao Zhang for also being my career mate. He has impacted me in many ways including the time management and the creativeness in conducting research. It is always pleasant to discuss difficult problems with him during late nights when both of us enjoy staying in our office. I wish him continuous success in his professional career.

To my dear mother Dekun Sun, my dear father Hongsheng Yang and my dear husband Youtao Zhang

# Table of Contents

| List of | FIGURES                                              | 9  |

|---------|------------------------------------------------------|----|

| List o  | Tables                                               | 12 |

| Abstr   | ACT                                                  | 13 |

| Снарт   | ER 1. Introduction                                   | 15 |

| 1.1.    | Motivation for Low Power Processor Design            | 15 |

| 1.2.    |                                                      | 19 |

| 1.3.    | Thesis Organization                                  | 21 |

| Снарт   | ER 2. Background and Related Work                    | 23 |

| 2.1.    | Circuit and Logic Level Techniques                   | 23 |

| 2.2.    | Architecture Level Techniques                        | 26 |

|         | 2.2.1. Low Power Designs for Processor Core          | 27 |

|         | 2.2.2. Energy Efficient Cache Designs                | 28 |

|         | 2.2.3. Bus Encoding Techniques                       | 30 |

|         | 2.2.4. Computation Reuse                             | 32 |

| 2.3.    | Simulation Tools                                     | 33 |

| 2.4.    | Energy Measurement Metrics                           | 36 |

| Снарт   | ER 3. Frequent Value Phenomenon                      | 37 |

| 3.1.    | Characteristics of Frequent Values                   | 37 |

|         | 3.1.1. Property I: Frequent Value Occurrences        | 38 |

|         | 3.1.2. Property II: Frequent Value Stability         | 41 |

|         | 3.1.3. Property III: Frequent Value Distribution     | 44 |

| 3.2.    | Frequent Value Locality vs. Value Locality           | 44 |

| 3.3.    | Summary                                              | 47 |

| Снарт   | ER 4. Identifying Frequent Values                    | 48 |

| 4.1.    | Frequent Value Identification Introduction           | 48 |

| 4.2.    | Software Method – Find once for a given program      | 51 |

| 4.3.    | Hardware Method I – Find once per run of the program | 55 |

| 4.4.    | Hardware Method II – Adaptive FV Finder              | 61 |

| 4.5.    | Summary                                              | 65 |

# Table of Contents—Continued

| Снарт  | ER 5.  | The Frequent Value Data Cache Design                                                     | 66                |

|--------|--------|------------------------------------------------------------------------------------------|-------------------|

| 5.1.   | FV Ca  | ache Overview                                                                            | 67                |

|        | 5.1.1. | Accessing the FVC                                                                        | 69                |

|        | 5.1.2. | The FVC design                                                                           | 70                |

| 5.2.   |        | Access Time                                                                              | 73                |

| 5.3.   |        | Dynamic Energy Model                                                                     | 76                |

|        | 5.3.1. | Per access energy                                                                        | 76                |

|        | 5.3.2. | Total Cache Energy                                                                       | 79                |

| 5.4.   | Findin | ng Frequent Values for FVC                                                               | 82                |

|        | 5.4.1. | The Design                                                                               | 83                |

|        | 5.4.2. | Combining with the Encoder                                                               | 84                |

|        | 5.4.3. | Study of Monitoring Time                                                                 | 84                |

| 5.5.   | Exper  | iments                                                                                   | 89                |

|        | 5.5.1. | Experimental Setup                                                                       | 89                |

|        | 5.5.2. | Experimental Results                                                                     | 90                |

| 5.6.   | Summ   | ary                                                                                      | 97                |

| CHARM  | DD 6   | Engagement Value Date Due Engading Cohomes                                               | 98                |

| CHAPT: |        | Frequent Value Data Bus Encoding Scheme                                                  | 96<br>99          |

| 0.1.   | г v Da | ata Bus Encoding                                                                         | 100               |

|        | 6.1.1. | 0                                                                                        | $100 \\ 102$      |

|        | 6.1.2. | Keeping Encoder and Decoder FV Tables Consistent Enhancements of Base FV Encoding Scheme | $10^{2}$ $10^{2}$ |

|        | 6.1.4. | Experiments                                                                              | 102               |

| 6.2.   |        | ing Coder Overhead                                                                       | 112               |

| 0.2.   | 6.2.1. | Reducing Access to the Coder                                                             | 112               |

|        | 6.2.1. | Reducing Coder Updating Activity                                                         | 114               |

|        | 6.2.2. | Reducing Coder Size                                                                      | 114               |

| 6.3.   |        | acy of Frequent Value Identification in Encoder                                          | 117               |

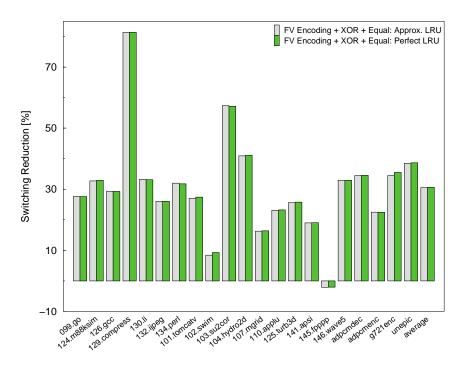

| 0.5.   | 6.3.1. | Approximate LRU versus perfect LRU replacement                                           | 117               |

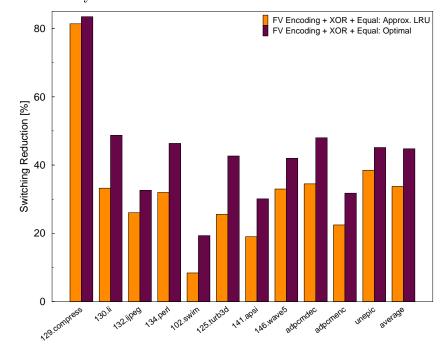

|        | 6.3.2. |                                                                                          | 118               |

| 6.4    |        | arisons with Other Techniques                                                            | 120               |

|        |        | ary                                                                                      |                   |

| 0.5.   | Summ   | .cary                                                                                    | 12(               |

| Снарт  | ER 7.  | Computation Reuse                                                                        | <b>12</b> 4       |

| 7.1.   | Load a | and Store Reuse Study                                                                    | 126               |

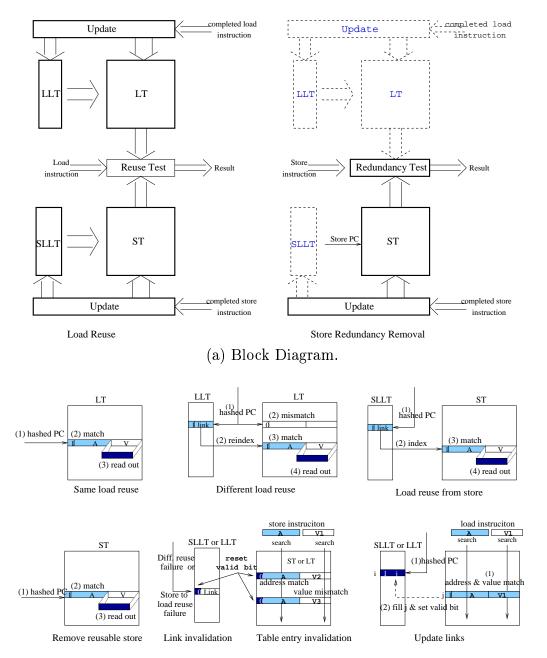

|        | 7.1.1. | Types of Load and Store Reuse Opportunities                                              | 127               |

|        | 7.1.2. | An Aggressive Reuse Mechanism                                                            | 128               |

|        | 7.1.3. | Amounts of Load and Store Reuse of Different Types                                       | 128               |

|        | 7.1.4. | History Table Sizes and Linking Parameters                                               | 131               |

| 7.2.   | Reuse  | Hardware and Update Algorithms                                                           | 132               |

## Table of Contents—Continued

|       | 7.2.1. | The RU Structure                                   | 132 |

|-------|--------|----------------------------------------------------|-----|

|       |        | Reuse Procedure                                    |     |

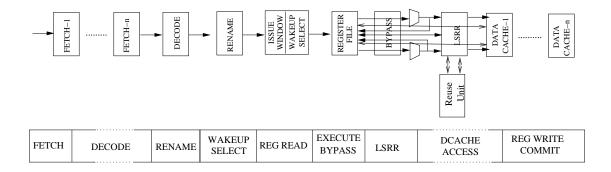

|       |        | Integration into Superscalar Pipeline              |     |

| 7.3.  | Perfor | mance Evaluation                                   | 138 |

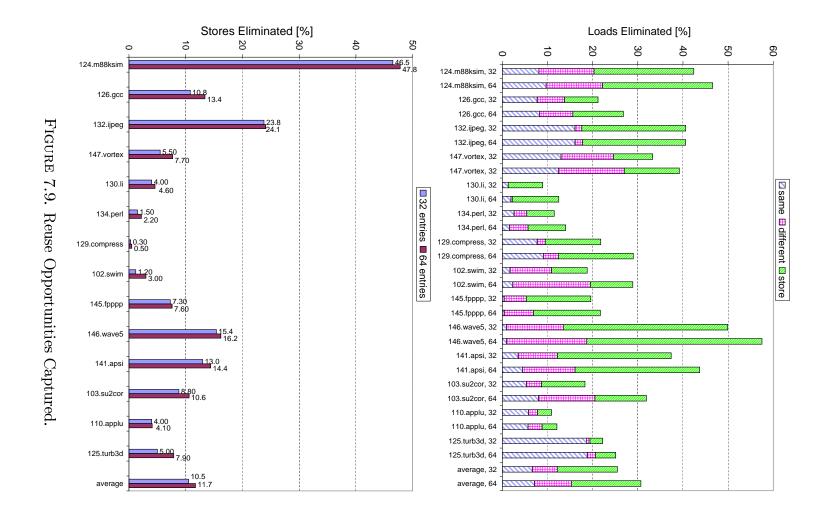

|       | 7.3.1. | Loads and Stores Reused                            | 139 |

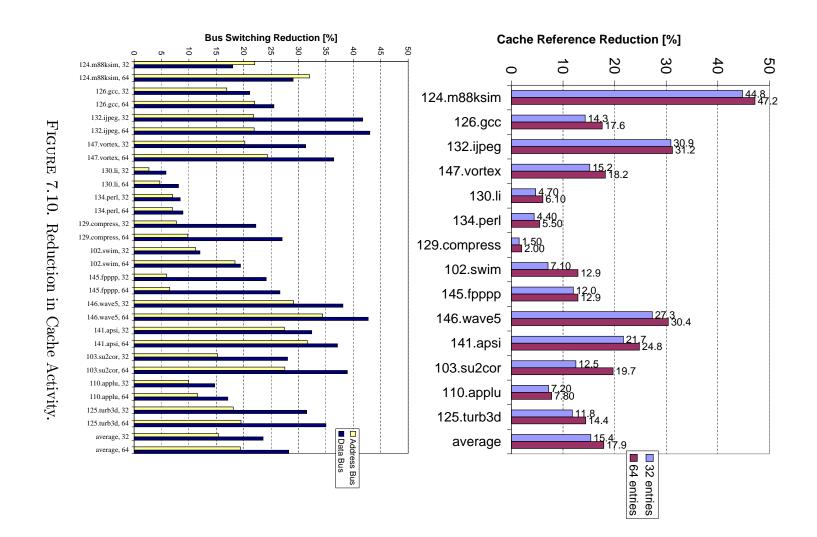

|       | 7.3.2. | Cache Activity Reduction                           | 140 |

|       | 7.3.3. | Energy Savings                                     | 140 |

|       | 7.3.4. | IPC Improvements                                   | 144 |

| 7.4.  | Summ   | ary                                                | 145 |

| Снарт | ER 8.  | Conclusion                                         | 147 |

| 8.1.  | Disser | tation Contributions                               | 147 |

| 8.2.  | A Vie  | w to the Practicability of the Proposed Techniques | 149 |

| 8.3.  | Future | Directions for Research                            | 152 |

| Рынын | ENGEG  |                                                    | 15/ |

# LIST OF FIGURES

| FIGURE 1.1.<br>FIGURE 1.2.<br>FIGURE 1.3.                                              | Power Distribution for Alpha 21264                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 2.1.<br>associat<br>FIGURE 2.2.<br>FIGURE 2.3.<br>FIGURE 2.4.                   | The structure of a general cache (derived from the standard setive cache structure [29])                                                                                                                                                                                                 |

| FIGURE 3.1.<br>FIGURE 3.2.<br>FIGURE 3.3.<br>FIGURE 3.4.<br>FIGURE 3.5.<br>FIGURE 3.6. | Amount of memory occupied by top 8 frequent values Amount of memory occupied by small vs. big values Stability of frequent values over program execution Distribution of frequent values across memory (heap and stack). Distribution of frequent values across memory (heap and stack). |

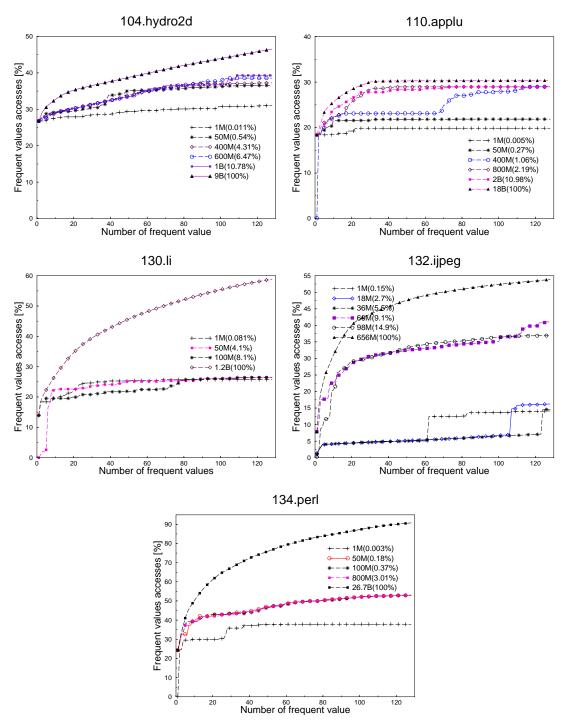

| feedbacl                                                                               | Access percentage attributed to top 128 frequent values Finding frequent values in profiling run using training inputs for ater execution runs. The training inputs are designed to generate k data in the Spec benchmarks                                                               |

| FIGURE 4.3. runs FIGURE 4.4.                                                           | Finding frequent values in profiling run for use in later execution  Value table entry                                                                                                                                                                                                   |

| FIGURE 4.5.                                                                            | Algorithm for finding the frequent values using the value table.                                                                                                                                                                                                                         |

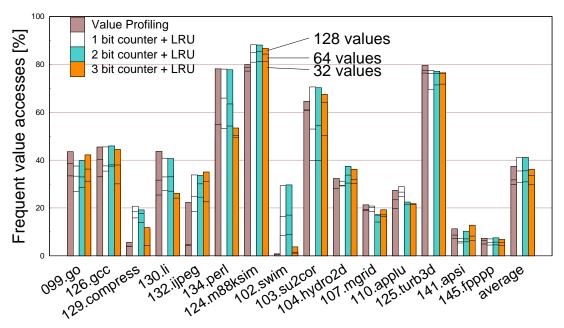

| FIGURE 4.6.                                                                            | Comparison of value profiling technique and the proposed hard-<br>ethod for capturing 32, 64 and 128 frequent values                                                                                                                                                                     |

| FIGURE 4.7.                                                                            | Finding and using frequent values in each execution run                                                                                                                                                                                                                                  |

| FIGURE 4.8.                                                                            | Finding and using frequent values in each execution run                                                                                                                                                                                                                                  |

| FIGURE 4.9.                                                                            | LRU algorithm for the adaptive frequent value finder                                                                                                                                                                                                                                     |

|                                                                                        | Inserting new values. Assume a 3-bit timestamp and 1 reference                                                                                                                                                                                                                           |

|                                                                                        | Example of frequent value identification                                                                                                                                                                                                                                                 |

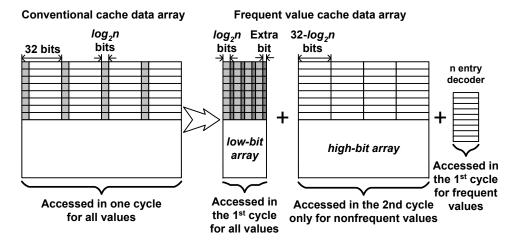

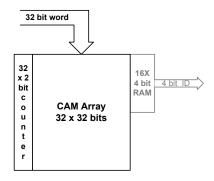

| (bpw),<br>and 32 -<br>original                                                         | An example of partitioning the data array of 32 bits per word 4 words per line (wpl) into two arrays of $log_2n + 1$ bpw, 4 wpl $-log_2n$ bpw, 4 wpl each. The n-entry decoder is used to store the frequent values                                                                      |

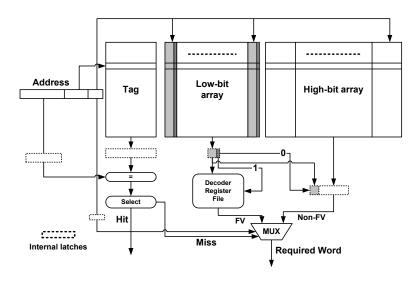

| FIGURE 5.2.                                                                            | The FVC design                                                                                                                                                                                                                                                                           |

# List of Figures—Continued

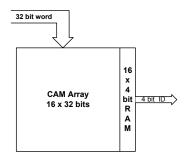

| FIGURE               | 5.3.   | 16 Value FV CAM                                                | 71  |

|----------------------|--------|----------------------------------------------------------------|-----|

| FIGURE               | 5.4.   | Read access operation                                          | 74  |

| FIGURE               | 5.5.   | % energy savings for frequent value accesses                   | 80  |

| FIGURE               | 5.6.   | Total energy consumed by FVC                                   | 81  |

| FIGURE               | 5.7.   | FV finder entry.                                               | 83  |

| FIGURE               | 5.8.   | 32 entry FV finder and 16 FV encoder                           | 83  |

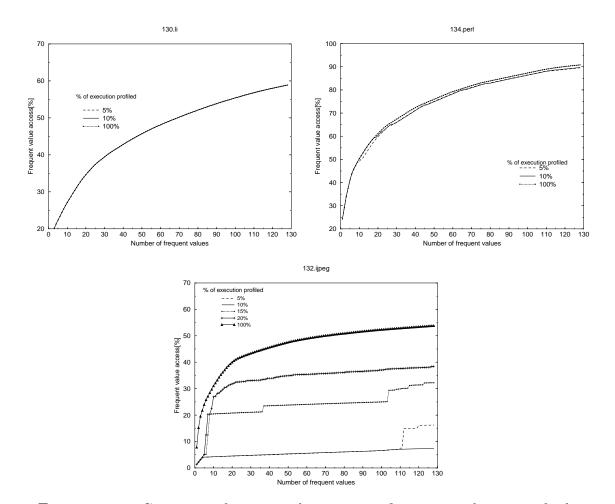

| FIGURE               | 5.9.   | Comparing frequent value set identified by the FV finder with  |     |

| an                   | ideal  | set                                                            | 86  |

|                      |        | Comparing frequent value set identified by the FV finder with  |     |

| an                   | ideal  | set                                                            | 87  |

| FIGURE               | 5.11.  | Comparing frequent value set identified using software method. | 88  |

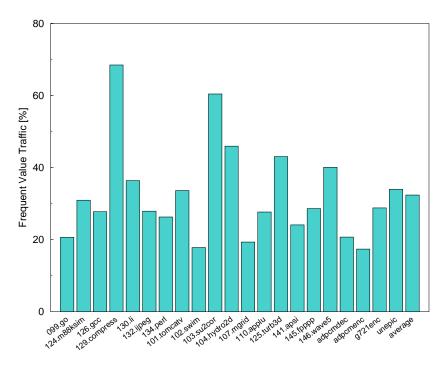

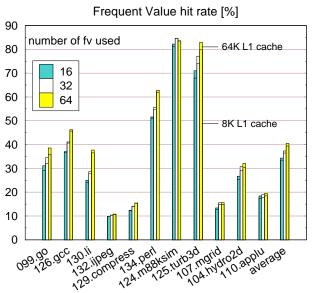

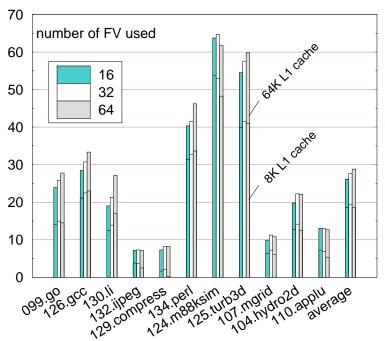

| FIGURE               | 5.12.  | Cache hits that are FV over the $95\%$ cache accesses          | 91  |

| FIGURE               | 5.13.  | Cache Energy Reduction                                         | 92  |

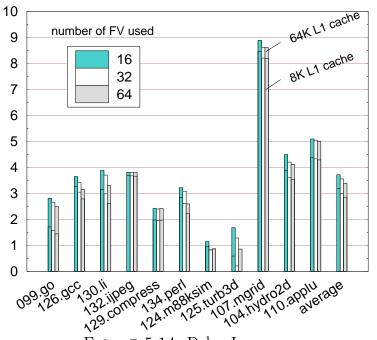

| FIGURE               | 5.14.  | Delay Increase                                                 | 93  |

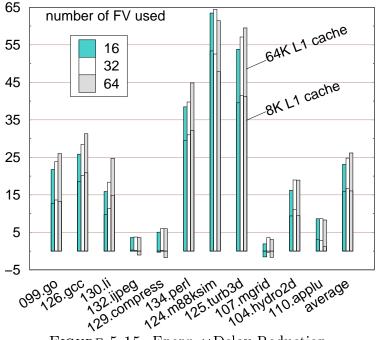

| FIGURE               | 5.15.  | Energy×Delay Reduction                                         | 93  |

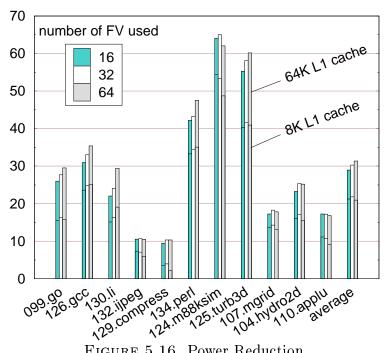

| FIGURE               | 5.16.  | Power Reduction                                                | 94  |

| FIGURE               | 5.17.  | Load marking                                                   | 96  |

| FIGURE               | 5.18.  | Effects of load-marking on delay                               | 97  |

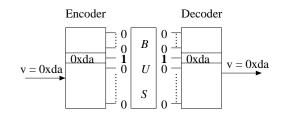

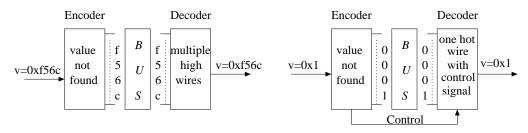

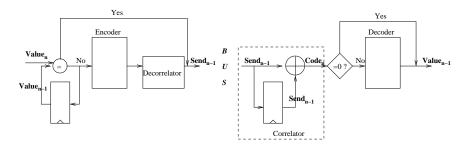

| FIGURE               | 6.1.   | Encoding-decoding setup                                        | 101 |

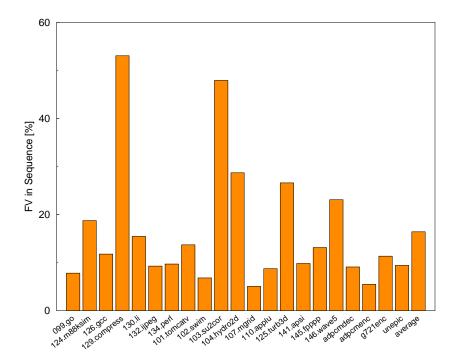

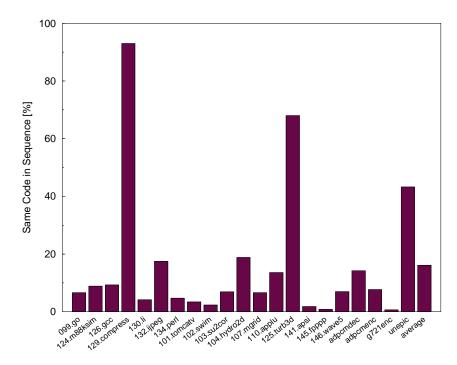

| FIGURE               | 6.2.   | Occurrence of frequent values in sequence                      | 103 |

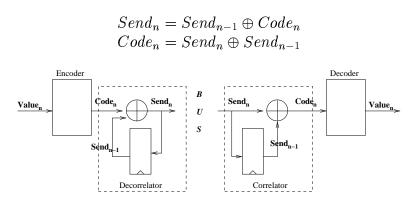

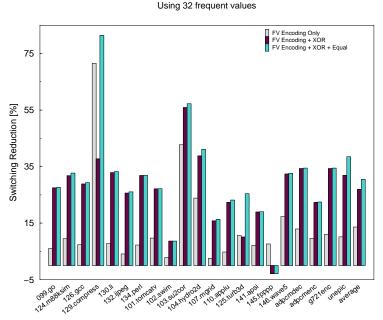

| FIGURE               | 6.3.   | Reducing switching by XORing values                            | 104 |

| FIGURE               | 6.4.   | Transmission of identical code in sequence                     | 105 |

| FIGURE               | 6.5.   | Dealing with equal code transfer.                              | 105 |

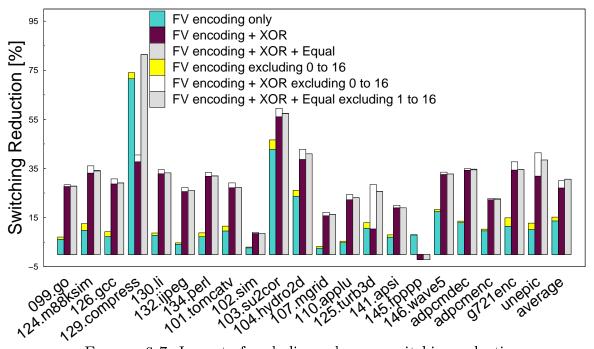

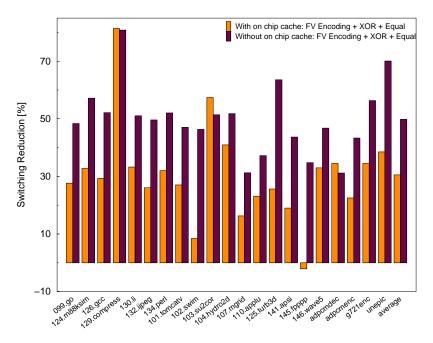

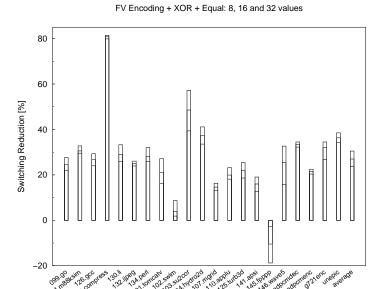

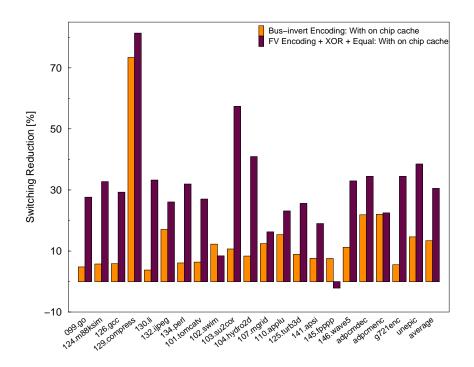

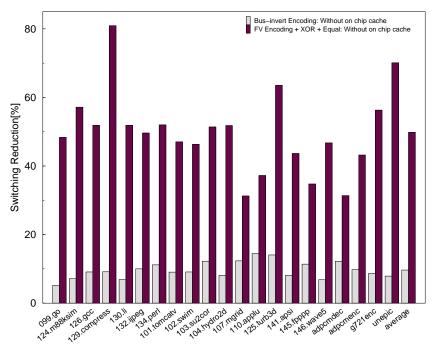

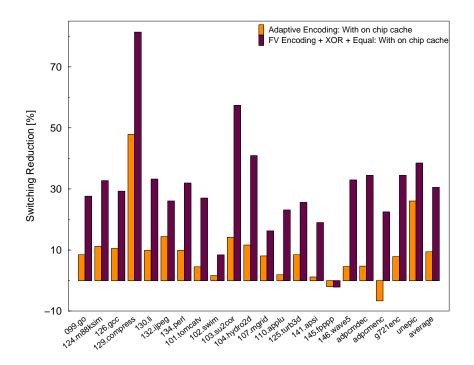

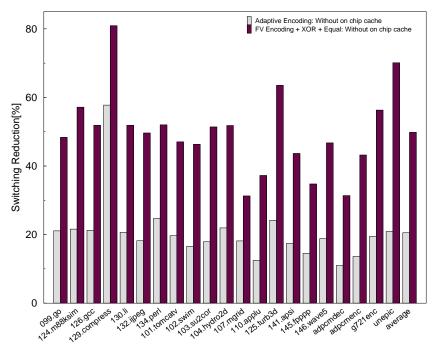

| FIGURE               | 6.6.   | Effectiveness of FV encoding and its enhancements              | 109 |

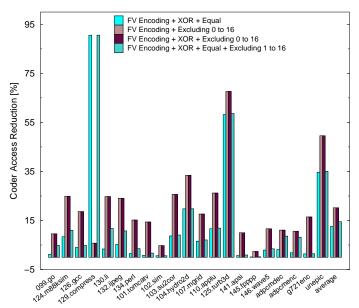

| FIGURE               | 6.7.   | Impact of excluding values on switching reduction              | 111 |

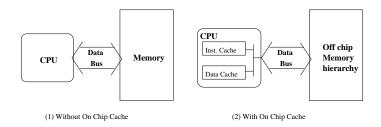

| FIGURE               | 6.8.   | Architecture models with and without on-chip caches            | 111 |

| FIGURE               | 6.9.   | FV encoding performance with on-chip cache versus without on-  |     |

| $\operatorname{chi}$ | p cacl | he                                                             | 112 |

| FIGURE               | 6.10.  | Impact of excluding values on encoding/decoding operations     | 113 |

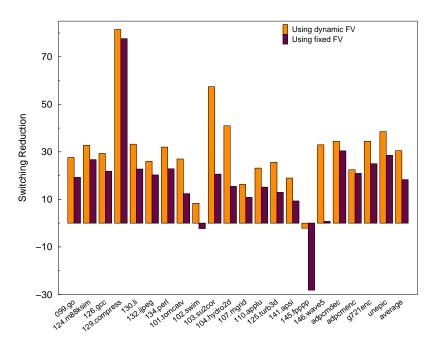

| FIGURE               | 6.11.  | Dynamic frequent values versus fixed frequent values           | 115 |

| FIGURE               | 6.12.  | Varying number of frequent values                              | 116 |

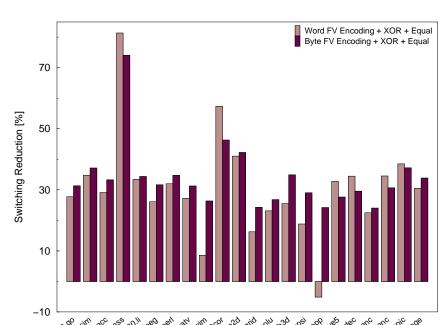

| FIGURE               | 6.13.  | Byte level frequent value encoding                             | 117 |

| FIGURE               | 6.14.  | Comparison with perfect LRU                                    | 118 |

| FIGURE               | 6.15.  | Comparison with optimal replacement policy                     | 119 |

| FIGURE               | 6.16.  | Bus-invert versus enhanced FV encoding                         | 121 |

| FIGURE               | 6.17.  | FV versus adaptive encoding                                    | 122 |

| FIGURE               | 7.1.   | Classification of Load and Store Reuse                         | 127 |

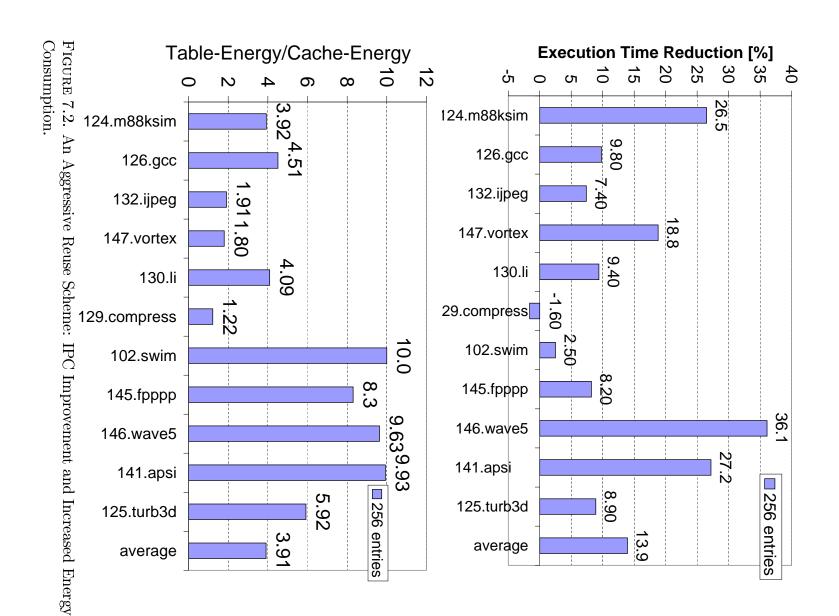

| FIGURE               | 7.2.   | An Aggressive Reuse Scheme: IPC Improvement and Increased      |     |

| $\operatorname{En}$  | ergy ( | Consumption                                                    | 129 |

# List of Figures—Continued

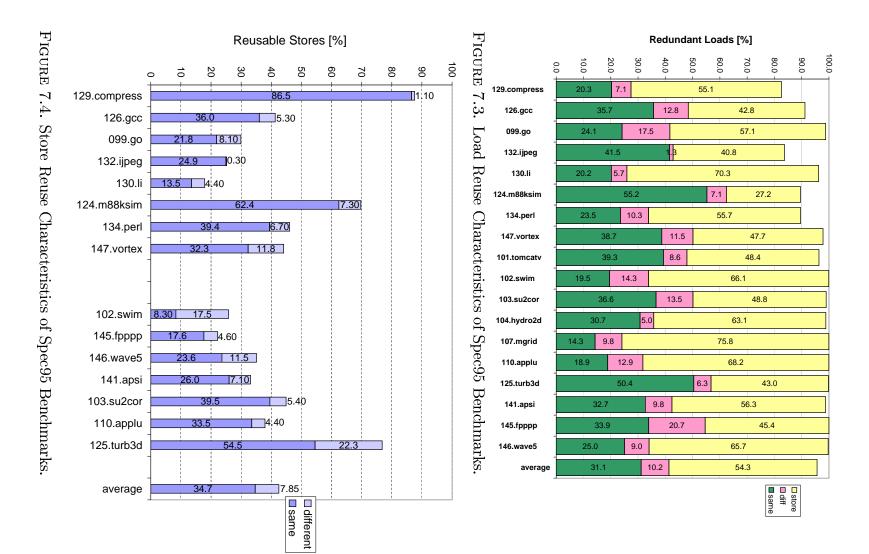

| FIGURE 7.3.         | Load Reuse Characteristics of Spec95 Benchmarks            | 130 |

|---------------------|------------------------------------------------------------|-----|

| FIGURE 7.4.         | Store Reuse Characteristics of Spec95 Benchmarks           | 130 |

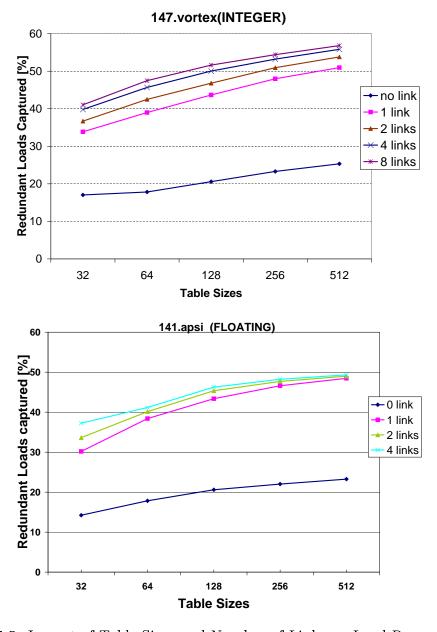

| FIGURE 7.5.         | Impact of Table Sizes and Number of Links on Load Reuse    | 133 |

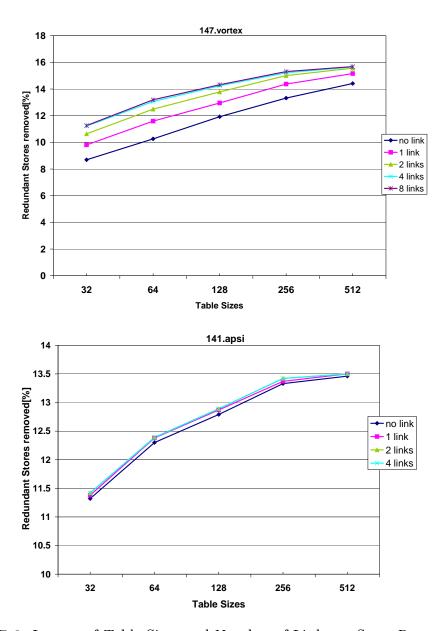

| FIGURE 7.6.         | Impact of Table Sizes and Number of Links on Store Reuse   | 134 |

| FIGURE 7.7.         | The Reuse Unit (RU)                                        | 135 |

| FIGURE 7.8.         | Superscalar Processor with Reuse Hardware                  | 138 |

| FIGURE 7.9.         | Reuse Opportunities Captured                               | 141 |

| FIGURE 7.10.        | Reduction in Cache Activity                                | 142 |

| FIGURE 7.11.        | Energy Figures: (a) Cache Savings; (b) Reuse Hardware Con- |     |

| $\mathbf{sumption}$ | n                                                          | 143 |

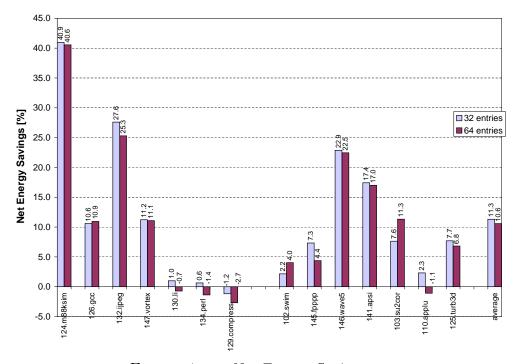

| FIGURE 7.12.        | Net Energy Savings                                         | 144 |

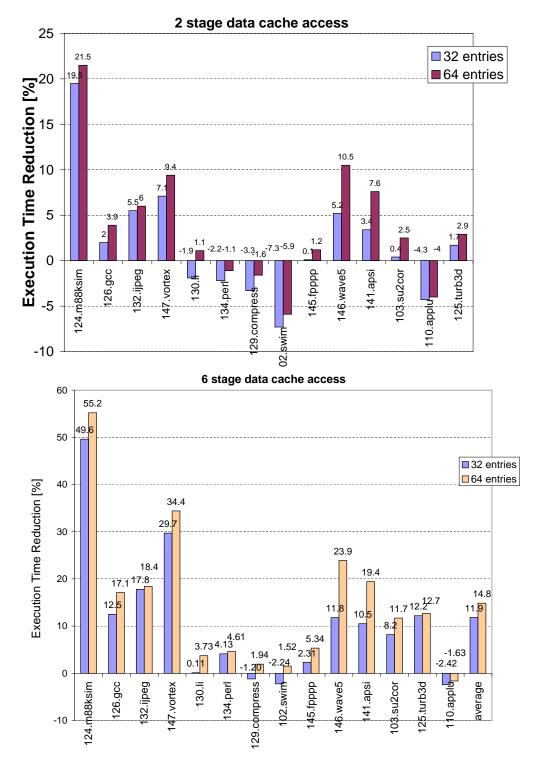

| FIGURE 7.13.        | IPC Improvements for Varying Cache Latencies               | 146 |

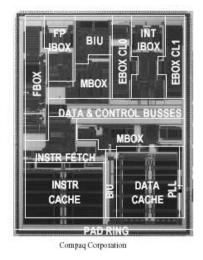

| FIGURE 8.1.         | Alpha 21264 Die Photo and Floorplan                        | 150 |

# LIST OF TABLES

|                                  | Power Trends for Compaq Alpha                                                                                                                                                                       | 15<br>16                   |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| TABLE 3.1.                       | Frequently occurring values ordered by decreasing frequency                                                                                                                                         | 39                         |

| TABLE 5.2. TABLE 5.3. TABLE 5.4. | Finding configurations with 1-cyle frequent value access and decode. Per access energy model(1)                                                                                                     | 75<br>78<br>78<br>78<br>90 |

| FV en                            | An example illustrating reduction in switching transitions using coding. The value stream in the first table contains two frequent 0xff and 0xfff whose one-hot codes are 0x1 and 0x2 respectively. | 107                        |

"Power, not manufacturability, is the challenge we face. Our industry needs to rise to the occasion and deliver innovative solutions that break through the power wall so we continue to deliver value to end users."

— Pat Gelsinge Chief Technology Office, Intel

## ABSTRACT

The need in low power processor design is growing due to the reliability problem for high frequency, high temperature processor chips and the expanding market for battery powered mobile devices. The memory hierarchy is a known source of significant power consumption. This dissertation develops low power techniques for two parts in the memory hierarchy, namely the data cache and the off-chip data bus. The proposed techniques are based on new observations of the memory residing frequent values.

The study on memory values shows that a small set of frequent values occupy a substantial fraction of memory spaces allocated to an executing program. Those values remain fairly stable over a program run. Moreover, the frequent values are distributed in the memory quite uniformly and periodically. Techniques in identifying the set of frequent values through software method and hardware methods are developed. Those techniques are adopted in the low power applications for the data cache and data bus.

A conventional data cache is redesigned into frequent value cache (FVC) so that power consumption is reduced for every access of frequent values. However, this comes with a cost of extra cycles for nonfrequent value accesses. To overcome the loss in speed, a load marking technique is developed so that for a substantial number of nonfrequent value accesses there is no degradation in speed. Experimental results of the FVC design show an energy reduction of 28.8% in L1 data cache is achieved.

On the off-chip data bus, an FV encoding technique is developed exploring frequent values. The encoding scheme reduces the total bus switching by using "one-hot" codes for frequent values. Variations of the FV encoding technique are also designed to achieve maximum switching reduction across different configurations and different benchmarks. The FV encoding technique can reduce the total number of bus switch-

ing counts 1.5 to 4 times more than that is achieved by other data bus encoding schemes.

In addition to the frequent value based cache design, a *cache access limiting* mechanism is developed to achieve low power from a different angle. A subset of cache accesses is removed by *reusing* their results in history. The reuse hardware is fine tuned to keep the overhead minimum while achieving low power in the data cache. The reuse hardware for the data cache can achieve 11% net cache energy saving.

# Chapter 1 Introduction

# 1.1 Motivation for Low Power Processor Design

Recently, power consumption has become one of the biggest challenges in high-performance desktop systems. This is because the drive toward increasing levels of performance has pushed clock frequencies higher and has increased the processor complexity. Both increases come at a cost of high power consumption. The costs associated with packaging, cooling and power delivery have thus jumped to the forefront in the microprocessor industry.

To get an idea of the trends in power consumption of today's processor consider the following table taken from the power study on Alpha processors [65]. The Alpha processor family is multi-issue, out-of-order execution high performance processor. We can see clearly the drastic growth of the power and its density as well. This increase would also negatively impact the processor reliability if the power dissipation keeps increasing at this rate. Even though reducing the supply voltage is well known as an efficient way of controlling power consumption, its benefits are more than offset by the increased complexity and frequency. This calls for creative architecture solutions that can focus on high level trade offs between power and performance.

| Alpha Model | Power(W) | Frequency(MHz) | Die size $(mm^2)$ | Voltage(V) |

|-------------|----------|----------------|-------------------|------------|

| 21064       | 30       | 200            | 234               | 3.3        |

| 21164       | 50       | 300            | 299               | 3.3        |

| 21264       | 90       | 575            | 314               | 2.2        |

| 21364       | >100     | >1000          | 340               | 1.5        |

Table 1.1. Power Trends for Compaq Alpha

The need to limit the power consumption is also crucial for portable computer platforms such as cellular phones, palm handhelds and pocket PCs because those devices are battery powered. Given the type of applications being written for mobile devices, there is an increasing demand for delivering high quality multimedia output. Since the advances in battery technology are limited, designing low power processors that can operate with a light weight battery for long duration is imperative. Table 1.2 shows the trends in power consumption for typical embedded processors: ARM7 to ARM10 [3]. They are simpler designed in-order execution pipelined processors. We can see from the table that the range of power consumption is only the order of MilliWatt. The reason for this big difference is due to much simpler architecture design. Future embedded processors will have more complex structure such as deeper pipeline length and branch prediction. The designs will resemble high performance processors but under different constraints. Therefore, limiting the power consumption is also becoming more and more important for embedded processors.

| ARM Model | Power(mW/MHz) | Frequency(MHz) | Die size $(mm^2)$ | Voltage(V) |

|-----------|---------------|----------------|-------------------|------------|

| ARM720T   | 0.2           | <100           | 1.8               | 0.9        |

| ARM920T   | 0.35          | <230           | 6.0               | 0.9        |

| ARM1020E  | 0.8           | < 375          | 6.9               | 0.9        |

Table 1.2. Power Trends for ARM Family  $(0.13\mu \text{m} \text{ technology})$

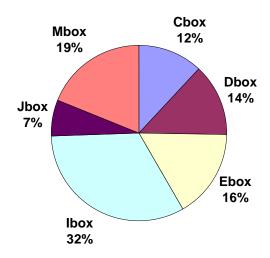

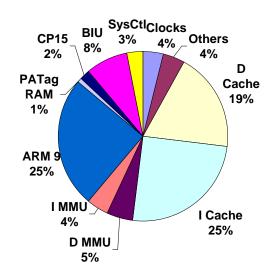

Let us look at the power distribution of the Alpha 21264 and ARM 920T. Figure 1.1 is taken from the power study in Alpha processors [65] and Figure 1.2 is taken from a tutorial on low-power processor [54].

In the Alpha 21264, the EBox and IBox represent the integer and floating point execution processor core. The summed power expenditure of those two is 47%, much higher than the ARM processor core (25%). This is because the 21264 has complex four-issue out-of-order speculative execution pipelines while the ARM 920T has only a single-issue in-order execution pipeline. The more complex the design the higher

• CBox: Bus Interface Unit, Data and Control Buses

• DBox: Data Cache

• EBox: Integer Units

• IBox: Integer Mapper and Queue, FP Mapper and Queue, Instruction Data Path

• JBox: Instruction Cache

• MBox: Memory Controller (Load/Store Queues, TLB etc.)

FIGURE 1.1. Power Distribution for Alpha 21264

power it consumes. The IMMU, DMMU, PATag RAM and the CP15 in ARM 920T contribute in various memory requests and handlings, similar to the function of the MBox of the 21264. The total power of those components is 12%, less than the 19% for MBox in 21264. One reason for that is the ARM uses the virtual address caches to partially avoid the address translation. The BIU and SysCtl in ARM 920T is comparable to the CBox of 21264. The former has total 11% of power consumption and the latter has 12%.

From the power distribution in both figures, we can see that the execution core and the cache memory system take up most power out of the total. This thesis focuses

• D Cache: Data Cache

• I Cache: Instruction Cache

• D MMU: Data Memory Management Unit

• I MMU: Instruction Memory Management Unit

• ARM 9: ARM execution core

• PATag: Physical Address Tag RAM

• CP15: Control Coprocessor

• BIU: Bus Interface Unit

• SysCtl: System Controller

• Clocks: Clock driver and network

FIGURE 1.2. Power Distribution for ARM920T

on reducing the power in the cache memory system. It is notable that caches consume significant amount of power in both processors, totaling up to 44% for ARM 920T and 21% for Alpha 21264. The instruction and data caches in ARM 920T amount for larger portion of power because they adopt higher associativity to amend the low hit rate due to smaller cache sizes.

The off-chip buses are also a significant source of power loss, although not dominant. They are usually very wide—the standard PC memory bus includes 64 data lines and 32 address lines. Each has capacitance that is orders of magnitude higher than the internal bus and requires substantial driving power. It is not unusual for a chip to expend 15–20% of its power on these off-chip drivers [42].

Overall, the memory system is critical in processor design because it affects both the performance and the power consumption. Usually there is a trade off between performance and the power. The modern designs tend to enlarge the cache sizes at different level to maximize the performance, driven by the increasing speed gap between CPU and memory. Larger cache sizes and higher clock frequency will in turn increase the power consumption of the memory system in the future processors.

#### 1.2 Thesis Contributions

The previous section discussed the power distribution for two representative processors. Even though the two processors have completely different designs, they both exhibit a common feature that the memory hierarchy is one of the dominant sources of power dissipation. This includes the on-chip level one caches, the off-chip buses, and the off-chip lower level cache/memory hierarchies. This thesis investigates revolutionary low power solutions targeting different points in the memory hierarchy.

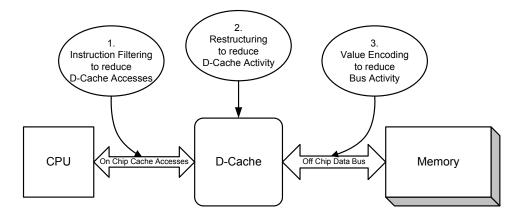

Figure 1.3 gives the high level picture of the major three low power solutions developed for a typical microprocessor. The first reuse mechanism is applied to all the memory instructions. A memory instruction is considered reusable if for read

FIGURE 1.3. Low power designs included in this thesis

operations we can obtain its result without accessing the cache, or for write operations accessing the cache is unnecessary. The reuse checking is performed just before the instruction accesses the data cache. Upon successful reuse, it turns back to prepare for committing, saving one access to the data cache.

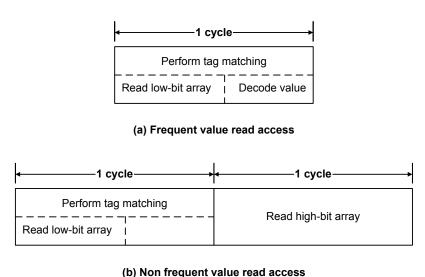

The data cache restructuring is tailored for the data array inside the D-cache. The array is partitioned into two sub-arrays, one with a shorter word width and the other with a longer word width. Data accesses are categorized so that a majority of them can be satisfied by only activating the shorter word width array and the rest of the accesses need both but at longer time. This design trades a little performance for big power savings since accessing the full data array consumes more energy than accessing a partial array.

The encoding algorithm is applied on the off-chip data bus as shown in Figure 1.3. It encodes the values streams evicted from the on-chip data cache and the value streams transferred from the off-chip memory. The algorithm exploits temporal locality of the values appeared on the data bus and transforms the values into codes so that the number of switching wires <sup>1</sup> between neighboring values are reduced as much as possible. Experiments showed that the proposed algorithm outperforms other

<sup>&</sup>lt;sup>1</sup>wires that change state from last cycle to current cycle, i.e. switch from low state to high state or high state to low state

existing encoding schemes while maintaining low overhead in encoder and decoder.

The second and the third low power solutions are based on the frequent value phenomenon that is discovered throughout the memory hierarchy. It is a characteristic of the values that appear in the memory that are relevant to a program. The essential idea is that a small set of distinct values happen very frequently in memory. Similarly, many values transfered across the bus occur repeatedly also. We called this the frequent value phenomenon and studied its interesting properties to better apply it to our low power designs.

In summary, the major contributions in this thesis are as follows.

- 1. A memory instruction reuse mechanism is developed to limit accesses to the L1 data cache, reducing the total energy of the data cache with only small overhead.

- 2. A restructuring of the L1 data cache scheme is proposed. With the newly designed cache, the accesses that are due to frequent values spend only one third or less of the energy than usual. This new design is also applicable to higher level cache or memory in the hierarchy. The redesigned cache slows down the processor by no more than 4%.

- 3. An efficient encoding algorithm is developed for off-chip data buses. This encoding algorithm is able to reduce the switching activity on the data bus by around 30%.

## 1.3 Thesis Organization

In Chapter 2, the background of the low power research in different types of processors is first briefly introduced. Then the related research in low power cache and memory, existing bus encoding research and the previous work in computation reuse is discussed.

Starting from Chapter 3 is the body of the thesis. First is the elaboration on the discovery of the frequent value phenomenon. Three distinct properties of frequent values are established through extensive experimental results. Chapter 4 provides technical methods in identifying the frequent values in various applications. Three methods in accordance with different application scenarios are proposed. Those methods contribute in the low power cache and bus designs in later chapters.

Chapter 5 illustrates the frequent value cache design specifics including constraints we endeavor to meet and the difficulties we solve. Chapter 6 develops the bus encoding algorithm to its fullest extent. A number of variations are included to reduce both the switching activity and the coder overhead.

In Chapter 7, the memory instruction reuse techniques is described. It first presents the reuse opportunities that exist in programs and then develops algorithms to catch the potential possibilities. It also includes methods to fine tune the reuse hardware to achieve low overhead.

# Chapter 2 Background and Related Work

A great amount of research has been performed in the design of energy efficient systems. The techniques developed can be broadly categorized into circuit level techniques and architecture level techniques. These two types of techniques are complementary and therefore can be combined to maximize energy savings. In this chapter, some common methods used in circuit level low power design are first summarized. Then some important architecture level techniques are discussed. Various existing low power techniques in cache design, bus encoding, and computation reuse are discussed respectively. Finally, the simulation environments and metrics used in low power research including the environment used in this thesis are described.

# 2.1 Circuit and Logic Level Techniques

The low level power optimization methods scale technology related parameters in different ways. The major parameters determining power consumption are: supply voltage, operating frequency, effective capacitance and switching activity. Equation 2.1 gives the first order approximation of power consumption at CMOS circuitry level [42].

$$P \approx A \times C \times V^2 \times f \tag{2.1}$$

The above model measures the *dynamic power* consumption caused by the charging and discharging of the capacitive load on gate outputs. Dynamic power is the dominating part of overall power consumption in current technologies. In the above equation, A is the number of switching of the gates, C is the total effective capacitance seen at the gate outputs, V is the supply voltage and f is the operation frequency of

the system. There have been many approaches proposed to reduce the value of these different factors or their combinations in this equation in order to lower P.

Besides dynamic power, the static power is also consumed even when there is no activity. It is the product of the supply voltage and the leakage current which is independent of clock rate and is present once the processor is powered on. Even though static power is not a dominant factor, under certain circumstances the leakage current could go up, increasing the static power. Since the dynamic power is the major portion in the total power consumption, some typical approaches in reducing the dynamic power are summarized and limitations are discussed next.

#### **Voltage Scaling**

Equation 2.1 shows that there is a quadratic relationship between power and supply voltage. Reducing V is therefore an effective way to reduce power. A large body of research that has been devoted to this technique [14].

However, voltage scaling has its own trade off. Reducing the supply voltage causes the circuit to run slower [6]. This will eventually make the applications run for a longer time, which in turn consumes more energy since energy is the product of power and time. Moreover, scaling supply voltage will increase leakage current and leakage power which is another factor to diminish the advantages. High leakage current also makes it difficult to design dynamic circuits, caches, sense-amps, etc. Because of the fundamental limitations stated above, voltage scaling in future techniques will have only marginal practical impact.

#### Reducing Frequency

Another way to reduce the power is by reducing the clock frequency. The power will decrease almost linearly in operating frequency. It has also been found that a lower discharging rate will help maximize the total amount of battery energy. Therefore,

lowering the clock frequency could prolong the time between battery recharges [41]. However, programs run slower with lower frequency and the total energy consumed may or may not decrease. The following equation explains the reason.

$$E = P \times T = P \times I \times CPI / f \tag{2.2}$$

In the above equation, E stands for energy, P represents power, T is time, I is the total number of dynamic instructions of a program, CPI means the average number of cycles needed by each instruction and f is the clock frequency. It is clear from the equation that E depends on both P and T. T is proportional to  $I \times CPI$  and the inverse of f. Given a program and an architecture, the product of I and CPI remains same under different f. Therefore, lowering f will increase T but decrease P. Consequently, the variation in E is difficult to predict if simply the f is reduced.

### Reducing Capacitance

The third parameter in 2.1 is the effective total capacitance. Current methods to reduce C is through downsizing the transistor, reducing the number of fan-out gates, and decreasing the wire capacitance. However, transistor scaling is limited by device physics and silicon-compatible material constraints [64]. The wire capacitance is very difficult to compute due to the layout and the cross-talk between close by wires [6].

Next we will see how reducing the activities can have significant impact on lowering power consumption.

#### Reducing Switching Activities

The fourth factor is the dynamic switching activity. Minimizing this factor is effective in power reduction when the chip technology and the supply voltage is set. Reducing switching activities is also a very flexible in design as the architects have the most design space at different levels to reduce useless switching. The idea here is to minimize activities of certain functional units or chip areas that are not performing useful

computation. Typical techniques at the hardware level that have appeared in the literature are the following.

1. Clock Gating The power consumed by the clock network, which includes the clock generator, the clock drivers, the clock distribution tree, the latches and the clock loading due to all clocked elements, is more than 40% in high-performance processors [62]. Clock gating, for this reason, has been widely employed to turn off those parts of the clock tree to latches or flip-flops that are not being used in each cycle [9, 25, 27]. It can be implemented by adding special "enable/disable" signal gates to the clock network. And the low area and performance overhead is paid off by the significant amount of power reduction.

Unfortunately, there are a number of issues that must be considered in clock gating. The most important concern is that the disabled block may not power up in time, or that modified clocks may generate glitches. Other issues such as clock skews and high transition current all make clock gating more difficult to design new CPUs.

2. Sleep (Standby) Modes Many state-of-art processors have built-in sleep (standby) modes. Typically, the clock is stopped for all but certain sections of the processor after the default period of inactivity. The processor does not perform any work or performs very little work while asleep resulting in significant power savings. However, there is a long latency for the system to wake up so it is profitable to put the system into sleep mode only when it is expected to sleep for a relatively long time.

# 2.2 Architecture Level Techniques

Most architecture techniques trade off a little performance for lower power consumption, achieving overall energy reduction (see equation 2.2. Typical approaches include

using simpler or smaller functional units, turning off part of functional units when they are not in use, removing certain redundancy and reusing computation results. Below, some novel techniques that are applied to different architecture components are briefly summarized.

## 2.2.1 Low Power Designs for Processor Core

For most high performance processors such as Alphas and Pentiums, the bulk of power goes into the pipeline issue logic. Various techniques have been proposed targeting this high power component. Since the primary goal of those processors is high performance, most techniques reduce the issue logic activities without much degradation in instruction throughput. Bahar et al. developed the Pipeline Balancing algorithm to dynamically adjust issue width on demand [5]. The algorithm is based on the observation that application programs do not always execute at their peak IPC. Therefore, the issue logic does not need to operate always at full width. In another design [22], it was observed that the issue logic wasted energy in trying to wake up empty instruction queue slots and already ready for execution instructions. Instead of limiting the searching width, they proposed to dynamically resize the instruction queue. This approach cuts off the power in wake-up activities that were performed beyond the dynamic queue length. In addition to resizing the issue width and instruction queue length, a more aggressive method in tuning resource sizes was developed [46]. In that method, the power sinks on data path as instruction queue, reorder buffer and load store queue were all allowed to vary sizes according to the needs of the executing program.

There are other techniques in reducing the power of the pipeline. For example, compressing the significant bits of values flowing through the pipeline can be used to reduce the ALU, register files and internal latches activities [13]. The technique is even extended to instruction and data caches as well.

Next, some representative low power solutions for caches the have appeared in the literature are described.

#### 2.2.2 Energy Efficient Cache Designs

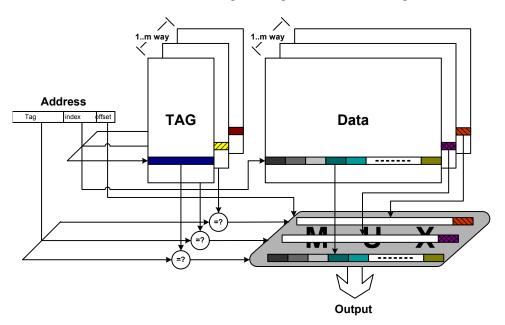

A Conventional Cache. Figure 2.1 plots the typical m-way set associative cache structure. It consists of Tag arrays, Data arrays, some comparators, multiplexers and internal latches. The major power spent in the cache is the tag comparison and data reads and writes. The tag comparison involves reading m tags from the Tag arrays and performing m comparisons. Data reads and writes involve activating m cache lines from the Data arrays and selecting the right word in the right line.

FIGURE 2.1. The structure of a general cache (derived from the standard set-associative cache structure [29])

**Energy Efficient Designs.** The problem of reducing the energy consumption of the conventional cache can be explored from different angles and in different cache components.

- 1. Reducing Power for Set Associative Caches. Traditional caches are designed for maximum performance. For example, a set associative cache outperforms a direct mapped cache because it decreases cache misses by probing multiple entries of the cache in parallel. However, a cache hit appears in only one entry, meaning that the energy spent in probing other entries are wasted. The Way-Prediction and Selective Direct-Mapped schemes were proposed to solve this problem [48]. Alternatively, certain cache ways can be disabled when the program has modest cache activity [2]. Even though the performance degraded due to less number of available cache ways, an overall energy saving was still achieved.

- 2. Reducing Power for Tag Path. The tag path of the cache consumes relatively high power. It mainly comes from the comparators that try to determine a hit or a miss. For this reason, methods were proposed to reduce the number of tag checks [45, 67]. One approach is that the compiler determines those loads and stores that are guaranteed to access the same cache line [67]. Those instructions can directly access the data arrays without tag checks. Since the instruction addresses are usually sequential, such a removal can be applied to the instruction cache effectively [45]. This technique can be implemented purely at the hardware level.

- 3. Reducing Power for Data Arrays. To diminish the energy spent in data arrays, one can either reduce the dynamic energy or the static energy. Dynamic energy is consumed when a cache line is driven for reading or writing data. It can be cut down by limiting the length of a line that needs to be driven. More specifically, only one word in a line, indicated by the offset field in the address, needs to be driven for reads and writes [24]. This involves wiring changes to the data arrays. The scheme saves energy in driving the other words that are discarded later in the same line.

Static energy is always consumed even when there is no activity. Kaxiras et. al. and Flautner et. al. introduced techniques to shut off the cache lines or bring them to a drowsy state [21, 35]. The lines being shut down are those that will not likely be accessed in the near future. Both techniques significantly reduced the static cache energy.

- 4. Reducing Power Based on Values. There are some designs that are based on the contents stored in the cache. Villa et al. found that data caches contain a lot of zeroes [63]. They introduced a compression method for zeroes inside the cache such that they can be represented by only a single bit. Reading or writing a single bit is much cheaper than 32 bits in energy consumption.

- 5. Other Techniques. Miscellaneous techniques including specializing caches [31], sequentializing cache accesses [28] code compression for instruction caches [38] are all valuable.

This thesis presents two power reduction techniques. The first technique focuses on reducing the power spent by data arrays. The average cache access power is reduced through data array restructuring. The second technique focuses on limiting the number of accesses to the cache through the reuse of instructions.

#### 2.2.3 Bus Encoding Techniques

Existing bus encoding algorithms can be categorized into address bus encoding, data bus encoding, and general purpose bus encoding. There are some very good encoding algorithms for address buses, especially instruction address buses, because most of the address stream is sequential. However, a similar regularity does not exist in data buses since it is assumed that the value stream on the data buses is randomly distributed. Thus, the encoding algorithms for the data bus are mostly limited to statistic investigation. The general purpose encoding algorithms do not result in

significant switching reduction. This is because the data value streams and address streams exhibit very different characteristics. It is therefore difficult to develop a general algorithm that is effective for both.

General Purpose Encoding. A very simple encoding algorithm called Bus-Invert was proposed by Stan et al. [59]. In this scheme, either the original address or its binary inverse is sent on the bus depending on the Hamming distance between the current address and the previous transmitted value. The rule is to always send the value that would cause the number of switching that is less than half of the total bus width. This scheme is applicable to both address and data buses and is adopted in many other encoding schemes because of its simplicity. Ramprasad et al. developed a framework [50] for generic encoder-decoder architecture. They also proposed an adaptive method that requires huge hardware overhead.

Address Bus Encoding. Gray coding [61] has been proposed to minimize the switching on the instruction address bus. The encoding scheme ensures that when the address is sequential, there is only one switch between two consecutive address words. T0-C coding was developed by Aghaghiri et al. [1]. It freezes the bus when the addresses are sequential. The bus transmits values normally when the address is non-sequential. The Working-Zone-Encoding [43] is developed based on memory reference locality. The memory regions being referenced by a program are divided into working zones. Instead of transmitting a sequence of complete addresses that exhibit locality, in this technique, the offset of current reference with respect to the previous reference to the same working zone is sent over the bus, along with an identifier of that zone.

**Data Bus Encoding.** As mentioned earlier, there are not many encoding schemes for the data buses. Even though the generic methods can be adopted, the achievable

switching reduction is modest. Benini et. al. presented the adaptive encoding in which new codes are generated based on the past N data samples [7]. This mechanism has huge hardware overhead so they developed further techniques in scaling down the sampling and encoding sizes.

This thesis introduces a new encoding scheme for data buses that is based on observations of the data streams sent on the bus. The frequent value characteristics are utilized into the encoding algorithms. The algorithm achieves a significant reduction in switching counts.

#### 2.2.4 Computation Reuse

The reuse mechanism has been exploited in many papers [4, 18, 30, 53, 57]. It is based on the empirical observations that many instructions, and groups of instructions, having the same inputs and outputs are executed repeatedly. Those instructions can be identified either dynamically [4, 30, 53, 57] or statically [18]. In dynamical instruction reuse, the inputs and outputs of the instructions are memorized in some hardware together with necessary tags. On successful reuse test, the result can be obtained directly from the hardware instead of the functional units [57] and [4]. More aggressively, the reusability was extended to block level [30]. There the authors exploited the inputs of a basic block and reuse the result of the block. This approach incurs expensive hardware overhead since all the block inputs and outputs need to be saved.

This thesis exploited a reuse technique for memory instructions. It aims at getting the results at an early stage in the pipeline so that the dependent instructions can read the value earlier. Consequently, an access to the cache can be saved to reduce the cache power dissipation.

#### 2.3 Simulation Tools

For computer architecture researchers, realizing novel designs in hardware is too expensive and time consuming, especially in an early stages of development. Therefore, most research relies on simulation tools that run at a tractable amounts of time for real sized programs, and provide reasonable accuracy. Most of all simulation tools are easily extensible.

The SimpleScalar tool set [11] is a widely used simulator in the modern processor architecture research community. The tool set simulates a slightly simpler MIPS-IV architecture and provides from an extremely simple and fast functional simulator to a detailed out-of-order issue processor simulator. The tool set contains a GCC based compiler and utilities that help generate MIPS object code. The advantage of SimpleScalar is that it is fast, flexible and efficient. Written in C code, the tool allows users to easily incorporate new designs into the simulator within a reasonable amount of time.

The success of SimpleScalar has made its power evaluation extension easy. Simple-Power [75] is the in-order 5-stage SimpleScalar simulator augmented with an energy estimation tool. It uses transition sensitive energy models to estimate the energy spent by processor components based on their states transition. SimplePower's limitation is that no energy estimation is available for out-of-order superscalar processors. The problem is solved in Wattch [10] which can model energy for different types of complex processors simulated by SimpleScalar. Wattch models the dynamic energy consumption of each major processor component and computes the accumulative energy every cycle. Though fast and simple, Wattch has been criticized for its large error in computing energy consumption for typical processors. Other processor energy simulators such as TEM<sup>2</sup>P<sup>2</sup>EST [19] and AccuPower [47] are more accurate but are not available for public use yet.

The study of the memory hierarchy calls for similar cache and memory simulators.

Some early cache simulation tools such as CacheProf [55] and Dinero IV [20] are effective functional simulators that produce mainly cache references, hits and misses information. Those tools are trace-driven for fast running time. They do not provide cache timing information which is desired for performance analysis. The newer version of SimpleScalar now has its own cache simulator of up to two levels. Cache and memory hit/miss latencies are calculated so that the performance impact of memory hierarchy can be easily studied.

As the interest in energy efficient memory hierarchy designs increased, energy models for cache and memory also emerged. The CAPE [34] tool used an analytical model to estimate the power dissipation in caches. This model is then adopted in SimplePower with enhancements that includes the off chip memory energy as well. By far, the most popular cache timing and power tool is the CACTI series [66]. CACTI 1.0 [32] models access time for non-fully associative caches. CACTI 2.0 added [52] modeling support for fully-associative caches, a power model, technology scaling, multiported caches, and improved tag comparison circuits, as well as other improvements to CACTI 1.0. CACTI 3.0 [56] includes modeling support for the area and aspect ratio of caches, caches with independently addressed banks, reduced sense-amp power dissipation, and other improvements to CACTI 2.0. The Wattch [10] simulator incorporated CACTI 2.0 into its cache energy models. CACTI has been extended to XCACTI by Renau et. al. in [31]. The XCACTI provides energy measurement for not only read operations, but also write operations, write back and line fill operations on cache misses.

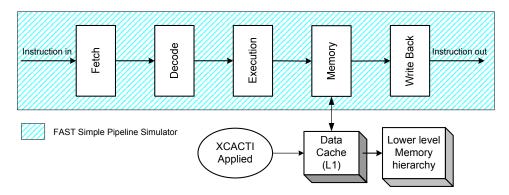

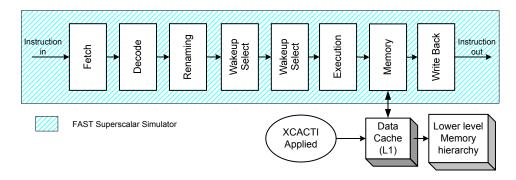

In this thesis, a cycle level simulator FAST developed by Onder et. al. [44] is used for processor cores. FAST can automatically generate simulators from an architecture description language (ADL). It currently supports the MIPS ISA which is also written in ADL. Three types of simulators are used: (1) a simple fast functional simulator that simply executes instructions one by one as if they are going through a single staged pipeline (Figure 2.2); (2) an in-order processor simulator which simulates the

Figure 2.2. A Simple One-Stage Simulator.

FIGURE 2.3. A Pipelined Simulator.

standard five stages pipeline (Figure 2.3) and (3) an out-of-order superscalar simulator (Figure 2.4). The first simulator is used mainly to generate trace information such as the memory instruction sequence for studying the cache access behavior. The second simulator is used in investigating embedded processor designs and the third is for exploring high performance superscalar processor designs. The research work contained in this thesis contributes to the FAST system in that the memory hierarchies are added to the previous processor cores. The memory extension can simulate as many levels of cache as possible, either unified or split, from direct-mapped to fully associative cache. Moreover, the memory system can output accurate latency information as well as energy consumption statistics which is obtained through plugging in the XCACTI energy model (Figure 2.3 and 2.4). In designing new energy efficient caches, the XCACTI tool is also modeled such that it complies with the modified caches. The enhanced FAST system allows us to investigate the memory hierarchy

impacts on both performance and energy consumption. We also extracted energy models from Wattch for non-cache structures such as array structure in modeling the energy in hardwares such as a simple indexing table.

FIGURE 2.4. A Superscalar Simulator.

### 2.4 Energy Measurement Metrics

Using correct metrics in experimental evaluation is crucial and has been studied by Gonzalez and Horowitz [25]. Earlier researchers have used only the energy metric in evaluating new designs. Unfortunately, this is misleading since the energy can be reduced dramatically by slowing down the processor or cutting down the supply voltage as we have discussed earlier. Therefore, Gonzalez and Horowitz proposed an energy\*delay metric to combine both factors. The delay factor is the total execution time of a program, usually measured in terms of number of cycles. The energy\*delay metric better describes the improvement or deterioration of new designs that trade performance for energy. Since then, this metric is widely used in the low power research community.

The following chapters contain the body of this thesis starting with our frequent value observations which is described next.

# Chapter 3 Frequent Value Phenomenon

Recent research has demonstrated that values produced by executing instructions exhibit a high degree of value locality, that is, multiple executions of the same instruction often produce the same value [23, 40]. Value locality has been exploited in the design of value reuse and prediction mechanisms for superscalar processors.

In this chapter another kind of locality is identified, termed frequent value locality; this is also quite prevalent in programs. The first aspect of the frequent value locality is that if the values involved in memory accesses are tracked, it can be observed that at any given point in the program's execution, a small number of distinct values occupy a large fraction of these referenced locations. In fact it is observed that on average in fifteen of the Spec95 <sup>1</sup> [58]. programs, eight distinct values occupy 48% of all allocated memory locations throughout the execution of the program. The second aspect of this phenomenon is that the set of frequent values remains quite stable throughout the execution of the program. The third and final aspect of frequent value locality is that frequent values are scattered fairly uniformly throughout the memory.

# 3.1 Characteristics of Frequent Values

The frequent value locality phenomenon characterizes the behavior of values being held in live memory locations of running programs. The following three properties of the values characterize frequent value locality. These properties are demonstrated

<sup>&</sup>lt;sup>1</sup>The Spec95 benchmark suites were released by the Standard Performance Evaluation Corp. (SPEC) on August 21, 1995. The suites provided the worldwide standard for measuring and comparing computer performance across different hardware platforms. The Spec95 comprises two sets (or suites) of benchmarks: CINT95 for compute-intensive integer performance (8 programs) and CFP95 for compute-intensive floating point performance (10 programs). The Spec benchmarks were selected from existing application and benchmark source code running across multiple platforms.

by analyzing the behavior of 15 Spec95 benchmarks when run on reference inputs. The left 3 benchmarks do not go through the FAST simulator due to incompatible libraries, therefore are not experimented in this experiments.

#### 3.1.1 Property I: Frequent Value Occurrences

A small number of frequently occurring values, called **frequent values**, occupy a substantial fraction of memory locations allocated to an executing program.

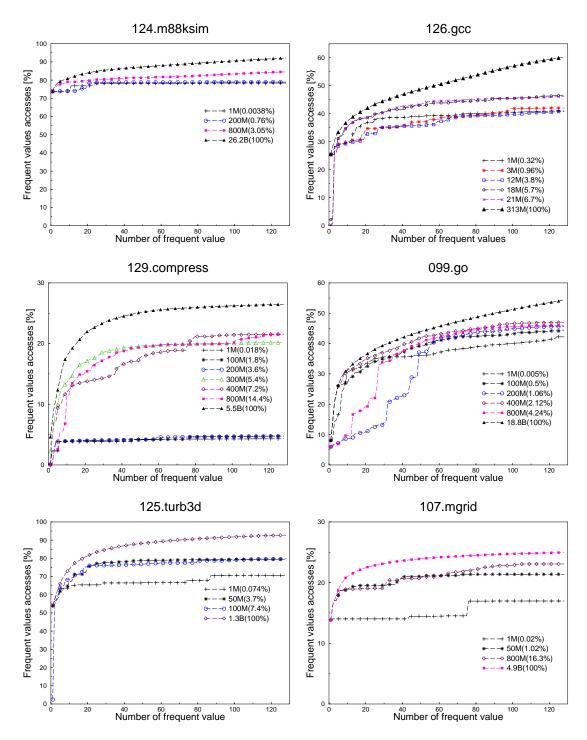

To establish the above property we ran the benchmarks and examined the values in memory locations every 10 million instructions and averaged the frequencies of the values over the entire set of collected samples. During each sampling point, the entire memory space was scanned through and every distinct value was ranked according to its occurrence frequency. The memory locations that were considered at a given point included those that were of interest to the program. In particular, the currently allocated stack and heap memory locations were considered. After the completion of the program's execution, for each encountered value, its average frequency across all sampling points was computed. The resulting average frequencies of all values were sorted in descending order. Values at the top of the list are more frequent than the values that appear later in the list. A significant amount of time collecting this data was needed as a program run typically involved execution of several billion instructions.

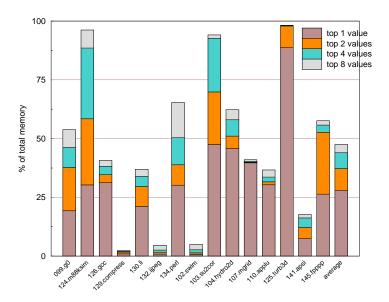

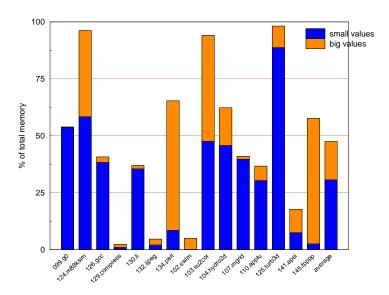

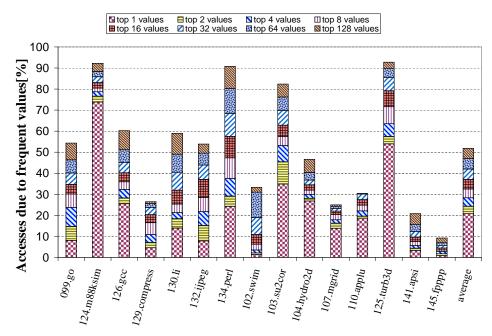

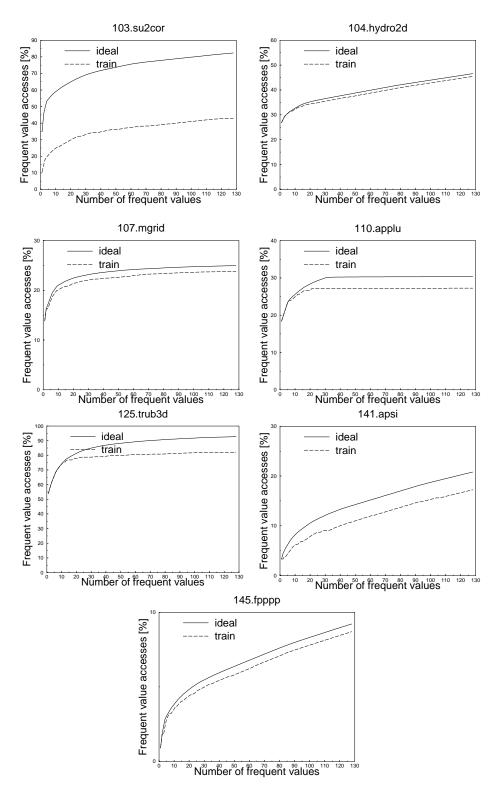

Figure 3.1 shows that 12 out of 15 benchmarks exhibit this property and on an average around 48% of memory locations are occupied by the top eight frequently occurring values in the 15 Spec95 benchmarks that were used in this study. The top 8 frequent values are listed in Table 3.1. Examination of these values shows that there is a mix of small values (that can be represented using 16 bits) and large values (which require more than 16 bits). While the same small values (e.g., zero) are often observed across different programs, the same is not true for large values. This is

FIGURE 3.1. Amount of memory occupied by top 8 frequent values.

because the large values are often memory addresses or string constants. Figure 3.2 shows what fraction of locations were occupied by small frequent values and large frequent values. In some programs the large values occupy a substantial number of locations.

| Benchmark          | 1        | 2        | 3        | 4        | 5          | 6        | 7        | 8           |

|--------------------|----------|----------|----------|----------|------------|----------|----------|-------------|

| 099.go             | 0        | 351a     | 4        | 1        | 2          | 3        | 349      | 1c1         |

| 124.m88ksim        | 0        | 4022ada0 | 1c       | 40229030 | 4022a610   | 60d12    | 8048bf7d | 1db82340    |

| $126.\mathrm{gcc}$ | 0        | e7       | 403      | 80004    | 40252734   | 10001    | 20       | 1b          |

| 129.compress       | 0        | fffffff  | 65687420 | 20656874 | 61687420   | 90a0a0a  | 68742065 | 20656820    |

| 130.li             | 0        | 3        | 1        | 4        | 6          | 1000000  | 5        | 40280df4    |

| 132.ijpeg          | 0        | 1        | ffff     | 10000    | ffff0000   | fffffff  | 10001    | 1ffff       |

| 134.perl           | "xxxx"   | "x x "   | 0        | " xx "   | "x xx"     | "xx x"   | " x x"   | "xx"        |

| 102.swim           | 47435000 | 47435001 | 47434fff | 47435002 | 47434ffe   | 47435003 | 47434ffd | 47435004    |

| 103.su2cor         | 0        | 3fe00000 | 40040000 | 807bcdaf | 3 fd5 f8e1 | 40290000 | 3fec71bc | 390cf5ba    |

| 104.hydro2d        | 0        | 3feccccc | ccccccc  | 3fe33333 | "3333"     | 3ff00000 | "0000"   | bc400000    |

| 107.mgrid          | 0        | 80000000 | 3c300000 | bc300000 | 3c400000   | bc400000 | bc200000 | 40000000    |

| 110.applu          | 0        | 2752547  | 4189374c | bfe16c8b | 43958106   | 3f7b089a | 3f90e560 | 80000000    |

| 125.turb3d         | 0        | 80000000 | ""       | 3ff00000 | "::::"     | 1        | 6        | 3bc79ca1    |

| 141.apsi           | 0        | 3fb99be4 | d443f3ee | d443f3ef | d443f3f0   | 3fb99999 | 9999999a | ""          |

| 145.fpppp          | 9999999a | 3fc99999 | 0        | 33333333 | 3fd33333   | 47ae147c | 3fb47ae1 | 3 fa 47 ae1 |

Table 3.1. Frequently occurring values ordered by decreasing frequency.

We have identified several reasons for the frequent value phenomenon. The first reason is that programs usually contain many constants such as character constants

FIGURE 3.2. Amount of memory occupied by small vs. big values.

and NULL pointer value, or, near constant values such as boolean variables which toggle between 0 and 1. Our study shows that they not only exist in register but also in memory as well, even when the program is compiled at -03 optimization level. The second reason is that many programs contain dynamically allocated data structures such as hash tables or binary trees. Accessing to different nodes frequently requires to start from the same head of the bucket or the root of the tree. The third reason is that the frequent values sometimes come from the inputs of a program such as a text file input of a compiler. There are only limited keywords for a language that repeatedly occur in the file. And the compiler usually loads the bulk of the file into the memory before compiling.

Currently, the frequent values are observed in the 32-bit machine applications. If the word width is increased to 64 bits, the frequent values will not be affected greatly for the following reasons. First, the small program constants will be represented in 64 bits by simply having sign extension in the high ordered bits. Second, the string constants will also be frequent except that they have different lengths. More specifically, if a frequent string is shorter than 32 bits it will still be frequent in a 64-bit machines with the same length because values are word-aligned. If a frequent string required multiple 32-bit words (each 32-bit substring must be frequent also), it is then represented in half number of 64 bits in the 64-bit machine. If the frequent values are memory addresses, their binary representations will be different in two different types of machines. However, the existence of frequent values is a property of a program. Those 32-bit frequent memory addresses will still be frequent in a 64-bit machine except that the binaries are in different forms.

#### 3.1.2 Property II: Frequent Value Stability

The set of frequently occurring values remains fairly stable over a program run which implies that frequent values can be identified and exploited during a program run.

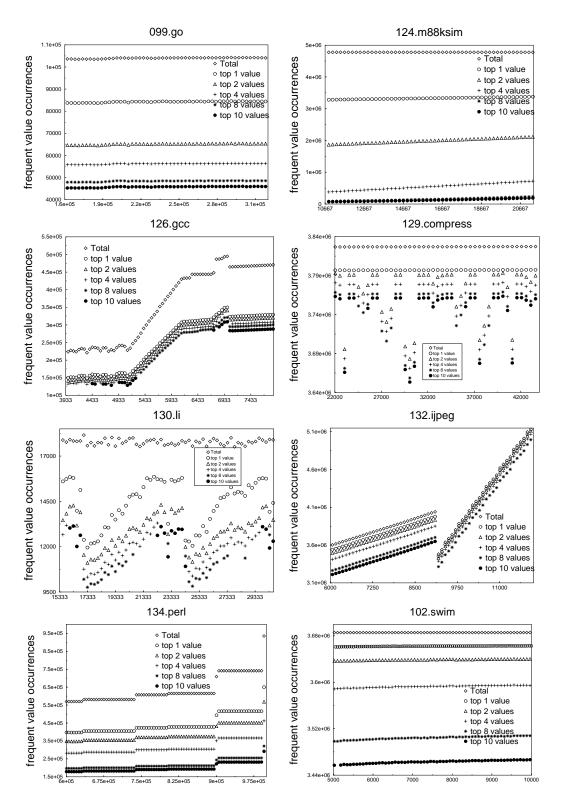

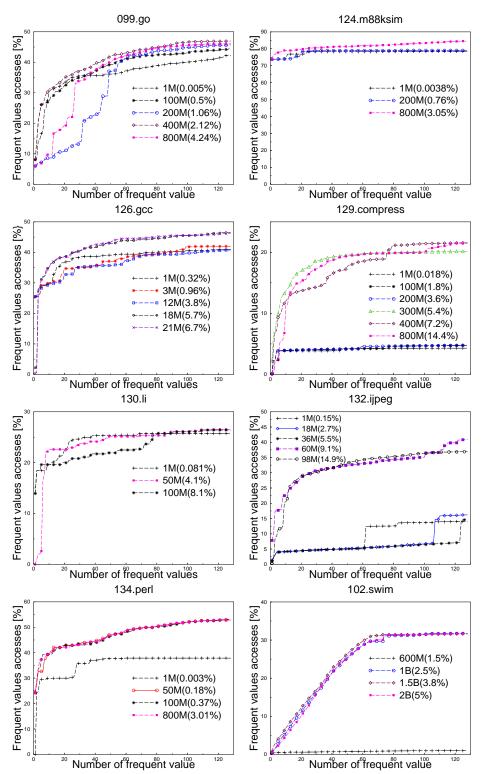

To observe this property the occurrences of frequent values throughout the program execution were studied. The graphs in Figure 3.3 and 3.4 show the behaviors of the benchmarks over their entire execution. To generate these graphs, the top ten frequent values were first found using the methodology already described above. Next the programs were run again and during these runs, at each sampling point, for each of the top ten frequent values, the number of memory words that contain the frequent value is noted down.

In the graphs the X axis represents time and the Y axis represents the memory occurrence characteristic of the various frequent values. To make the graphs more readable we did not plot these graphs for entire execution of the program but instead carefully reduced the duration to a period in the middle of program's execution. However, when the scope of the data presented is narrowed, the data for the entire execution is first examined and we only narrowed the duration for which the data is presented if the behavior of the program was similar for the remainder of the execution. In these graphs the top-most line represents the total number of allocated memory locations. The subsequent curves give us an idea of how many locations

FIGURE 3.3. Stability of frequent values over program execution.

FIGURE 3.4. Stability of frequent values over program execution.

correspond to the top ten most frequently occurring values. The difference between the first (top most) and second curve is the number of locations with the top most frequent value. The difference between the first and third curve is the number of locations containing to the top two frequent values and so on. From the results it can be seen that the fraction of allocated locations occupied by a given number of frequent values remains fairly stable throughout the program execution. This is because the same values continue to occur frequently over the entire execution of the program.

#### 3.1.3 Property III: Frequent Value Distribution

The frequent values are distributed fairly uniformly throughout memory which implies that no matter which part of memory is accessed, it is likely to encounter these values.

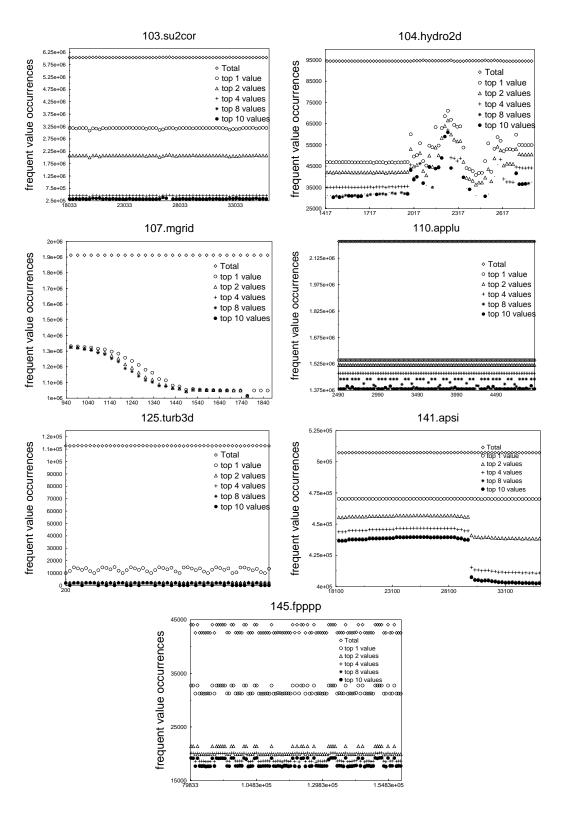

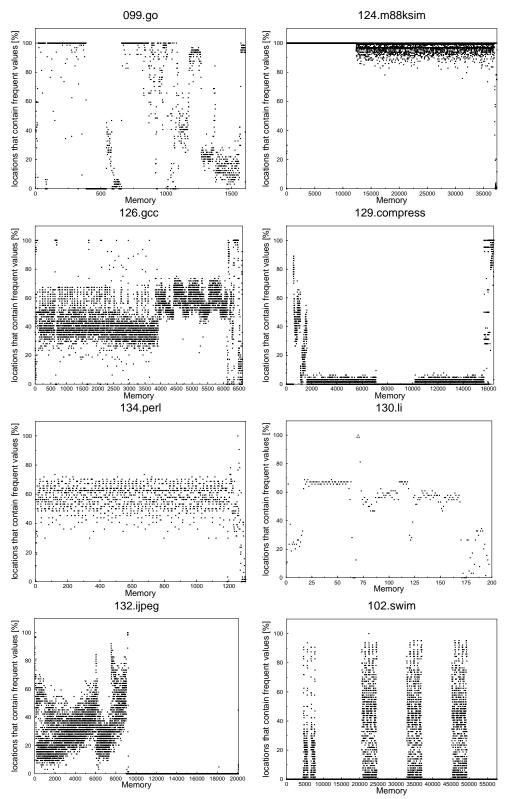

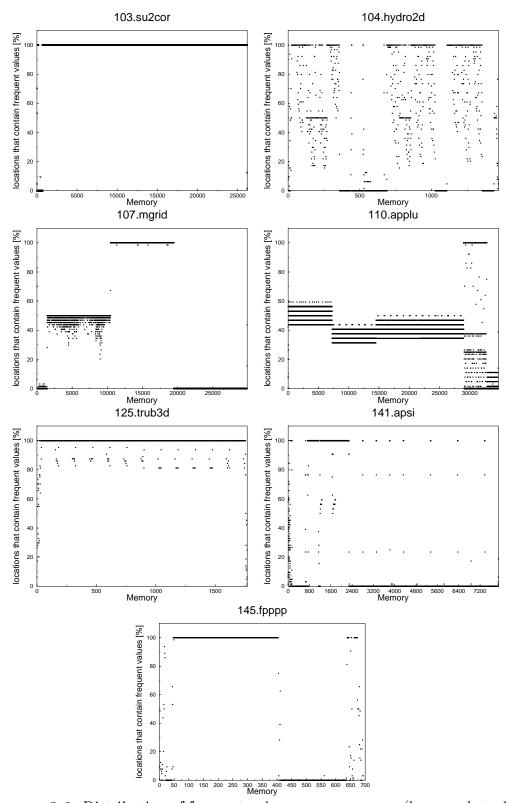

To establish the above property, the distribution of frequently occurring values in memory is plotted as shown in Figure 3.5 and 3.6. The data in these graphs represents the snapshot of memory at a point when the programs were nearly half way through their execution. The referenced memory was broken into blocks of 800 consecutive locations each and the percentage of frequent values in each block of 800 locations was plotted as a point in the graph. A threshold of top 8 frequent values is selected in these graphs. As can be seen, for nearly all of the programs the frequent values are scattered across the memory and for many programs the distribution of frequent values across the memory is quite uniform.

# 3.2 Frequent Value Locality vs. Value Locality

Although the frequent value locality phenomenon is related to recently discovered concepts of value locality and value prediction [40], there are important differences between them. Value locality addresses the likelihood of a previously-seen value recurring repeatedly within a storage location. The authors limited their study to only the general-purpose or floating-point registers that are targets of integer, floating-point

FIGURE 3.5. Distribution of frequent values across memory (heap and stack).

FIGURE 3.6. Distribution of frequent values across memory (heap and stack).

and memory instructions. The study is a **register** value locality and characterizes only the values encountered during multiple executions of specific instructions.

Unlike the study on only streams of instructions, our frequent value locality characterizes the behavior of values present across the **memory** allocated to the program, throughout the execution of the program. Substantial number of experiments were conducted and interesting spatial and temporal properties of frequent values were discovered. The work presents a thorough insight of frequent values that are useful in exploring memory value related applications. Register value locality is exploited for carrying out value prediction and speculative execution of instructions to speed up a program's execution. Frequent value locality can be exploited in designing the memory hierarchy to achieve better power or performance behavior.

#### 3.3 Summary

In this chapter, the frequent value phenomenon has been demonstrated by characterizing it into three distinct properties. The claims are supported through elaborative experimental data obtained from running 15 Spec95 benchmarks. The chapter first showed the existence of the frequent values across most of the programs tested. Then the stability of the frequent values during the execution time line was illustrated. Finally, the distribution of the top frequent values in the memory spaces at the mid point of execution was shown.

Though the set of ideal frequent values have been presented in this chapter, it is important to develop application driven techniques in finding those frequent values. And we will introduce those techniques in the next chapter.

# Chapter 4 Identifying Frequent Values

#### 4.1 Frequent Value Identification Introduction

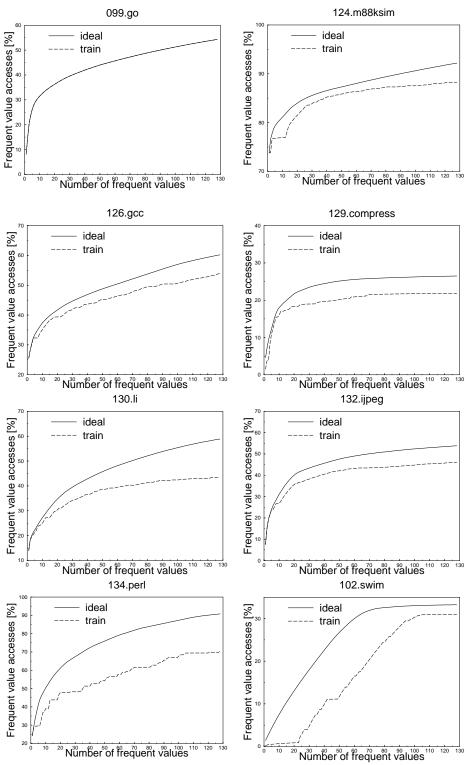

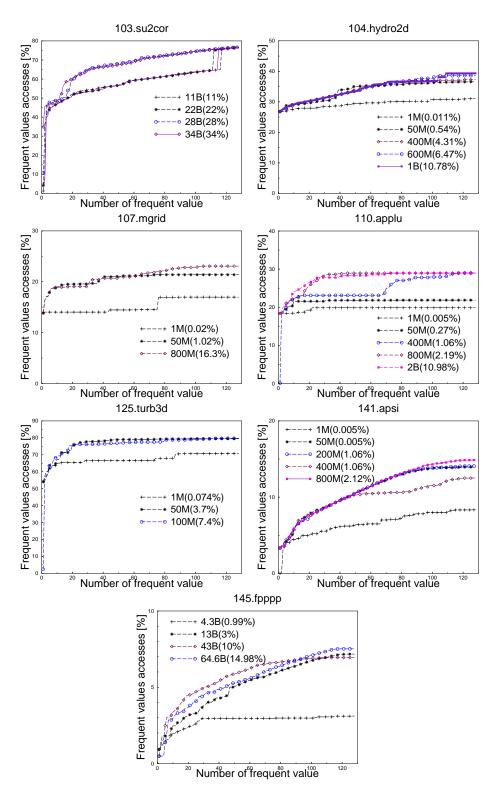

The data in Figure 3.1 showed that the large frequent values always vary from program to program and small frequent values can also differ across programs. Since there is no universal set of frequent values, methods for identifying these values must be developed. Before describing the different methods for finding frequent values, it is useful to understand the nature of applications that will make use of these methods.

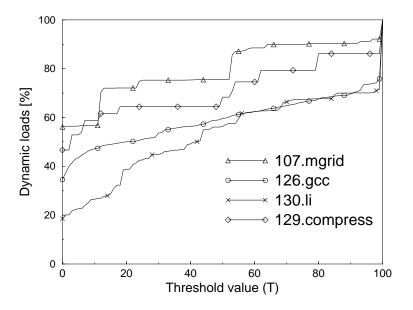

While it has been discussed the frequent value locality in context of memory contents of a program over its entire execution, the observations have much broader implications. Given that frequent values were observed across the memory, it is also expected that these values would be frequently encountered at all points in the memory hierarchy, for example in the on chip data cache, on the data bus that brings data into the on chip cache, and of course in the main memory itself. At different points in the memory hierarchy at which frequent value locality is being exploited, different types of frequent value finding methods may be appropriate.