# UNIVERSITY OF CALIFORNIA RIVERSIDE

Hardware Acceleration of Irregular Applications Using Event-Driven Execution

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

by

Shafiur Rahman

December 2021

### Dissertation Committee:

Professor Nael Abu-Ghazaleh, Co-Chairperson

Professor Rajiv Gupta, Co-Chairperson

Professor Walid Najjar

Professor Daniel Wong

University of California, Riverside

### Acknowledgments

As I am close to the end of this journey, I look back and remember all the people who have inspired, supported, and guided me along the way. There are so many people I call family, friends, and mentors. I probably cannot adequately thank all of them here. But I am grateful that our paths crossed.

First and foremost, I must thank my committee members for their thoughtful advice and feedback, and their support over the years. I appreciate the time they have contributed into all the milestones in my journey.

This work would not have been possible without the support of my advisors. I am grateful to Professor Nael Abu-Ghazaleh for extending me the opportunity to begin my PhD here. He has been an exceptional mentor in both professional and personal aspects of my doctoral journey. He had great patience and insights to motivate and mold a young researcher. I am incredibly lucky to be working with him. I want to thank Professor Rajiv Gupta. He was always available to offer me guidance and ideas in every aspect of my research. His excitement for any new idea was contagious. His supervision was a significant contributor to the timely completion of this project. The steady guidance and continuous encouragement from my advisors have made me a better researcher and made this project achievable. There were no two scholars better suited to guide me to complete this project.

I want to thank all my colleagues in our group. You were the most remarkable part of my graduate life. Our time in and out of the lab will always be a cherished memory. I regret that we could not make the most out of our time on campus because of the pandemic. But I am hopeful that we will get chances to make up for it once the world becomes normal.

I am thankful to the people with whom I started my first research work during my undergraduate studies. Those days made me ready to undertake this far greater responsibility today. Thanks to my professors, Md Atiqur Rahman Ahad and Upal Mahbub, and my friend, Tonmoy Roy, for our collaboration. What I learned from them is invaluable.

A special thanks to my parents, who always supported all my life decisions and were with me in every step of my life. Thanks to everyone in my family – all the sacrifices I made, they made it too. I am thankful for all the support and comfort they have given me from miles away.

Finally, and very importantly, I would like to acknowledge my wife and partner, Farzana Kabir. You have been there through all the good times and all the struggles. We both shared the same journey at the same time. Thank you for being so understanding and being the person I can rely on. Your unwavering support and steady presence made it so much easier for me.

DEDICATION

To my mother.

### ABSTRACT OF THE DISSERTATION

Hardware Acceleration of Irregular Applications Using Event-Driven Execution

by

#### Shafiur Rahman

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, December 2021 Professor Nael Abu-Ghazaleh, Co-Chairperson Professor Rajiv Gupta, Co-Chairperson

The consistent growth of DRAM memory bandwidth and capacity has enabled the computation of increasingly larger workloads in high-performance computing. However, the memory latency improvement over time is nominal, which severely bottlenecks the performance of modern systems. Modern computers rely on the exploitation of data locality using large cache hierarchies to keep the throughput high. Additionally, architects employ multicore and multithreaded architectures to boost throughput by extracting parallelism. However, irregular applications do not enjoy the same performance gain from these techniques. The inadequate data locality in these applications renders the cache ineffective, and the dynamic data dependence causes sub-optimal parallel processing. Hence, researchers are motivated to look beyond conventional CPU and GPU platforms towards dedicated hardware accelerators for these applications.

In this dissertation, we present strategies and architectures for accelerating irregular applications using the event-driven execution technique. We examine three irregular applications – Parallel Discrete Event Simulation (PDES), Graph Processing, and Streaming Graph Analytics – to study their limitations in conventional systems and solve these challenges using hardware primitives to build generalized accelerator frameworks. Our custom datapaths based on event-driven execution models promote parallelism and memory bandwidth utilization in these applications.

The first application, Parallel Discrete Event Simulation, is inherently event-driven. It demonstrates ordered irregular parallelism, characterized by strict ordering between tasks that constrains parallelism. First, we design an efficient hardware priority queue, which becomes the core component of our event-driven systems. Then, we build a highly scalable accelerator, PDES-A, that incorporates a decoupled datapath for robust transmission of events and masking long memory access latency.

The second application, graph processing, has partial ordering among the tasks and possesses similar dynamic data dependence. We convert the traditional iterative execution model into an event-driven execution model. We demonstrate that fine-grained control over the dynamic memory access patterns is achievable through strategic manipulation of events to maximize spatial locality and, hence, memory bandwidth utilization. Our acceleration framework, GraphPulse, uses this model to accelerate asynchronous graph processing.

Finally, we study a more complex variation of graph processing, streaming graph analytics, to illustrate the extensibility of the event-driven model. This application has multiple types of computation tasks and requires multi-phase execution. We employ incremental recomputation of streaming data to reduce redundant computation. We develop an incremental graph computation model suitable for the event-driven paradigm and subsequently develop JetStream to support streaming graphs using this algorithm.

# Contents

| Li | st of        | Figure  | es                                                     |  |  |  |

|----|--------------|---------|--------------------------------------------------------|--|--|--|

| Li | st of        | Tables  | 5                                                      |  |  |  |

| 1  | Intr         | oducti  | ion                                                    |  |  |  |

|    | 1.1          | Motiva  | ation: Challenges in Irregular Applications            |  |  |  |

|    | 1.2          | Contri  | ibutions of the Dissertation                           |  |  |  |

|    |              | 1.2.1   | PDES-A: Parallel Discrete Event Simulation Accelerator |  |  |  |

|    |              | 1.2.2   | GraphPulse: an Accelerator for Graph Processing        |  |  |  |

|    |              | 1.2.3   | JetStream: Accelerator for Streaming Graph Analytics   |  |  |  |

|    | 1.3          | Organ   | ization of the Dissertation                            |  |  |  |

| 2  | Related Work |         |                                                        |  |  |  |

|    | 2.1          | Paralle | el Discrete Event Simulation                           |  |  |  |

|    | 2.2          | Graph   | Processing                                             |  |  |  |

|    | 2.3          | Stream  | ning Graph Processing                                  |  |  |  |

| 3  | PD           | ES-A:   | Parallel Discrete Events Simulation Accelerator        |  |  |  |

|    | 3.1          | Paralle | el Discrete Event Simulation                           |  |  |  |

|    | 3.2          | PDES    | -A Design Overview                                     |  |  |  |

|    |              | 3.2.1   | Design Goals                                           |  |  |  |

|    |              | 3.2.2   | General Overview                                       |  |  |  |

|    |              | 3.2.3   | Event Queue                                            |  |  |  |

|    |              | 3.2.4   | Event Processor                                        |  |  |  |

|    |              | 3.2.5   | Event scheduling and processing                        |  |  |  |

|    |              | 3.2.6   | Event History                                          |  |  |  |

|    |              | 3.2.7   | Rollback and Cancellation                              |  |  |  |

|    | 3.3          | Imple   | mentation Overview                                     |  |  |  |

|    |              | 3.3.1   | Design Language and Application Modeling               |  |  |  |

|    | 3.4          | Perfor  | mance Evaluation                                       |  |  |  |

|    |              | 3.4.1   | Performance and Scalability                            |  |  |  |

|    |              | 3.4.2   | Rollbacks and Simulation Efficiency                    |  |  |  |

|   |                                                             | 3.4.3<br>3.4.4 | Breakdown of event processing time             | 41<br>43 |  |  |

|---|-------------------------------------------------------------|----------------|------------------------------------------------|----------|--|--|

|   |                                                             | 3.4.5          | Effect of event processing time                | 44       |  |  |

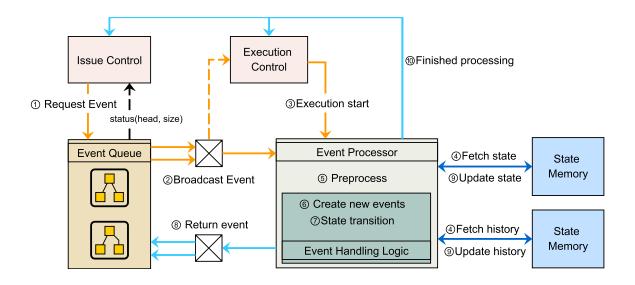

| 4 | Dec                                                         | ouple          | d Datapath for PDES-A                          | 46       |  |  |

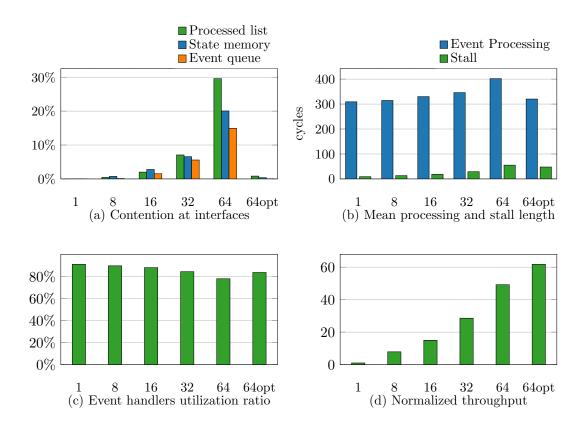

|   | 4.1                                                         | Datap          | eath Optimization via structure partitioning   | 47       |  |  |

|   |                                                             | 4.1.1          | Decoupled Event Processing Flow                | 50       |  |  |

|   |                                                             | 4.1.2          | Operational Characteristics                    | 52       |  |  |

|   | 4.2                                                         | Comp           | arison With ROSS                               | 53       |  |  |

|   | 4.3                                                         |                | rce Utilization Analysis and Scaling Estimates | 56       |  |  |

| 5 | Eve                                                         | nt-Dri         | iven Execution Model for Graph Processing      | 60       |  |  |

|   | 5.1                                                         | Conve          | entional Computation Models                    | 61       |  |  |

|   | 5.2                                                         | Delta-         | -based Accumulative Processing                 | 63       |  |  |

|   | 5.3                                                         | Overv          | iew of Event-Driven Graph Processing           | 66       |  |  |

|   |                                                             | 5.3.1          | Event-Processing Considerations                | 66       |  |  |

|   |                                                             | 5.3.2          | Application Mapping                            | 71       |  |  |

| 6 | GraphPulse: an Asynchronous Graph Processing Accelerator 73 |                |                                                |          |  |  |

|   | 6.1                                                         | Graph          | Pulse Architecture                             | 74       |  |  |

|   |                                                             | 6.1.1          | Event Management                               | 75       |  |  |

|   |                                                             | 6.1.2          | Event Scheduling and Termination               | 77       |  |  |

|   |                                                             | 6.1.3          | In-Place Coalescing Queue                      | 78       |  |  |

|   |                                                             | 6.1.4          | Event Processors and Routing Network           | 82       |  |  |

|   |                                                             | 6.1.5          | GraphPulse Execution Flow                      | 84       |  |  |

|   |                                                             | 6.1.6          | Scaling to Larger Graphs                       | 85       |  |  |

|   | 6.2                                                         | Graph          | Pulse Optimizations                            | 87       |  |  |

|   |                                                             | 6.2.1          | Vertex Property Prefetching                    | 87       |  |  |

|   |                                                             | 6.2.2          | Efficient Event Generation                     | 89       |  |  |

|   | 6.3                                                         | Exper          | imental Evaluation                             | 89       |  |  |

|   |                                                             | 6.3.1          | Experimental Methodology                       | 90       |  |  |

|   |                                                             | 6.3.2          | Performance and Characteristics                | 93       |  |  |

|   |                                                             | 6.3.3          | Hardware Cost and Power Analysis               | 97       |  |  |

| 7 | Inci                                                        | ement          | tal Recomputation of Streaming Graphs          | 99       |  |  |

|   | 7.1                                                         | Stream         | ming Graph Analytics                           | 101      |  |  |

|   |                                                             | 7.1.1          | Incremental Query Evaluation                   | 102      |  |  |

|   | 7.2                                                         | JetStr         | ream Design Overview                           | 105      |  |  |

|   |                                                             | 7.2.1          | Event-based Processing in GraphPulse           | 105      |  |  |

|   |                                                             | 7.2.2          | Streaming Graph Computation Objective          | 107      |  |  |

|   |                                                             | 7.2.3          | Event Representation of Graph Mutation         | 108      |  |  |

|   |                                                             | 7.2.4          | Impacted Vertex Detection and Recovery         | 112      |  |  |

|   |                                                             | 7.2.5          | Recomputation of the Mutated Graph             | 115      |  |  |

| 8                | Jets   | Stream: a Streaming Graph Processing Accelerator 1 | 19          |

|------------------|--------|----------------------------------------------------|-------------|

|                  | 8.1    | Event Management                                   | 121         |

|                  | 8.2    | Event Scheduler                                    | 123         |

|                  | 8.3    | Event Processing Engine                            | 124         |

|                  | 8.4    | Stream Processing Modules                          | 125         |

|                  | 8.5    | JetStream Execution Flow                           | 126         |

|                  | 8.6    | Graph Representation and Partition                 | 127         |

|                  | 8.7    | Optimizations                                      | 129         |

|                  |        | 8.7.1 Value Aware Propagation (VAP)                | 129         |

|                  |        | 8.7.2 Dependency Aware Propagation (DAP)           | 130         |

|                  | 8.8    | Evaluation                                         | 132         |

|                  |        | 8.8.1 Experimental Setup                           | 133         |

|                  |        | 8.8.2 Performance and Characteristics              | 135         |

|                  |        | 8.8.3 Hardware Cost and Power Analysis             | 141         |

| 9                | Cor    | nclusions and Future Work 1                        | 43          |

| $\mathbf{B}^{i}$ | ibliog | graphy 1                                           | L <b>47</b> |

# List of Figures

| 3.1  | Block diagram of basic control and data flow in a PDES system                     | 25 |

|------|-----------------------------------------------------------------------------------|----|

| 3.2  | The P-heap data structure [11]                                                    | 26 |

| 3.3  | Multiple event issue priority queue                                               | 28 |

| 3.4  | Simplified timeline representation showing scheduling of events in the system.    | 30 |

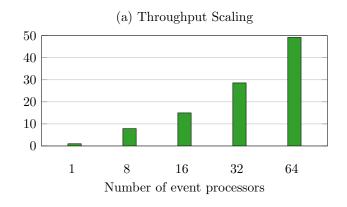

| 3.5  | Effect of variation of number of cores on (a) throughput and (b) percentage       |    |

|      | of core utilization for 256 LP and 512 initial events in PDES-A                   | 37 |

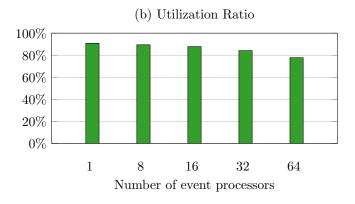

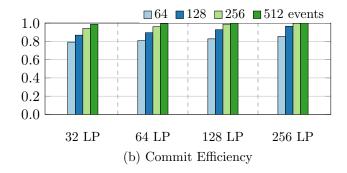

| 3.6  | (a) Event processing throughput (events/cycle) and (b) Ratio of number of         |    |

|      | committed events to number of total processed events for different number         |    |

|      | of LPs and initial events on 64 event processors                                  | 39 |

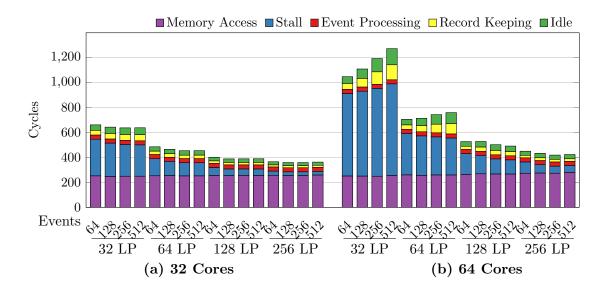

| 3.7  | Breakdown of time spent by the event processors on different tasks to process     |    |

|      | an event using (a) 32 event processors and (b) 64 event processors with           |    |

|      | respects to different number of LPs and initial event counts                      | 40 |

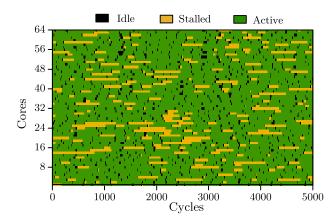

| 3.8  | Timeline demonstrating different states of the cores for during a 5000 cycles     |    |

|      | frame of the simulation                                                           | 41 |

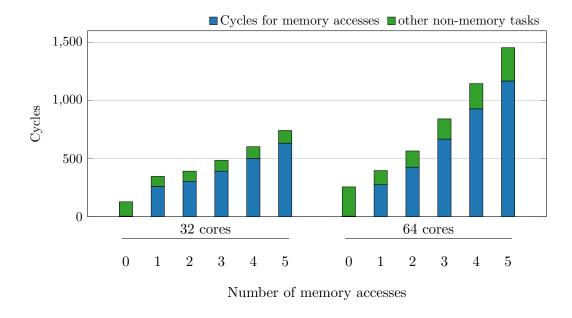

| 3.9  | Effect of number/size of state memory access on event processing time             | 43 |

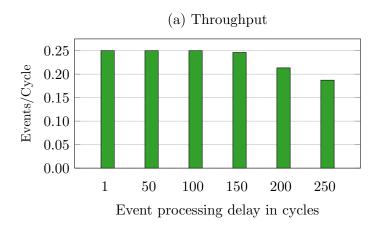

| 3.10 | Effect of variation of processing delays (in cycles) on (a) throughput, (b)       |    |

|      | ratio of core utilization for 64 event processors with 256 LP and 512 initial     |    |

|      | events                                                                            | 45 |

|      |                                                                                   |    |

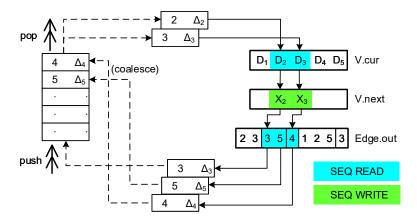

| 4.1  | Overview of an event processing cycle                                             | 50 |

| 4.2  | Effects of optimized dataflow and concurrent resource access on PDES-A ac-        |    |

|      | celerator performance compared to the baseline engine with different number       |    |

|      | of event handlers                                                                 | 52 |

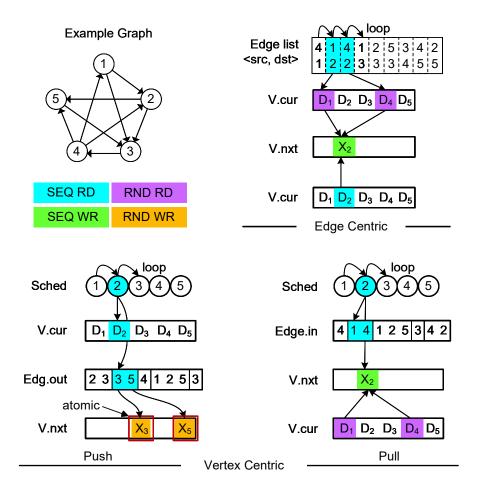

| 5.1  | Data access patterns for conventional graph processing models: Edge Centric       |    |

| 5.1  | and Vertex Ordered ( <i>Push</i> and <i>Pull</i> directions) processing paradigms | 61 |

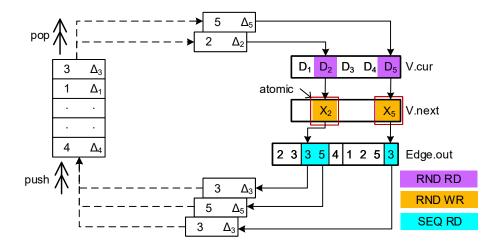

| 5.2  | Data access pattern in event-driven approach with a FIFO event-queue              | 68 |

| 0.2  | Dava access particin in event-driven approach with a 1110 event-queue             | UC |

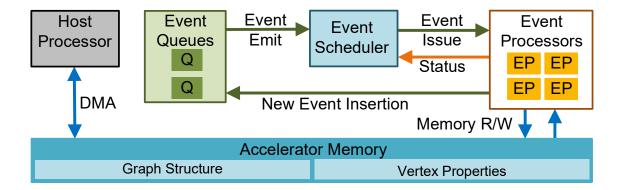

| 6.1  | Overview of GraphPulse Design                                                     | 74 |

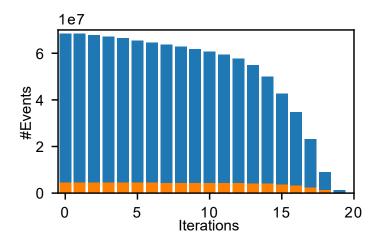

| 6.2  | Total events produced (blue) and remaining after coalescing (orange) with         |    |

|      | the event-driven execution model in GraphPulse                                    | 75 |

| 6.3  | Data access pattern in event-driven approach with coalescing & sorting            | 76 |

|      |                                                                                   |    |

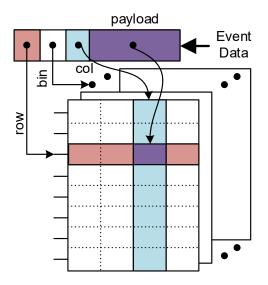

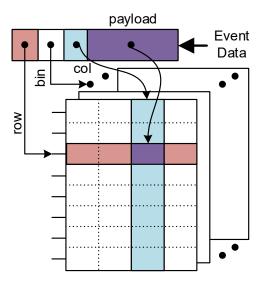

| 6.4         | An event is direct-mapped to a cell in a queue bin. Bits in the destination vertex Id is used to find cell mapping                                                                                                            | 79  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.5         | In-place coalescing of events and retrieval in the direct mapped event storage                                                                                                                                                | 19  |

|             | (for PageRank)                                                                                                                                                                                                                | 79  |

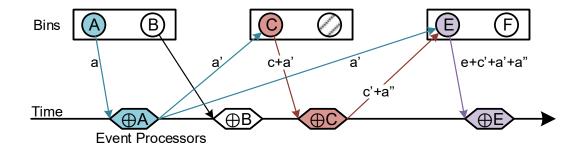

| 6.6         | Look-ahead: Vertex contributions are compounded across iterations in the event-driven model                                                                                                                                   | 81  |

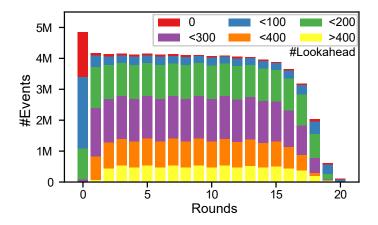

| 6.7         | Degree of lookahead in events processed in each round                                                                                                                                                                         | 82  |

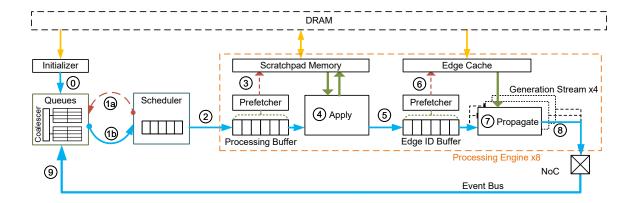

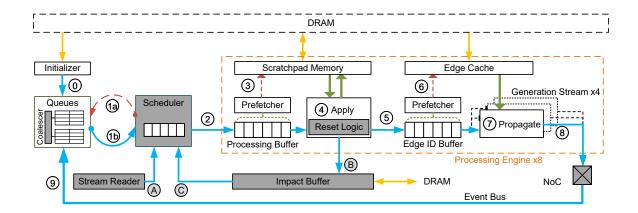

| 6.8         | Detailed GraphPulse datapath. Blue arrows show data flow, red arrows indicate control signals, green and yellow arrows represent on-chip and off-chip memory transfers respectively                                           | 84  |

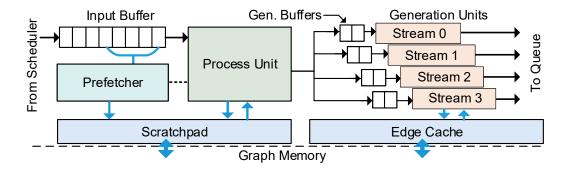

| 6.9<br>6.10 | Optimization of event processing and generation in GraphPulse                                                                                                                                                                 | 87  |

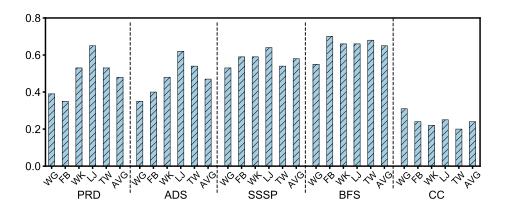

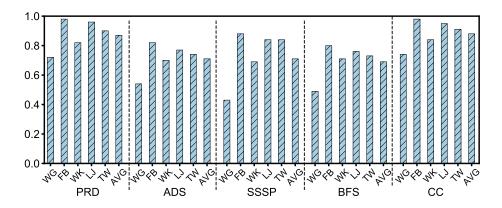

|             | Section 6.1.6                                                                                                                                                                                                                 | 94  |

|             | Total off-chip memory accesses of GraphPulse normalized to Graphicionado. Fraction of off-chip data transmissions that resulted in useful computations                                                                        | 95  |

|             | in GraphPulse                                                                                                                                                                                                                 | 95  |

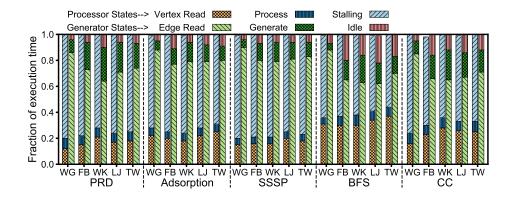

| 6.13        | Cycles spent by an event in each execution stage, shown chronologically from bottom to top                                                                                                                                    | 96  |

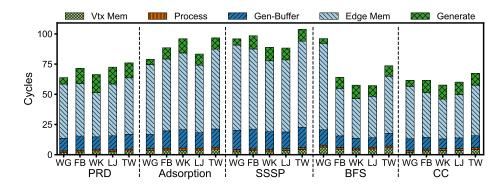

| 6.14        | Time breakdown for the GraphPulse processors (left-bar) and generation units (right-bar)                                                                                                                                      | 97  |

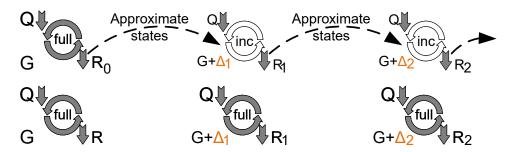

| 7.1         | Query evaluation on a streaming graph using an incremental algorithm (top)                                                                                                                                                    |     |

| 7.2         | and static algorithm (bottom)                                                                                                                                                                                                 | 101 |

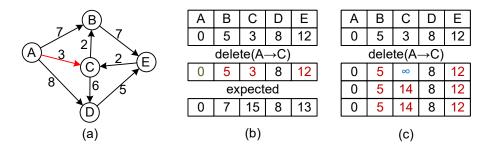

|             | vertex                                                                                                                                                                                                                        | 102 |

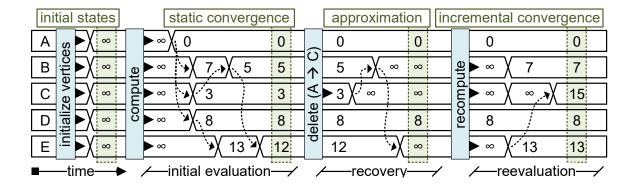

| 7.3         | Conceptual timeline showing vertex values over time through initial evaluation, recovery, and reevaluation phases for SSSP on the example graph in                                                                            |     |

| 7.4         | Figure. 7.2                                                                                                                                                                                                                   | 104 |

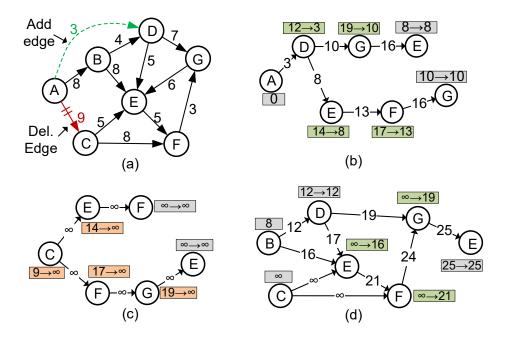

|             | example graph. (b) Propagation and updates from the insertion of edge $A \to D$ in the graph. (c) Propagation of deletes and resetting impacted                                                                               |     |

|             | vertices due to the deletion of edge $A \to C$ in the graph. (d) Recovery of approximate state after request events are processed                                                                                             | 108 |

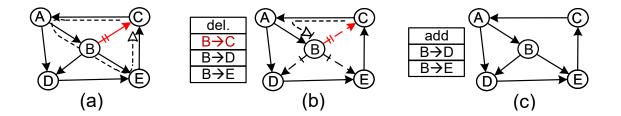

| 7.5         | Showing an edge deletion for accumulative algorithms: (a) initial graph with $B\rightarrow C$ to be deleted; (b) intermediate representation; (c) mutated graph                                                               | 118 |

| 8.1         | Detailed JetStream datapath. Blue arrows show data flow, red arrows indicate control signals, green and yellow arrows represent on-chip and off-chip memory transfers respectively. Shaded modules are now or modified in let |     |

|             | memory transfers respectively. Shaded modules are new or modified in Jet-Stream                                                                                                                                               | 125 |

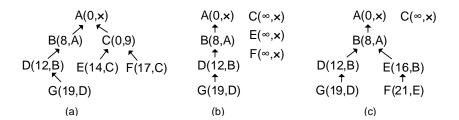

| 8.2         | Dependency tree for the example in Figure 7.4: (a) before deletion; (b) after reset; (c) after reevaluation for the deleted edge $A\rightarrow C$                                                                             | 129 |

|             |                                                                                                                                                                                                                               | _   |

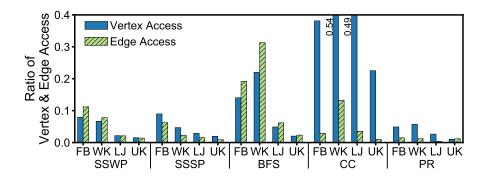

| 8.3 | Number of vertex and edge accesses in JetStream normalized to GraphPulse.  | 135  |

|-----|----------------------------------------------------------------------------|------|

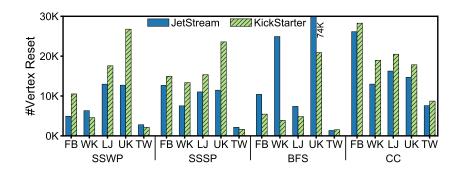

| 8.4 | Number of vertices reset by 30K edge deletions                             | 137  |

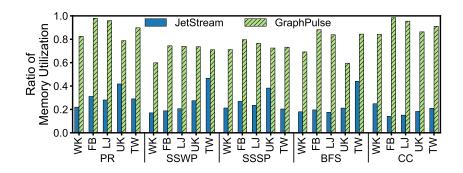

| 8.5 | Utilization of off-chip memory transfers in JetStream                      | 138  |

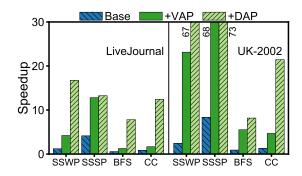

| 8.6 | Speedup over GraphPulse for Baseline JetStream, VAP and DAP optimizations  | .139 |

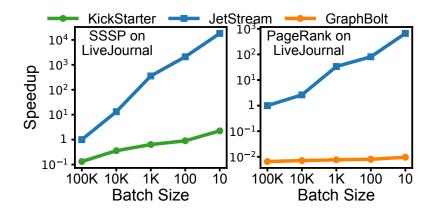

| 8.7 | Sensitivity to batch size. Run-time shown as speedup over JetStream with   |      |

|     | 100K batch                                                                 | 140  |

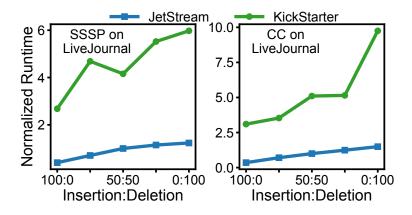

| 8.8 | Run-time sensitivity to batch composition. Run-time is normalized to 50:50 |      |

|     | composition on JetStream                                                   | 140  |

# List of Tables

| 4.1 | Summary of the configurations used for performance comparison of ROSS                                                                           |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | and PDES-A using Phold model                                                                                                                    | 55  |

| 4.2 | Comparative analysis of PDES simulation performance for Phold model on                                                                          |     |

|     | ROSS and PDES-A                                                                                                                                 | 56  |

| 4.3 | FPGA resource utilization for Optimized Datapath PDES-A                                                                                         | 57  |

| 5.1 | Functions for mapping algorithm to GraphPulse                                                                                                   | 71  |

| 6.1 | Device configurations for software framework evaluation and GraphPulse                                                                          |     |

|     | with optimizations                                                                                                                              | 91  |

| 6.2 | Graph workloads used in the evaluations of GraphPulse                                                                                           | 92  |

| 6.3 | Power and area of the GraphPulse accelerator components                                                                                         | 98  |

| 8.1 | Experimental configurations for JetStream                                                                                                       | 133 |

| 8.2 | Input graphs used in the experiments for JetStream                                                                                              | 134 |

| 8.3 | Execution time (in ms) per query on JetStream and speedup over full evaluation in GraphPulse(GP), and incremental evaluation in KickStarter(KS) |     |

|     | and $GraphBolt(GB)$                                                                                                                             | 136 |

| 8.4 | Power and area of the JetStream accelerator components                                                                                          | 142 |

### Chapter 1

# Introduction

For years, the growth in high-performance computation capacity was facilitated by the rapid increase in transistor density and clock speed in computer CPUs following the predictions of Moore's Law and Dennard Scaling [27]. However, the laws of physics finally appeared as a barrier to this exponential growth preventing the ability to shrink the transistors anymore than they already were. The end of Dennard Scaling restricts the ability of software to scale the performance using larger and faster processors due to the Dark Silicon effect. As a result, alternative strategies are required to support the rapidly growing computational demands of the modern days. This incentivizes the push towards custom hardware accelerators built for specific application domains. The accelerators can be orders of magnitude more efficient in terms of performance and power since the complex pipelines of modern CPUs can be streamlined and trimmed down. In addition, a large portion of the industry workloads is a small set of repetitive tasks that can benefit significantly from specialized accelerator units to execute them. The recent drive for integrating reconfigurable

accelerators in the cloud, as seen in the Microsoft Catapult Project [78] and Amazon F1 FPGA instances [45], recognizes the industry demand for application-specific accelerators.

This dissertation explores the advantages of using event-driven execution to accelerate irregular applications in hardware. An event-driven system records an update task as an event in a queue. It only performs the task when the event is scheduled. Such systems visit a state only when necessary, thus, reducing the workload of the system. Furthermore, the event-based model transforms the dynamic dependence of irregular applications into order among the events to preserve correctness. Then, synchronization complexity is reduced by controlling the flow of events in the system to enhance parallelism. Additionally, finegrained control over the state access pattern is possible by manipulating the order of events processing. Thus, memory bandwidth can be optimized by scheduling the events to execute the tasks in a memory-access-friendly pattern. Event-driven execution, however, does not achieve expected performance in conventional shared-memory systems because the task processing throughput becomes dependent on the performance of an ordered queue structure containing the events. Such queues are challenging to implement with high performance in software, and event storage becomes the critical bottleneck of the system.

Nevertheless, it is possible to overcome this challenge in hardware accelerators with hardware primitives for robust event storage and transmission to achieve a high degree of parallelism. The hardware acceleration of these applications offers two primary advantages.

• Low-latency and high-bandwidth on-chip communication: Hardware platforms such as FPGAs support fast high-bandwidth on-chip communication, substantially alleviating the communication bottleneck limiting the performance of irregular applications [107].

• Specialized high-bandwidth datapaths: General-purpose processing provides high flexibility but at the price of high overhead and a fixed datapath. A specialized accelerator, in contrast, can more efficiently implement a required task without unnecessary overheads of fetching instructions and moving data around a general datapath. Moreover, specialized hardware allows high parallelism limited only by the number of processing units and the communication bandwidth available between them, as well as the memory bandwidth available to the chip.

We approach the study of event-driven accelerator design from three perspectives. First, we investigate the **feasibility**, **profitability**, **and technical limitations** of building an event-driven system using hardware. Afterward, we analyze the **adaptability** of such systems to different application domains that are not typically event-driven. Finally, we explore the **expansibility** of the event-driven execution model for supporting complex applications with multiple types of tasks and multiple phases of computations. Our study confirms that event-driven execution can be a beneficial technique for accelerating diverse application classes in hardware.

We examine three irregular applications – Parallel Discrete Event Simulation (PDES), Asynchronous Graph Processing, and Streaming Graph Analytics – to investigate and demonstrate the methodologies for designing accelerators using the event-driven execution model. Parallel Discrete Event Simulation is an inherently event-driven application. We establish the sustainability of a hardware architecture for event-driven execution using Parallel Discrete Event Simulation as the target application. Graph Processing, on the other hand, traditionally uses the iterative execution method. We demonstrate the tech-

niques and considerations for the algorithmic conversion of an irregular application (Graph Processing) to execute in an event-driven approach and develop an architecture to support this execution model. Finally, we illustrate how the event-driven model can accommodate multi-phased computation and diverse tasks to support complex application domains by extending the execution model for streaming graph analysis.

In the remainder of this chapter, we describe the motivations for this dissertation and the limitations of existing technologies in Section 1.1. We continue to present the contributions of this dissertation in Section 1.2, Finally, we describe the organization of this dissertation in Section 1.3.

### 1.1 Motivation: Challenges in Irregular Applications

While computer architects quickly adopted multicore and multithreaded architectures to subvert the limitation in processor speed using parallel processing, this adds new challenges for scaling the performance of high-performance workloads. The increasing gap between the processing speed and memory bandwidth becomes the primary bottleneck in processing performance in these systems. Historically, the DRAM memory has enjoyed rapid growth in capacity, while the bandwidth increased at a much lower rate and the DRAM latency increased nominally. The high capacity of DRAM memory enables modern systems to undertake huge workloads, but the performance suffers because of long latency and limited bandwidth. If memory latency and bandwidth become insufficient to provide processors with enough instructions and data to continue computation, processors will effectively always be stalled waiting on memory. The trend of placing more and more cores

on-chip exacerbates the situation since each core enjoys a relatively narrower channel to shared memory resources. The problem is commonly referred to as *memory wall*, and it is particularly acute in highly parallel systems.

In modern systems, these bottlenecks are alleviated using speculative execution and large cache hierarchies. Many applications have little control flow divergence, predictable execution pattern, and high spatial or temporal locality receive good performance boost from these techniques. However, some applications, dubbed Irregular Applications have characteristics that prevent them from getting any significant improvements from these techniques. Irregular applications have pointer-based indirection in their data structures resulting in unpredictable memory access patterns and dynamic data-dependent control-flow. Many critical HPC applications such as graph algorithms, machine learning, and database operations fall in this category. These applications help derive actionable intelligence from highly connected data of massive size, and they depend on highly dynamic, multidimensional data structures such as graphs, trees, and grids.

In irregular applications, pointer-based memory indirections lead to data accesses unrelated in any temporal or spatial sense. Such a lack of locality limits the performance of modern processor architectures built on deep memory hierarchies and prefetching to mitigate latencies. Moreover, irregular data structure-based applications usually have limited arithmetic intensity, as most of the computation time is spent navigating the data structures. Thus, modern processors and accelerators designed to maximize floating-point operations per memory access are a poor fit for these applications. These applications also have large amounts of data parallelism as many data values can be explored in parallel.

However, the dynamic data dependence between tasks makes it difficult to exploit this parallelism. Moreover, they often require fine-grained synchronization as concurrent threads may compete to modify the same data elements. These irregular applications become the prime candidates for hardware acceleration. The dedicated architecture can re-purpose or discard the cache hierarchy to optimize memory access and use specialized hardware primitives to establish a fast and effective synchronization mechanism. As a result, significant parallelism and performance gain can be expected from the accelerator.

### 1.2 Contributions of the Dissertation

We have designed several computation models and accelerators for different applications during our research in the acceleration of irregular applications. These computation models demonstrate techniques for efficient event-driven execution and serve as pointers for adapting iterative applications into the event-driven model. We also built three accelerators demonstrating the performance potential of the event-driven method.

#### 1.2.1 PDES-A: Parallel Discrete Event Simulation Accelerator

PDES-A is the first hardware accelerator for Parallel Discrete Event Simulation. It includes a hardware priority queue capable of fast insertion and retrieval. This pipelined priority queue allows PDES-A to support many processing cores and achieve high throughput. In addition, we relax synchronization by employing an optimistic execution with a rollback mechanism for recovery. PDES-A provides excellent scalability for PDES Model *Phold* for up to 64 concurrent event processors. Our baseline prototype outperforms a sim-

ilar simulation on a 12-core 3.5GHz Intel Core i7 CPU by 2.5x. Afterward, we describe re-designed PDES-A engines that relieve contention by partitioning all shared structures such as event and state queues into multiple substructures. It also incorporates a decoupled datapath that significantly relaxes synchronization and improves the scalability of the system. This optimized design results in another 25% improvement in throughput. The optimized accelerator outperforms a 12-core Intel Core i7 by 3.2x while consuming less than 15% of the power.

### 1.2.2 GraphPulse: an Accelerator for Graph Processing

Our graph processing accelerator, GraphPulse, is the first asynchronous event-driven graph processing accelerator. GraphPulse alleviates several performance challenges faced in traditional software graph processing while bringing the benefits of hardware acceleration to graph computations. GraphPulse's event-driven model decouples computations, ergo memory accesses, from communications. In this model, memory accesses are only necessary during vertex updates. As a result, one of the primary sources of random memory access is eliminated. Moreover, synchronization is simplified by having the accelerator serialize events destined to the same vertex; thus, the synchronization overhead of traditional graph processing is reduced. At any point in time, the events present in the system naturally correspond to the active computation. Thus the bookkeeping overhead of tracking the active subset of the graph is also masked.

Supporting this model in software is difficult due to the high overheads of generating, communicating, managing, and scheduling events. GraphPulse architecture supports events in the hardware queue and routes them using a fast on-chip communication network.

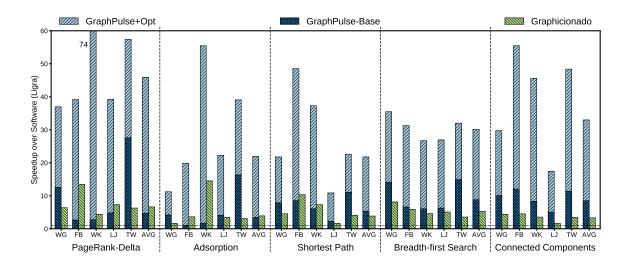

Thus, it essentially eliminates event-related overheads and making the model more efficient than software implementations. GraphPulse performs asynchronous graph processing, resulting in substantial speedups due to greater exploitation of parallelism and faster convergence. In addition to this, it introduces coalescing of events to control event population and allow transaction safety. We enhance the model with a prefetcher and smart scheduler to achieve high throughput. This design substantially outperforms software frameworks due to its efficient memory usage and bandwidth utilization. GraphPulse outperforms software frameworks on a 12-core Intel Xeon system by 28x with about 300x better energy efficiency.

#### 1.2.3 JetStream: Accelerator for Streaming Graph Analytics

The last accelerator we built as part of this dissertation is JetStream, an accelerator for performing incremental evaluations of streaming graphs. Graphs are constantly evolving in real-world applications. Restarting a query from scratch on a mutated graph is wasteful because the changes usually modify only a small subset of the graph. Thus, much of the computation performed during reevaluation is redundant. Streaming graph systems support incremental update of query results to address this inefficiency, resulting in order of magnitudes speedups over cold-start recomputation. JetStream builds on GraphPulse and uses the same event-driven asynchronous processing model. It extends the event-driven graph computation model to support incremental computation for edge addition, deletion, and updates. JetStream proposes an event-driven approach to reset and recover after edge deletions for monotonic graphs. JetStream achieves 18x speedup over software graph processing framework, GraphBolt. It also performs 13x better than compared to a complete recomputation of the streaming graphs in GraphPulse.

### 1.3 Organization of the Dissertation

We begin the rest of the dissertation by reviewing important literature related to the applications considered in our work. Then, we describe the three accelerators that we built in the following chapters. In Chapter 3, we present the design of a Parallel Discrete Event Simulation accelerator, PDES-A. We explore the fundamental design considerations and a baseline architecture for the accelerator in this design. We analyze the limitations of the basic architectures that are resolved using a redesigned datapath in Chapter 4. This chapter describes the optimizations for PDES-A and our techniques for designing a decoupled datapath for the event-driven model.

Next, we present the limitations of conventional graph processing systems and the development of event-driven methods to alleviate them in Chapter 5. This chapter elaborates on the design considerations for event-driven execution and illustrates the transformation of an iterative algorithm to an event-based model. We describe the architecture of the GraphPulse accelerator in Chapter 6. This chapter also describes the evaluation of the accelerator against state-of-the-art software and hardware graph analytics frameworks.

The last part of this dissertation describes the design of JetStream, an accelerator for streaming graph analytics in Chapter 7. We present the challenges of incremental computation and how the event-driven model can be extended to perform incremental evaluation of streaming graphs. It is followed by the description of JetStream architecture that implements this extended model in Chapter 8.

Finally, we conclude with a brief summary of our research and potential future works in Chapter 9.

## Chapter 2

### Related Work

In this chapter, we present previous works relevant to this dissertation. We organize the relevant literature into three sections. The first section reviews literature related to the techniques and software frameworks for parallel discrete events simulation. Then, we describe recent works on software and hardware-based graph processing systems. Finally, we highlight crucial works in the field of streaming graph analytics.

### 2.1 Parallel Discrete Event Simulation

Discrete Events Simulation is heavily used in real-world simulations and performance evaluations where systems change in discrete states. A wide range of domains extending from military simulations and war-gaming [34, 42] to epidemiology and molecular biology [32, 114] uses discrete event simulation for studying vast simulation space, which is prohibitively expensive with traditional time-stepped simulation methods. PDES is an important tools for digital design simulation [63] industry as well.

The parallel Discrete Event Simulation community extensively uses Phold [34] models as a synthetic benchmark for profiling and evaluating PDES systems. The Phold model consists of a model where an event is generated for a random destination whenever a logical element receives an event. It is a communication-centric model to expose the communication robustness of the simulation system. There is another model [55] that utilizes real-world simulation profiles to generate more accurate and realistic synthetic PDES models that are more parameterizable and customizable.

In recent years, researchers have developed and analyzed PDES simulators on various parallel and distributed platforms as these platforms have continued to evolve. The widespread adoption of both shared and distributed memory cluster environments has motivated the development of PDES kernels optimized for these environments, such as GTW[25], ROSS[18] and WarpIV[95]. These systems can be conservative or optimistic simulators that employ a diverse range of techniques for checkpointing, reverse computation, implementations of GVT, and anti-messages. Apart from the works on new simulation frameworks, there are many individual works that experiment on optimizations for a particular system or architecture. For example, Jagtap et al. [49, 106] proposed and analyzed several optimizations for multi-threaded PDES simulators to improve scalability on shared-memory platforms such as Intel Core-i7 and such. One of the notable contributions of their work involves the conversion of an MPI-driven strategy to a shared-memory threaded strategy.

Other PDES implementations explore various upcoming architectures. For example, Jagtap et al. studies the performance of PDES [49] on the many-core Tilera architecture. Their result displays good scalability, and the architecture proves capable of sustaining high

throughput even under a heavy workload. A study of PDES in Intel Many Integrated Core (MIC) system [20] suggests that full utilization of the Knights Corner processor's vector units are required to outperform the Xeon host processors. A PDES system designed by Bauer et al. [9] replaces the checkpointing system in ROSS with reverse computation to achieve close to linear speedup, utilizing 128K cores in the IBM Blue Gene Supercomputer. Reverse computation tries to trace backwards the states using the opposite computation of the regular update operation. Thus, it can eliminate the overhead for checkpointing states and maintaining a global time if the computation can be rolled back using reverse computation. Barnes et al. [8] extend the previous work to analyze performance in the Sequoia BlueGene/Q supercomputer with 2 million cores. Their experiments show impressive throughput for PDES with an MPI-driven execution. Several researcher explore the use of GPGPUs to accelerated PDES [76, 97, 77, 19]. In contrast to these effort, very few works considered acceleration of PDES using non-conventional architectures such as FPGAs.

Other optimizations of PDES systems focus on improving the robustness and throughput of the priority queue of the PDES system. For example, the study by Gupta et al. [37] looks at the use of ladder queues for a lock-free event management structure that can substitute the more commonly used linked list-based event queue. This work assumes that the events in a small simulation time window have no dependence and can be issued without sorting in an optimistic simulation system. Optimization to the calendar queue is considerred in [68] to propose a lock-free non-blocking event pool woth O(1) time complexity for both insertion and dequeuing. The event queue structure and its impact on PDES performance have been studied in the context of software implementations [82];

however, it is crucial to understand suitable queue organizations implemented in hardware. Prior work has studied hardware queue structures supporting different features. For example, hardware priority queues offer attractive properties for PDES such as constant-time operation, scalability, low area overhead, and simple hardware routing structures. Simple binary heap-based priority queues are commonly used in hardware-based implementations but require O(log(n)) time for enqueue and dequeue operations. Other options have other drawbacks; for example, Calendar Queues [13] support O(1) access time but are difficult and expensive to scale in a hardware implementation. QuickQ[80] uses multiple dual-ported RAM in a pipelined structure which provides easy scalability and supports constant-time access. However, the access time is proportional to the size of each stage of RAM. Therefore, configuring them to achieve a short access time necessitates many stages, which leads to high hardware complexity.

### 2.2 Graph Processing

The next application, graph processing, is employed in many domains, including social networks [96, 15, 22, 46, 30], web graphs [109], and brain networks [14], to uncover insights from high volumes of connected data. Iterative graph analytics require repeated passes over the graph until the algorithm converges. Since real-world graphs can be massive (e.g., YahooWeb has 1.4 billion vertices and 6.6 billion edges), these workloads are highly memory-intensive. Thus, there has been significant interest in developing scalable graph analytics systems. Some examples of graph processing systems include GraphLab [64], GraphX [36], PowerGraph [35], Galois [74], Giraph [3], GraphChi [60], and Ligra [90].

Maiter [116] is a graph analytics framework for delta-accumulative computation, which is the basis of the event-driven model. Maiter shows the computation model for a distributed systems where vertices communicate only the incremental change in their states, and graph updates incrementally accumulate in vertices to reach the final converged state.

#### **Graph Accelerators**

Template-based graph accelerators process hundreds of vertices in parallel to mask long memory latency [4]. They use hardware primitives for synchronization and hazard avoidance. Swarm [51] allows speculative execution to increase parallelism and support commit and rollback on a many-core architecture so that when tasks proceed speculatively, there is the option to revert with little overhead. This increases the number of concurrent tasks processed for ordered or tree-based algorithms. However, inherent memory access inefficiencies of graph algorithms still persist. Spatial Hints [52] uses application-level knowledge to tag tasks with specific identifiers for mapping them to processing elements which allows better locality and more efficient serialization, thus, addressing the inefficiencies of Swarm. Chronos [1] provides another hardware acceleration framework based on speculative execution. On the other hand, serialization becomes unnecessary after coalescing in GraphPulse since transaction safety is implicitly guaranteed by the execution model and architecture.

Ozdal [75] proposes a graph processing architecture in hardware that takes advantage of a hardware-based commit queue to provide transaction safety in asynchronous graphs. Graphicionado [38], a pipelined architecture, optimizes vertex-centric graph models using a fast temporary memory space. It improves locality using on-chip shadow memory for vertex property updates. Throughput increases due to reduced memory consistency over-

heads and higher memory bandwidth using the temporary storage. However, GraphPulse substantially outperforms Graphicionado due to the advantages of the event-driven model over conventional models. Graph processing systems for FPGAs include ForeGraph [23], Zhou et al. [119, 120] etc.

#### PIM-based solutions

These solutions lower memory access latency and increase performance. Tesseract [2] implements simplified general-purpose processing cores in the logic layer of a 3D stacked memory. Like distributed graph processing, it uses messages to access/update data. GraphPIM [73] replaces atomic operations in the processor with atomic operation capability in Hybrid Memory Cube (HMC) 2.0 to achieve low latency execution of atomic operations. Another solution explores robust partitioning and cross-communication to fit large graphs in 3D stacked memory [113]. There have been other recent works that focus on architectures for PIM-based graph processing, such as GraphP [112], and GraphQ [121]. Our approach has the potential to be advantageous on PIM platforms too, because memory accesses are simplified, and the complex scheduling and synchronization tasks are isolated to the logic layer.

### Tolerating irregular memory accesses

The propagation blocking technique for PageRank [10] temporarily holds contributions in hashed bins in memory, merges contributions to the same vertex, and later replays them to maximize bandwidth utilization and cache reuse. However, it entails the overhead of maintaining bins. Zhou et al. [119, 120] store contributions temporarily to memory and combines them using hardware when possible for the edge-centric model. Due to a large number of edges, there is a substantial increase in random memory writes to temporary bins and small combination windows limit combining. To optimize irregular memory accesses, IMP [110] uses a dynamic predictor for indirect accesses to drive prefetching. HATS [70] proposes a hardware-assisted traversal scheduler for locality-aware scheduling to increase data reuse. RAts [92] memory model exploits commutativity in atomic operations to reduce complexity. In contrast, GraphPulse coalesces the application's computations rather than memory operations and controls the scheduling and frequency of vertex accesses to improve memory access patterns.

### Efficient vertex update handling

Since vertex updates are a crucial bottleneck in a graph-analytics application, some prior works focus on improving the locality and cost of scattering updates to the neighbors. Beamer et al. [10] uses *Propagation Blocking* to accumulate the vertex contributions in cache-resident bins instead of applying them immediately. Later, the contributions are combined and then applied, thus eliminating the need for locking and improving spatial locality. *Propagation Blocking* technique creates perfect spatial locality but fails to utilize potential temporal locality for vertices having many incoming updates since updates are binned and spilled to memory first. Other methods exploit commutative nature of the reduction (apply) operation seen in many graph algorithms to relax synchronization for atomic operations. Coup [111] extends the coherence protocol to apply commutative-updates to local private copies only and reduce all copies on reads. This reduces read and write traffic by taking advantage of the fact that commutative reduction can be unaware of

the destination value. PHI [71] also uses the commutativity property to coalesce updates in private cache and incorporates update batching to apply scatter updates in bulk while reducing the on-chip traffic further. Both PHI and Coup optimize memory updates, but have no fine grain control over the memory access pattern. Like PHI, GraphPulse utilizes commutative property to fully coalesce updates using the specialized on-chip queue. Furthermore, GraphPulse applies these updates at a dataflow-level abstraction to reorder and schedule updates for maximizing spatial locality and bandwidth use.

#### **Dataflow architectures**

GraphPulse bears some similarities to dataflow architectures in that computation flows with the data [98, 57, 24, 44]. The Horizon architecture supports lightweight context switching among a massive number of threads for tolerating memory latency. It heavily relies on the compiler [24] but dynamic parallelism in graph applications is not amenable to similar compiler techniques. The SAM machine [44], which is a hybrid dataflow/von Neumann architecture, employs a highspeed memory (register-cache) between memory and execution units is a better match for graph applications. However, neither of these architectures address issues in graph processing addressed by GraphPulse. Specifically, GraphPulse uses data-carrying events to eliminate random and wasteful memory accesses, coalescing strategy eliminates atomic operations and reduces storage for events, and event queues improve locality and enable prefetching.

### 2.3 Streaming Graph Processing

Taxonomy on streaming graph analytics is not yet well-established and several conventions are observed for streaming graph papers. Most works refer to a graph system where new edges additions or deletions appear over time as streaming graphs. However, these graphs are also referred to as time-evolving [47], dynamic, or continuous [28] in many literatures.

A number of streaming graph frameworks have been developed that are based on the BSP [100] model similar to a software framework like Pregel [65]. Of these frameworks, Kineograph [21], Tornado [89], Naiad [72], and Tripoline [53] are limited to growing graphs (i.e., deletion updates are not allowed). In contrast, Kickstarter [103], GraphBolt [67], and DZiG [66] support both addition and deletion of edges. Our work in this dissertation, JetStream, supports both the addition and deletion of edges.

Streaming graph frameworks employ various techniques for performing incremental computations. Some frameworks put the responsibility on the end-user to write methods for discovering inconsistent vertices after graph mutation is applied. GraphIn [88] and EvoGraph [87] use this technique. The user-defined method detects whenever inconsistency arises in a graph based on the batch of edge updates and schedules the updated vertices for recomputation. GraphBolt [67], and KickStarter [103] on the other hand, automatically detects the affected vertices using a dependence tracking technique built into their systems. There is a difference between the targeted class of graph algorithms between GraphBolt and KickStarter. KickStarter targets a class of algorithms that have monotonic properties and selects a single edge update to set the property of a vertex. GraphBolt, on the other hand,

proposes a dependency tracking technique that works on graph algorithms of iterative nature and accumulative update functions. GraphInc [16] uses a memoization-based technique to support incremental evaluation on iterative graphs. This technique attempts to preserve the states of all computations performed and attempts to reuse the preserved states to answer a graph query quickly. Other frameworks, such as KineoGraph [21] maintain a snapshot of the graph states at repeated intervals and recompute the differences in the snapshot to identify the part of the graph that needs recomputation. This strategy works even when vertex update computations are not minimalistic or deterministic.

There are also designs of graph representations to support high-throughput graph updates, such as Aspen [29], STINGER [31], and Version Traveller [54]. Other works handling changing graphs include GraphTau [48], Vora et al. [102], Chronos [40]. However, these works consider scenarios in which historical data is being analyzed, i.e., graph versions are available a priori. GraSU [108] provides the first FPGA-based high-throughput graph update library for dynamic graphs.

## Chapter 3

## PDES-A: Parallel Discrete Events

# Simulation Accelerator

In this section, we introduce a baseline design targeted to run a PDES system in an FPGA. The design focuses on the development of a high performance pipelined queue with constant time insertion and dequeue to facilitate maximum parallelism in the accelerator. It provides a simple datapath with all the components required for a PDES engine.

### 3.1 Parallel Discrete Event Simulation

A discrete event simulation (DES) models the behavior of a system that has discrete state changes. This is in contrast to the more typical time-stepped simulations where the complete state of the system is computed at regular intervals in time. DES has applications in many domains such as computer and telecommunication simulations, war-gaming/military simulations, operations research, epidemic simulations, and many more.

PDES leverages the additional computational power and memory capacity of multiple processors to increase the performance and capacity of the simulation, allowing the simulation of larger, more detailed models and the consideration of more scenarios in a shorter amount of time [33].

In a PDES simulation, the simulation objects are partitioned across a number of logical processes (LPs) that are distributed to different Processing Elements (PEs). Each PE executes its events in simulation time order (similar to DES). Each processed event can update the state of its object, and possibly generate future events. Maintaining correct execution requires preserving time stamp order among dependent events on different LPs. If a PE receives an event from another PE, this event must be processed in time-stamped order for correct simulation.

To ensure correct simulation, two synchronization algorithms are commonly used: conservative and optimistic synchronization. In conservative simulation, PEs coordinate with each other to agree on a lookahead window in time where events can be safely executed without compromising causality. This synchronization imposes an overhead on the PEs to continue to advance. In contrast, optimistic simulation algorithms such as Time Warp [50] allow PEs to process events without synchronization. As a result, it is possible for an LP to receive a straggler event with a time stamp earlier than their current simulation time. To preserve causality, optimistic simulators maintain checkpoints of the simulation, and rollback to a state in the past earlier than the time of the straggler event. The rollback may require the LP to cancel out any event messages it generated erroneously using antimessages. This approach uses more memory for keeping checkpoint information, which need

to be garbage collected when they are no longer needed to bound the dynamic memory size.

A Global Virtual Time (GVT) algorithm is used to identify the minimum simulation time that all LPs have reached: checkpoints with a time lower than the GVT can be garbage collected, and events earlier than the GVT may be safely committed.

## 3.2 PDES-A Design Overview

FPGAs are progressing quickly in terms of both capabilities and integration with computing platforms making them increasingly accessible to programmers. However, concerns regarding longer development time and different development tools, and lack of flexibility and portability are significant impediments to FPGA adoption. Considering these concerns, our goal is to enable simulation of different applications within an easy-to-use framework. An interesting characteristic of PDES simulation algorithms is that, despite the irregular nature of the dependencies, the algorithm itself has a relatively clean and straightforward execution semantics, iterating over the event list to schedule events, processing these events, and then scheduling any events that result from their execution. Most of the complexity lies in the data structures to manage the event lists and those for handling synchronization and causality, which are common to any PDES application. In contrast, application-specific event processing often is computationally and logically contained, and for many simulation models, they are simple. For example, the Simian project [85] shows that a completely functional PDES engine can be implemented in less than 500 lines of python code. An FPGA-based PDES engine can leverage these properties to make it modular and scalable so that experts in any domain can simulate their application models by simply defining the state transition and event processing logic, not requiring hardware development expertise.

In this paper, we present an overview of the unit PDES accelerator (PDES-A), the building block of our PDES accelerator. Each PDES-A accelerator is a tightly coupled high-performance PDES simulator in its own right. However, hardware limitations such as contention for shared event and state queue ports, local interconnection network complexity, and bandwidth limit restrict the scalability of this tightly coupled design approach. These properties suggest a design where multiple interconnected PDES-A accelerators together work on a large simulation model, and exploiting the full available FPGA resources. In this paper, we explore and analyze only PDES-A, and not the full architecture consisting of many PDES-A accelerators.

In an FPGA implementation, event processing, communication, synchronization, and memory access operations occur in a way different from how these operations occur on general purpose processors. Therefore, both performance bottlenecks and optimization opportunities differ from those in conventional software implementations of PDES. We developed a baseline implementation of PDES-A and used it to identify performance bottlenecks. We then used these insights to develop improved versions of the accelerator. We describe our design and optimizations in this section.

#### 3.2.1 Design Goals

PDES-A provides a modular framework where various components can be adjusted independently to attain the most effective data path flow control across different PDES models. Since the time to process events in different models will vary, we designed an

event-driven execution model that does not make assumption about event execution time. We decided to implement an optimistically synchronized simulator to allow the system to operate around the large memory access latencies. However, the tight coupling within the system should allow us to control the progress of the simulation and naturally bound optimism. We avoided any model specific tuning to retain generality of the accelerator.

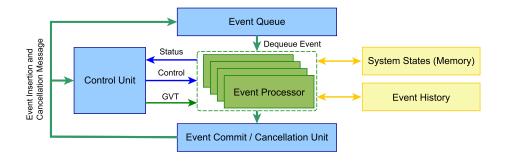

The simulator is organized into four major components: (1) Event Queue: stores the pending events; (2) Event Processors: custom datapaths for processing the event tasks in the model; (3) System State Memory: holds relevant system state, including checkpointing information; (4) and the Controller: it coordinates all aspects of operation. The first three components correspond to the same functionality in traditional PDES engines in any discrete event simulator, and the last one oversees the event processors to ensure correct parallel operation and communication.

Communication between different components uses message passing. We currently support three message types: Event messages, anti-messages, and GVT messages. These three message types are the minimum required for an optimistic simulator to operate, but additional message types could be supported in the future to implement optimization, or to coordinate between multiple PDES-A units.

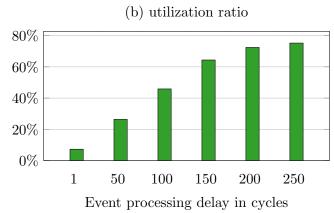

#### 3.2.2 General Overview

Figure 3.1 shows the major components of PDES-A and their interactions. The event queue contains a list of all the unprocessed events sorted in ascending order of their timestamp. Event processors receive event messages from the queue. After processing

Figure 3.1: Block diagram of basic control and data flow in a PDES system

events, additional events that may be generated are sent and inserted into the event queue for scheduling. The system needs to keep track of all the processed events and the changes made by them until it is guaranteed that the events will not be rolled back. When an event is received for processing, the event processor checks for any conflicting events from the event history. Anti-messages are generated when the event processor discovers that erroneous events have been generated by an event processed earlier. Since the state memory is shared, a controller unit is necessary to monitor the event processors for possible resource conflict and manage their correct operation. Another integral function of the control unit is the generation of GVT which is used to identify the events and state changes that can be safely committed. The control unit computes GVT continuously and forwards updated estimates to the commit logic. These messages should have low latency to limit the occurrence of rollbacks and to control the size of the event and message history. In the remainder of this section, we describe the primary components in more detail.

Figure 3.2: The P-heap data structure [11]

#### 3.2.3 Event Queue

The event queue maintains a time-ordered list of events to be processed by the event processors. It needs to support two basic operations: *insert* and *dequeue*. An *invalidate* operation can be included to facilitate faster cancellation of events that have not been processed yet. However, this function was not considered in our preliminary implementation to avoid circuit complexity.

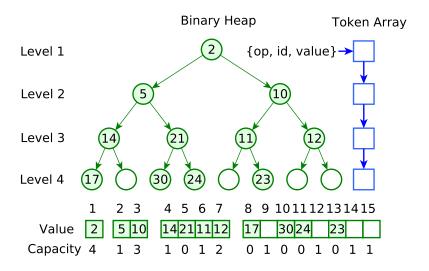

We selected a *pipelined heap* (P-heap in short) [11] structure as the basic organization in our implementation, except for a few modifications described later. P-heap uses a pipelined binary heap to provide two cycles constant access time. The P-heap structure uses a conventional binary heap with each node storing a few additional bits to represent the number of vacancies in the sub-tree rooted at the node (Figure 3.2). The capacity values are used by *insert* operations to find the path in the heap that it should percolate

through. P-heap also keeps a *token* variable for each stage which contains the current operation, target node identifier and value that is percolating down to that stage. During an insertion operation, the value in token variable is compared with the target node: a smaller value replaces the target node value and a larger value passes down to the token variable of the following stage. The id value of the next stage is determined by checking the capacity associated with the nodes.

For the dequeue operation, the value of the root node is dequeued and replaced by the smaller between its two child nodes. The same operation continues to move through the branch, promoting the smallest child at every step. During any operation any two of the consecutive stages are accessed; one read access and the other write access. As a result, a stage can handle a new operation every two cycles, since the operation of the heap is pipelined with different insert and/or dequeue operations at different stages in their operation [11].

P-heap can be efficiently implemented in an FPGA. Every stage requires a Dual Port RAM. Depending on the size of the stage, it can be synthesized with registers, distributed RAM, or block RAM to maximize resource utilization. An arbitrary number of stages can be added (limited by resource availability) as the performance is not hurt by the number of stages in the heap, making it straightforward to scale.

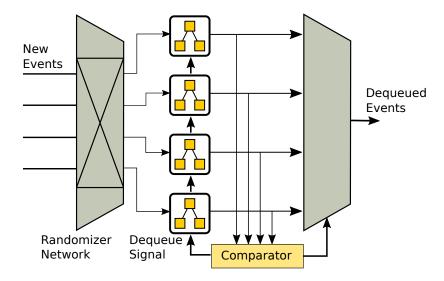

In an optimistic PDES system, it is possible that ordering can be relaxed to improve performance, while maintaining simulation correctness via rollbacks to recover from occasional ordering violations. This opens up possibilities for optimization of the queue structure. For example, multiple heaps may be used in parallel to service more than one

Figure 3.3: Multiple event issue priority queue

request in a single cycle. In an approach similar to [41], we can use a randomizer network to direct multiple requests to multiple available heap (Figure 3.3). There is a chance that two of the highest priority events may reside in the same heap and ordering violation will occur when a lower priority event from same LP is dequed from another queue during multiple dequeue. However, as the number of LPs and events grow, the probability that two events from the same LP are at different queue heads decreases. So, the number of such events will be low enough to result in a net performance gain. We used the simple P-heap model in the baseline implementation and explored the effect of this version in our optimized architecture discussed in section 4.1. Other structures that sacrifice full ordering but admit higher parallelism such as Gupta and Wilsey's lock-free queue may also be explored [37].

The queue stores a key-value pair. Event time-stamp acts as the key and the value contains the id of the target LP and a payload message. In case the payload message is too large, we store a pointer to a payload message in memory.

#### 3.2.4 Event Processor

The event processor is at the core of PDES-A. The front-end of the processor is common to all simulation models. It is responsible for the following general operations: (1) to check the event history for conflicts; (2) to store and clean up state snapshots by checking GVT; (3) support events exchange with the event queue; and (4) respond to control signals to avoid conflicting event processing. In addition, the event processors execute the actual event handlers which are specialized to each simulation model to generate the next events and compute state transitions.

The task processing logic is designed to be replaceable and easily customizable to the events in different models. It appears as a black box to the event processor system. All communications are done through the pre-configured interface. The event processor passes event message and relevant data to the core logic by populating FIFO buffers. Once the events are processed, the core logic uses output buffers to load the generated events. The core logic has interfaces to request state memory by supplying addresses and sizes. The fetched memory is placed into a FIFO buffer to be read from the core. The interface to the memory port is standard and provided in the core to be easily accessible by the task processing logic.

#### 3.2.5 Event scheduling and processing

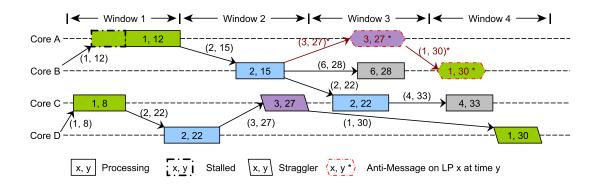

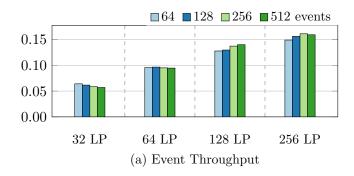

Figure 3.4 shows a representative event execution timeline in the system. Events are assigned to the event processors in order of their timestamps; in the figure, the event is represented by a tuple (x,y) where x is the LP number and y is the simulation time. When

Figure 3.4: Simplified timeline representation showing scheduling of events in the system.

a second event (1, 12) is scheduled while another event (1, 8) associated with the same LP is already being processed, the core is stalled by the controller unit until the first event completes. At the completion of an event, the controller unit allows the earliest timestamp among the waiting (stalled) events for that core to proceed as shown in window 1. Each event generates one or more new events when it exits which are schedule at some time in the future when a core is available. Occasionally, an event is processed after another event with a later timestamp has already executed (i.e., a straggler event). It needs to be rolled back to restore causality. Windows 2 in figure 3.4 shows one such event (2,22) which executes before event (2,15). We use a lazy cancellation and rollback approach. Event processing logic detects the conflict by checking the processed events list and initiates the rollback. The new event will restore the states and generate events it would have normally scheduled (6, 28) along with anti-messages (3, 27\*) for all events generated by the straggler event, and new event (2, 22) that reschedules the straggler event itself.

The anti-messages may get processed before or after its target event is done. An anti-message (3, 27\*) checks the event history and if the target event has already been

processed, it rolls back the states and generate other anti-messages (1, 30\*) to chase the erroneous message chain much like a regular events as shown in window 3 of Figure 3.4. If the target message is yet to arrive, the anti-message is stored in the event history table. The target message (1,30) cancels itself upon discovery of the anti-message in the history and no new event is generated as shown in window 4.

#### 3.2.6 Event History