# **Runtime Monitoring on Multicores via OASES**

Vijay Nagarajan and Rajiv Gupta

University of California, CSE Department, Riverside, CA 92521 {vijay,gupta}@cs.ucr.edu

# Abstract

Runtime monitoring support serves as a foundation for the important tasks of providing security, performing debugging, and improving performance of applications. Often runtime monitoring requires the maintenance of information associated with each of the application's original memory location, which is held in corresponding shadow memory locations. Unfortunately, existing robust shadow memory implementations are inefficient. In this paper, we present OASES: OS and Architectural Support for Efficient Shadow memory implementation for multicores that is also robust. A combination of operating system support (in the form of coupled allocation of memory pages used by the application and associated shadow memory pages) and architectural support (in the form of ISA support and exposed cache events) is proposed. Our page allocation policy enables fast translation of original addresses into corresponding shadow memory addresses; thus allowing implicit addressing of shadow memory. By exposing the cache events to the software, we ensure in software that the shadow memory instructions execute atomically with their corresponding original memory instructions. Our experiments show that the overheads of runtime monitoring tasks are significantly reduced in comparison to previous software implementations.

*Categories and Subject Descriptors* D.2.5 [*Software Engineering*]: Testing and Debugging – debugging aids, monitors

General Terms Design, Reliability, Performance, Experimentation

Keywords Shadow Memory, Atomic Updates, Exposed cache events

## 1. Introduction

There has been significant research on the online monitoring of running programs using various dynamic analyses for a variety of purposes. For example, LIFT (16) and Taint-Check (15) are software tools that perform taint analysis to ensure the execution of a program is not compromised by harmful inputs; Memcheck (13) is a popular memory checking tool that is widely used to detect memory bugs; and Eraser (18) is a tool for detecting data races. A common element among these tools is that they make use of shadow memory (13). With each memory location used by the application, a shadow memory location is associated to store information about that memory location. Original instructions in the application that manipulate memory locations are accompanied by instructions that manipulate corresponding shadow memory locations. For example, in taint analysis, with every memory location a taint value is associated that indicates whether that memory location is data dependent on an (tainted) input. Each original instruction that stores the value of a register into a memory location is accompanied by an additional store that moves the taint value of the register into the shadow memory location. Similarly each original instruction that loads a value from a memory location to a register is accompanied by an instruction that loads the corresponding taint value from shadow memory location. Thus, monitoring requires that loads and stores present in an application be accompanied by shadow memory loads and stores.

Although the need for shadow memory support across variety of monitoring tasks is well recognized, supporting robust shadow memory that can be efficiently accessed and manipulated remains a challenge that has not been successfully addressed. There are two key issues at the heart of this challenge:

Shadow Memory Management. An important issue in shadow memory design, that affects the speed and the robustness of the shadow memory implementation, is the organization of the shadow memory in the address space of the application process (13). A simple half-and-half scheme (3; 16) roughly divides the virtual memory into two halves, the original memory and the corresponding shadow memory. While this has the advantage of a fast translation of original addresses into corresponding shadow memory addresses, its less flexible layout means that it fails for some programs in linux and is incompatible with operating systems with restrictive layouts (13). Moreover, it does not scale when we need to associate more than one shadow value per memory location. To improve robustness, Valgrind's Memcheck tool (13) implements a two-level page table in software. Although, several optimizations are proposed, the slowdown can still be as high as 22x for SPEC programs, about half of which may be due to shadow memory accesses (13).

Atomic Updates. For multithreaded programs, it is essential that original memory instructions (OMIs) and the shadow memory instructions (SMIs) accompanying them be carried out atomically in order to correctly maintain the shadow values. Since OMIs and SMIs are really separate instructions, maintaining atomicity incurs an additional cost. Existing software monitoring schemes (14; 13) prevent race conditions that can lead to incorrect shadow values by ensuring that a thread switch does not occur in the middle of execution of OMI and its corresponding SMI. Unfortunately, the problem still exists when a multithreaded program is being run on, the now ubiquitous, multicores. To overcome this problem of concurrent updates on multicores, threads can be serialized and made to run on one core (14). However, this is clearly inefficient as parallelism is sacrificed. Alternatively, in the fine grain locking approach, the thread that wants to perform a SMI along with the OMI, grabs a lock associated with that memory region and releases the lock after completion. However, this approach suffers from the overhead of executing additional instructions including the expensive atomic instructions.

In this paper, we present OASES, a robust shadow memory implementation for multicores that addresses the above challenges of *efficient address translation* and *atomic updates*. Our design couples shadow memory management (i.e., its allocation, addressing, and coherence) with the management of original memory in a manner that enables the required goals to be met.

| Monitoring Application                                                                                                                                     | Meta Data Tracked by Shadow Memory                                                                                                                                                                                                                                            | Code Instrumentation Required                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>DIFT</b> (16; 15; 3) (Dynamic Information Flow Tracking) is used to track whether contents of memory locations are data dependent upon insecure inputs. | With each memory location (byte) a <i>taint</i> bit is associ-<br>ated, which indicates whether that memory location is<br>data dependent upon an insecure input. Consequently,<br>the taint bit has to be manipulated for every memory<br>instruction.                       | (Loads) For every load, the taint bit corresponding to<br>the loaded memory location has to be read; (Stores)<br>For every store, the taint bit corresponding to the stored<br>memory location has to be updated. |

| <b>Eraser</b> (18) is used to track information to enable data race detection.                                                                             | With every memory word Eraser associates the <i>status</i> and the <i>lockset</i> . The <i>status</i> tells if the current word is shared across threads or exclusive to one thread, while the <i>lockset</i> indicates the set of locks used to access that memory location. | (Loads/Stores) Each memory access, either by a load or<br>a store, must be accompanied with reading and writing<br>of both <i>status</i> and <i>lock-set</i> .                                                    |

| Memcheck (13) is used for debugging memory bugs.                                                                                                           | Every location is associated with two values, the $A$ bit<br>and the $V$ bits. While the $A$ bit indicates if that particu-<br>lar memory location is addressable, the $V$ bits indicate<br>whether the corresponding bits in the memory location<br>have been defined.       | (Loads) The <i>A bit</i> is read and updated while <i>V bits</i> are read on every load; (Stores) The <i>A bit</i> and the <i>V bits</i> are read and updated on every store.                                     |

| <b>MemProfile</b> (1) is a simple memory profiler that keeps count of number of reads and writes to each memory location.                                  | With each memory location two counts are associated: <i>ReadCount</i> and <i>WriteCount</i> .                                                                                                                                                                                 | (Loads) The <i>ReadCount</i> is read and updated on every load; (Stores) The <i>WriteCount</i> is read and updated on every store.                                                                                |

Table 1. Applications Requiring Runtime Monitoring.

# 2. Runtime Monitoring: Applications and Costs

Runtime monitoring serves as a foundation of a variety of tasks aimed at providing security, performing debugging, and improving performance of applications. In this section we describe the role of monitoring in context of four popular monitoring tasks. In addition, we analyze the execution time overhead of runtime monitoring as well as degree to which various factors contribute to this overhead.

Table 1 describes four popular monitoring tasks: DIFT (15) for runtime monitoring of software attacks, Memcheck (13) a tool for runtime checking of memory errors, Eraser (18) for runtime detection of data races, and Memprofile a runtime memory profiler (1). Each of these monitoring tasks require the following:

- With each data memory location, shadow memory location(s) are associated to track the meta data required by the monitoring task. The second column of Table 1 describes the meta data maintained by these applications. The number of distinct items of information to be associated with a memory location can vary. While *DIFT* associates just one value, the taint bit, for every memory location, *Eraser* and *Memcheck* associate two values per memory location. Thus, in general, capability of associating *multiple* shadow values for every memory location is needed.

- Application code must be instrumented by associating operations for maintaining the meta data with the memory operations (loads and stores) in the application. The third column of Table 1 describes the function of shadow memory instructions (SMIs) that instrument each original memory instruction (OMI) for each of the monitoring tasks.

- An OMI and its associated SMI(s) must be performed *atomically*. For example, if during DIFT a value in an original memory location and its taint bit are read, atomicity must guarantee that the taint bit corresponds to the value read from the original memory location and not to some old value that once resided in the memory location. Note that the SMI in *DIFT* is *symmetric*, i.e. for every original *load* there is an associated *shadow load* and for every original *store*, there is a *shadow store*. However, in *general*, for every original memory access (*load*, *store*), the associated

*shadow memory* may need to be both *read* and *updated*. In fact this is the case for *Eraser*.

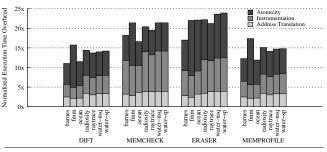

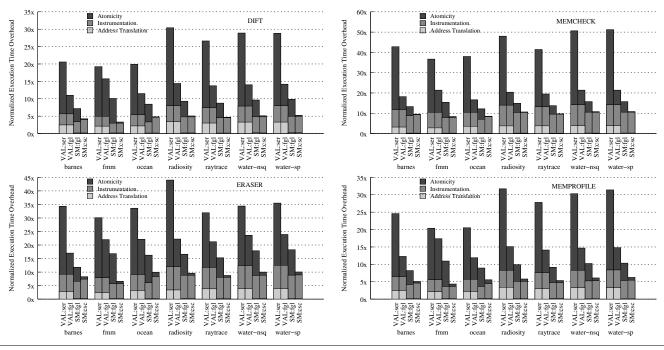

Figure 1. Overhead Imposed by Current Shadow Memory Tools.

To get an idea of the performance overhead imposed by the current shadow memory tools, we measured the overhead of performing the above monitoring tasks for the SPLASH (23) benchmarks on a 4 core processor. As shown in Fig. 1, we broke up the runtime overhead of monitoring into three components: the overhead for performing address translation, overhead for maintaining atomicity of OMIs and SMIs, and finally the overhead due to execution of instrumentation code required by the monitoring task. As we can see the overhead in performing the monitoring tasks can be as high as 25x, with a significant percentage of overhead (about 50%) spent in performing address translation and enforcing atomicity.

The goal of OASES is to reduce the runtime overhead of monitoring tasks. For this purpose, we focus on providing support that reduces the overhead due to the two components that are common to all the monitoring tasks, i.e. address translation of shadow memory references and enforcing atomicity of OMIs and SMIs. The third component, code instrumentation, varies from one monitoring task to another. Thus, the ability to program the instrumentation to accommodate the requirements of different monitoring tasks must be maintained. We do not provide any specialized hardware support to reduce the cost of executing the instrumentation code as different monitoring applications will require different hardware support.

## 3. Shadow Memory Design for Multicores

We begin by providing an overview of our approach for efficiently enforcing atomicity and performing address translation. Then in subsequent sections we present our solutions in full detail. Let us first consider the problem of performing atomic updates of original memory locations and corresponding shadow memory locations.

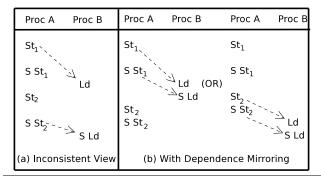

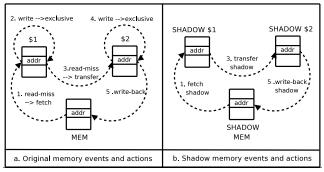

Atomic Updates. First let us see why an OMI and its SMI(s) must be performed atomically. Consider the example shown in Fig. 2. Processor A executes two store instructions ( $St_1$  and  $St_2$ ) and their corresponding shadow store instructions ( $SSt_1$  and  $SSt_2$ ) while Processor B executes a load instruction Ld and its corresponding shadow load SLd. We assume that all these instructions target the same virtual address. As we can see in Fig. 2a, if no special care is taken, Ld in Processor B may see the value produced by  $St_1$  while SLd may see a value produced at  $SSt_2$ . Atomic SMIs will guarantee that Ld and SLd see either values produced by  $(St_1, SSt_1)$  or  $(St_2,SSt_2)$  as shown in Fig. 2b. Prior solutions have used thread serialization or fine grained locking to ensure atomicity of OMIs and SMIs. However, they are inefficient as we saw earlier: while thread serialization is clearly inefficient since it compromises on concurrency, the expensive atomic instructions and memory fences involved in locking are also inefficient. Although the above example illustrates a scenario in which there is a race in the original program, the same problem can manifest itself even if the original program is devoid of races; the introduction of SM can break the assumed atomicity of instructions such as compare-and-swap which are used to implement a variety of synchronization primitives and lock-free data structures. (4)

Figure 2. Atomic Updates of Shadow Memory.

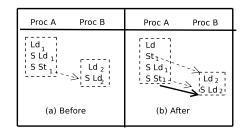

Our solution for enforcing atomicity is based upon the following key observations. First, given a memory location and a corresponding shadow value, we must maintain multiple memory locations for this shadow value. More specifically, a distinct shadow location must be provided for each distinct place where the shadow value can reside, i.e. corresponding to each processor's cache we must provide a shadow memory location and corresponding to the memory we must provide a shadow memory location. Second, we must provide a protocol for updating the shadow values in a manner that guarantees atomicity. We name this protocol as the *Coupled Shadow Coherence* (CSC) protocol because it couples the coherence of shadow values with coherence actions of the original values to achieve the effect of atomicity.

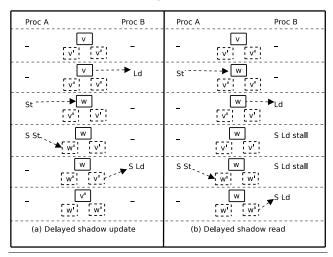

The need for maintaining multiple shadow locations to implement a single shadow value and the requirements placed on the CSC protocol for maintaining these shadow locations are illustrated by two scenarios shown in Fig. 3. Let us consider the first scenario, Fig. 3(a), in which the Ld and SLd performed by processor B must access values v and v' respectively. However, the execution of Ldand SLd at Processor B is intervened by execution of a St and SStat Processor A that update values v and v' to w and w' respectively. The contents of the memory location and the two corresponding shadow locations for the two processors are shown in the figure as the execution proceeds. It should be noted that to guarantee atomicity of Ld and SLd at Processor B, the following must be done. After the execution of SSt at Processor A, although the contents of shadow location for Processor A are changed to w', the contents of the shadow location for Processor B must remain unchanged as v' till v' has been read by SLd at Processor B. While this scenario shows that an update of a shadow location may need to be delayed till a SLd had been executed, the second scenario in Fig. 3b shows the reverse situation, i.e. the execution of SLd must be stalled till the shadow location has been updated.

In the first scenario, there is a period of time during which the shadow values at the two processors must be different. This justifies the need for separate shadow locations for the two processors. The requirements of delaying the update of a shadow location (first scenario) and waiting for the update of a shadow location (second scenario) must be enforced by the CSC protocol that will be implemented in software. For example, in the first scenario, following Processor B's execution of its SLd operation, any future references by Processor B to the memory location and its shadow location should result in the delivery of values w and w' respectively. While delivery of w is guaranteed by the hardware cache coherence mechanism, the delivery of w' requires that this value be copied from the shadow location for Processor A to the shadow location for Processor B. The CSC protocol will be responsible for ensuring that this copying operation is performed. Similarly, in the second scenario the CSC protocol will cause the execution of *SLd* to stall till it is able to copy the value w' from shadow location for Processor A to shadow location for Processor B.

The actions performed by the CSC protocol to maintain the consistency of shadow memory locations are coupled with the actions performed by the cache coherence protocol to maintain the consistency of the memory locations cached at various processors. The example in Fig. 4 shows how cache events trigger corresponding CSC actions. To implement the CSC protocol we provide architectural support in the form of *exposing the cache events* to the software which then performs the corresponding actions of the CSC protocol. Whenever the cache controller of a processor receives a cache-coherence event, such as a data value reply, it interrupts the processor and passes the control to the CSC protocol. The CSC protocol is implemented as a sent of handler functions – one handler for each distinct cache coherence event. One key aspect of the CSC protocol is that there are no changes to the original hardware cache coherence protocol.

Figure 4. Coupled Shadow Coherence.

Efficient Address Translation. The process of addressing shadow memory needs to be both robust and efficient. We employ a design that meets these goals. We use the same virtual address to reference an original memory location and the corresponding shadow memory location. During translation to physical addresses, different physical addresses are produced for the original and SMIs referring to the same virtual address. In particular, for every original page there are corresponding shadow memory pages and during page translation virtual page is translated to different appropriate physical pages. This approach is robust as unlike the half-and-half strategy it does not require an application to reserve half of its virtual address space for shadow memory. To enable efficient translation of original memory addresses into shadow memory addresses we take the following approach. A page of memory belonging to the application and the corresponding shadow memory pages are all allocated consecutive physical memory pages. Thus, from the address of a original memory location, the address of corresponding shadow memory locations can be efficiently computed. Furthermore, we ensure that at any point in time if an original memory page resides in main memory then the corresponding shadow memory pages also resides in main memory. Thus, while page table entries are created for original memory pages, no additional page table entries are required for the corresponding shadow pages.

In the remainder of this section we describe the detailed design and implementation of the solutions outlined above. First we describe instruction set support for identifying memory instructions that must be executed atomically as well as distinguishing an OMI from its SMIs. Next we present the details of the OS and architectural support for efficient translation of original memory addresses to shadow memory addresses. Finally we describe the details of our CSC protocol that ensures atomic updates of original memory locations and corresponding shadow memory locations.

#### 3.1 Instruction Set Support

We need instruction set support for two purposes. First, since each OMI and all of its SMIs must execute atomically, we need a mechanism for identifying them as an *atomic block*. Second, since the same virtual address is specified in addressing a memory location and its corresponding shadow locations, for correct address translation there is a need to provide a means for *distinguishing* the OMI and SMIs for various shadow values. We propose two new instructions that simultaneously meet the above requirements. As shown below, the two new instructions, shadow-start and shadow-end, are used to define an atomic block. The operands of the shadow-start instruction, *init-SVC* and *pid*, allow us to distinguish between OMI and SMIs for various shadow values.

```

shadow-start init-SVC, pid

...

shadow-end

```

The *pid* operand identifies the processor id of the processor whose copy of a shadow value is to be accessed. The *pid* operand is an optional operand. If no value is specified as the processor id, the processor id is implicitly assumed to be the current processor's processor id. The operand *init-SVC* enables us to distinguish between the OMI and various SMIs within an atomic block. All memory instructions in the atomic block that access the same virtual address as the OMI are recognized as SMIs. If *init-SVC* is specified as 0, the first memory operation in the atomic block is treated as the OMI and subsequent memory operations that access the same virtual address are treated as SMIs. Moreover, the second memory operation refers to the first shadow value, the third memory operation refers to the second shadow value and so on. However, a non zero init-SVC is used to handle situations in which only shadow values need to be accessed without the accessing original values. For example, if init-SVC is 1, the first memory access refers to the first shadow value and so on. In other words, *initSVC* is specified as a parameter to give us additional flexibility in accessing the shadow values. It should be noted that we assume that multiple shadow reads (writes) correspond to different shadow values. We are able to do this since each shadow memory location is read and written once in an atomic block. It is not necessary to explicitly read (or write) to the same shadow memory location more than once inside the atomic block the shadow memory value can be copied on to the stack, manipulated and then copied back.

| Example 1.<br>// init-SVC = 0<br>shadow-start 0x0<br>// Access Original memory<br>Id r1, addr<br>// Access shadow cache<br>Id r2, addr // 1st shadow value<br>// Access shadow cache<br>Id r3, addr // 2nd shadow value<br>shadow-end | Example 2<br>// init-SVC =1, pid =1<br>shadow-start 0x1, 0x1<br>// Access shadow cache<br>ld r1, addr // 1st shadow value<br>ld r2, addr // 2nd shadow value<br>shadow-end<br>Example 3<br>// init-SVC =1, pid = 3<br>shadow-start 0x1, 0x3<br>// Write to shadow memory<br>st r1, addr // 1st shadow value<br>shadow-end |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Figure 5. Some Code Sequences for Accessing Shadow Values.

Given the above interpretation of *init-SVC*, the compiler must generate instructions within an atomic block in the appropriate order. Fig. 5 shows some examples that show how the compiler generates code for accessing various shadow values. For the purpose of this example, let us assume that there are 2 processors with 2 shadow values. The first scenario shows the inlined instrumentation for accessing both original and shadow memory values. Since original memory values are involved, the value of *init-SVC* is set to 0, specified as an operand to shadow-start instruction. Accordingly, the first memory access is an original memory access and subsequent accesses are for shadow values. Since the shadow-start instruction does not specify any *pid* operands, the current processor id is used in the translation process and so the shadow cache contents of the current processor are accessed. The second scenario shows code generated for the handler. The purpose of this handler is to read the contents of shadow cache of processor 1 and write it to shadow memory. Accordingly the first two loads access the shadow cache contents of processor 1. To enable these accesses, init-SVC is set to 1 through the shadow-start instruction; this is because there are no original memory accesses involved. Furthermore, by the specifying the *pid* as 1, the shadow cache contents of processor 1 are accessed. Finally, in the last example, the two stores are made to write to the shadow memory contents. This is enabled by specifying the *pid* as 3; since there are only, 2 processors, a pid of 3 denotes shadow memory.

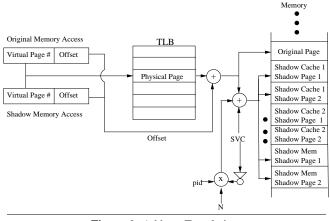

## 3.2 Address Translation for Shadow Memory Accesses

Since the same virtual address is used by the OMI and the corresponding SMIs, we must implement an address translation scheme that efficiently translates the virtual address used by SMIs into appropriate physical addresses of shadow locations. To ensure that the translation can be performed efficiently, we make use of a page layout scheme that fixes the relative location of an original physical page and its corresponding shadow physical pages. For every original page, the OS allocates p + 1 shadow pages per shadow value, where p is the number of processors. Therefore, if there are *n* shadow values, the processor allocates  $n \times (p+1)$  shadow pages. Moreover, consecutive set of physical pages are allocated by the OS. Thus, given the physical address of an original memory location, the physical addresses of the various associated shadow values can be easily determined. Given the values of SVC (shadow value count), the pid, and N the number of processors, address translation proceeds by multiplying N with the *pid* and adding the result with SVC. The resultant is added to the physical page fetched from the TLB, if it is a shadow memory access (SVC is non zero); if it is an original memory access, the resultant is 0, since the value of SVC is 0 and hence the fetched page from TLB is used. The above page layout and addressing scheme is illustrated in Fig. 6 for the scenario where there are 2 processors and 2 shadow values. As we can see, the first page denotes the original page, while the rest denote shadow pages. The second and third pages denote the shadow cache pages of the first processor, while the fourth and fifth denote the shadow cache pages of the second processor, and finally the last two pages refer to the shadow memory pages.

Figure 6. Address Translation.

The OS treats every original memory page and its corresponding shadow pages as a single entity. When the OS decides to swap out an original page on to the disk, it also swaps out the associated shadow pages. Similarly, both original page and its associated shadow pages are swapped in together. The above translation process is highly efficient. Another important consequence of this scheme is that shadow memory does not require any additional TLB entries. Finally, since an application may not require monitoring, we add an extra flag to the *process descriptor* which indicates whether that particular process requires shadow memory support. When this flag is set, the OS allocates shadow page(s) along with every original page that it allocates; otherwise no shadow pages are allocated.

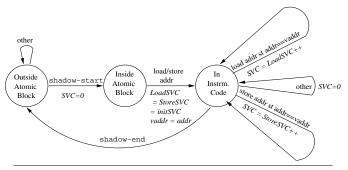

Given the manner in which code within atomic blocks is organized, we next show how this organization can be used to generate the *Shadow Value Count* (SVC) needed for address translation in Fig. 6. The state machine in Fig. 7 generates the value of *SVC*. The state machine is in initial state "Outside Atomic Block" and when shadow-start is encountered it moves to state "Inside Atomic Block" initializing SVC to init-SVC the value specified as an operand to the shadow-start instruction. For now, let us assume that the value of init-SVC is a 0, which means the first memory instruction encountered refers to the OMI. When the OMI (load or store) is encountered – the virtual address is remembered in vaddr; counts LoadSVC and StoreSVC are set to initSVC; and transition to state "Inside Instrumentation Code" takes place. In this state when a shadow load (store) is encountered, LoadSVC (StoreSVC) is incremented and its value is assigned to SVC for use by address translation logic. If shadow-end is encountered, transition to initial state "Outside Atomic Block" occurs.

Figure 7. Generating Shadow Value Count.

*Small Sized Shadow Values*. In the above discussion we assumed that each memory location used by an application requires equal sized shadow values. For some monitoring tasks, each word of original application does not require an equal size shadow value. For example, in DIFT each memory byte is associated with only a shadow bit. Association of a byte of shadow value with every byte of original application, in this instance, will lead to wastage of memory. It is also possible to extend our scheme to support small-sized shadow values as discussed in (10).

*Optimizing Shadow Cache Organization.* The memory overhead of maintaining shadow cache can be reduced. This is based on the simple observation that the cache can only hold a fixed amount of data and so the size of the shadow cache can be limited. Thus one way of organizing shadow cache is to reserve a small portion of the virtual memory for the shadow cache. For example, for an L1 cache of size 32KB with 8 processors and 4 shadow values, it is sufficient to allocate 1MB of virtual memory for shadow cache. However, such a scheme will only be applicable for a direct mapped cache; otherwise tag checks that are performed in parallel in hardware will have to performed in software, which can be very expensive.

#### 3.3 Atomic Updates of Shadow Memory

As we have already discussed, in a multithreaded application, we need to ensure that an OMI and its corresponding SMI(s) are executed atomically. In this section, we present the CSC protocol to ensure atomicity and describe how we implement CSC in software with the help of *exposed cache events*. To implement our CSC scheme in software, the only requirement is that cache controller expose the specified events to the software. Consequently, our implementation does not rely on any particular coherence protocol used or the memory consistency model enforced by the system.

In CSC, the coherence of the shadow memory values is *coupled* with the coherence of the original memory. In particular, to achieve atomicity, the CSC scheme we develop ensures *dependence mirroring* between OMI and SMIs; dependences exercised among SMIs are made to *mirror* the dependences exercised among OMIs. Let  $M_1$  and  $M_2$  denote a pair of OMIs and  $SM_1$  and  $SM_2$  denote their corresponding SMIs. If  $M_2$  is dependent (e.g., RAW)

upon  $M_1$  during an execution, then  $SM_2$  must be similarly dependent upon  $SM_1$ . To enforce dependence mirroring, we ensure that whenever there is a transfer of original memory values from one local cache to memory (or another local cache), it is accompanied by a corresponding *co-transfer* of shadow memory values. To implement this in software, we propose exposing cache events to the software. Whenever the cache controller receives a pre-specified cache event for a processor's local cache, it can be programmed to interrupt the processor, and call a predefined *handler* function; by suitably programming the handler, we can enforce dependence mirroring in software.

*Events*. To implement CSC scheme in software we expose the following specific cache events:

- When a processor exclusively holding a block, is about to send the data value reply

- · When a processor receives a data value reply

- When a processor experiences a read miss for a block uncached in any of the processors

- When a processor is about to write back a block

The first two events capture dependencies that are exercised through cache coherence network, while the last two events capture dependences exercised via the main memory.

Handler Semantics. The coherence controller interrupts the processor and calls the handler function, when one of the specified events takes place. When the specified event occurs, the current instructions in the pipeline are flushed and a call to handler function is made at once. However, if the processor is in the midst of executing an atomic block (between shadow-start and shadow-end), then the call to the handler is delayed until the atomic block is fully executed (shadow-end instruction commits). The handler is made to reside in the user space and the semantics of the call to the handler is similar to a function call. The programmer is responsible for saving and restoring the values of registers that are used in the handler. However, the hardware is responsible for providing event related information to the handler as function call parameters: for example, the block address associated with the event and the remote processor id associated with the event, if applicable. The hardware pushes these two values (proc and addr) into the stack, before calling the handler. The programmer notifies to the hardware through the handler instruction, which handler to call for what event. While the event is expressed via the predefined event*code*, the handler is specified with its start instruction address.

| State                  | Purpose                                                                                                          |

|------------------------|------------------------------------------------------------------------------------------------------------------|

| shadow (addr)          | Shadows the original address 'addr'                                                                              |

| shadow-cache (p, addr) | Proc p Shadow cache contents of address 'addr'                                                                   |

| ready (i, j)           | Synchronizing procs 'i' and 'j' for implementing<br>co-transfer b/w shadow caches                                |

| shadow-event-cnt       | Ensuring that co-transfer b/w shadow memory<br>and shadow cache takes place along with the<br>original transfer. |

Figure 8. State Maintained to Implement CSC.

State Maintained for Implementing CSC. Since we are implementing CSC in software, we need to maintain shadow coherence state in software as shown in Fig. 8. Every original memory block, addr, that is present in the local cache of each processor p is shadowed by shadow-cache(p, addr); likewise, each original memory address in the main memory is shadowed by shadow(addr). When original memory dependences are enforced via the coherence network, enforcing the dependences of shadow values entails that the two processors involved in the dependency synchronize with each other. For achieving this pair-wise synchronization, we maintain a flag for each processor pair (i, j) which is referred to as ready(i, j). Finally when dependences are enforced through the main memory, we need to ensure that co-transfer of shadow values to and from shadow memory, take place in the same order of the transfer of original values to and from shadow memory. For achieving this, we maintain a count referred to as *shadow-eventcnt*, to uniquely identify each memory event.

*Handlers for CSC.* We now explain how the individual steps involved in CSC scheme are implemented within the software handlers, which is shown in Fig. 9. For this discussion, we assume macros for reading and writing into the shadow memory (steps 48 through 55) and shadow cache (steps 31 through 45).

| 1.                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                         | // Proc 'i' is about to send data reply to proc 'j'                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 2.                                                                                                                                                                                                                                      | // for block address 'addr'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 3.                                                                                                                                                                                                                                      | data-reply-request (addr, j)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 4.                                                                                                                                                                                                                                      | while (ready(i,j) == true);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 5.                                                                                                                                                                                                                                      | ready(i,j) = true;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 6.                                                                                                                                                                                                                                      | end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 7.                                                                                                                                                                                                                                      | chu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 8.                                                                                                                                                                                                                                      | // Proc 'j' receives data reply from proc 'i'                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 9.                                                                                                                                                                                                                                      | // for block address 'addr'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 10.                                                                                                                                                                                                                                     | data-reply (addr, i)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 11.                                                                                                                                                                                                                                     | while $(ready(i,j) == false);$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 12.                                                                                                                                                                                                                                     | write-shadow-cache (j, addr)= access-shadow-cache (i, addr);                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 13.                                                                                                                                                                                                                                     | ready (i,j) = false;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 14.                                                                                                                                                                                                                                     | end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 15.                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 16.                                                                                                                                                                                                                                     | // Proc 'i' is about to write back block 'addr'                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                                                                                                                                                                                                         | write-back (addr, event-cnt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 18.                                                                                                                                                                                                                                     | while (event-cnt != shadow-event-cnt);                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 19.                                                                                                                                                                                                                                     | write-shadow-memory (addr)= access-shadow-cache (i, addr);                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 20.                                                                                                                                                                                                                                     | shadow-event-cnt++;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 21.                                                                                                                                                                                                                                     | end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 22.                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 23.                                                                                                                                                                                                                                     | // Proc 'i' experiences a read miss for block 'addr'                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 24.                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 25.                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 26.                                                                                                                                                                                                                                     | write-shadow-cache (i, addr) = access-shadow-memory (addr);                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 27.                                                                                                                                                                                                                                     | shadow-event-cnt++;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 28.                                                                                                                                                                                                                                     | end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 29.                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 30.                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                                                                                                                                                                                                         | // reads from registers and writes to shadow cache                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                                                                                                                                                                                         | write-shadow-cache (pid, addr)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 33.                                                                                                                                                                                                                                     | shadow-start 0x1, pid // init-SVC = 1, pid = pid                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 34.                                                                                                                                                                                                                                     | stadow start oxi, pid // int sve = 1, pid = pid                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 35.                                                                                                                                                                                                                                     | st r2, addr // 2nd shadow value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                                                                                                                                                                                                         | shadow ond                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 36.                                                                                                                                                                                                                                     | shadow-end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 37.                                                                                                                                                                                                                                     | shadow-end<br>end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 37.<br>38.                                                                                                                                                                                                                              | end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 37.<br>38.<br>39.                                                                                                                                                                                                                       | end // reads from shadow cache and writes to register                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 37.<br>38.<br>39.<br>40.                                                                                                                                                                                                                | end<br>// reads from shadow cache and writes to register<br>read-shadow-cache (pid, addr)                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 37.<br>38.<br>39.<br>40.<br>41.                                                                                                                                                                                                         | end<br>// reads from shadow cache and writes to register<br>read-shadow-cache (pid, addr)<br>shadow-start 0x1, pid //init-SVC = 1, pid = pid                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 37.<br>38.<br>39.<br>40.                                                                                                                                                                                                                | end<br>// reads from shadow cache and writes to register<br>read-shadow-cache (pid, addr)                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 37.<br>38.<br>39.<br>40.<br>41.                                                                                                                                                                                                         | end<br>// reads from shadow cache and writes to register<br>read-shadow-cache (pid, addr)<br>shadow-start 0x1, pid //init-SVC = 1, pid = pid                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 37.<br>38.<br>39.<br>40.<br>41.<br>42.                                                                                                                                                                                                  | end<br>// reads from shadow cache and writes to register<br>read-shadow-cache (pid, addr)<br>shadow-start 0x1, pid //init-SVC = 1, pid = pid<br>ld r1, addr // 1st shadow value                                                                                                                                                                                                                                                                                                                                 |  |  |

| 37.<br>38.<br>39.<br>40.<br>41.<br>42.<br>43.                                                                                                                                                                                           | end<br>// reads from shadow cache and writes to register<br>read-shadow-cache (pid, addr)<br>shadow-start 0x1, pid //init-SVC = 1, pid = pid<br>Id r1, addr // 1st shadow value<br>Id r2, addr // 2nd shadow value                                                                                                                                                                                                                                                                                              |  |  |

| 37.<br>38.<br>39.<br>40.<br>41.<br>42.<br>43.<br>44.                                                                                                                                                                                    | end<br>// reads from shadow cache and writes to register<br>read-shadow-cache (pid, addr)<br>shadow-start 0x1, pid //init-SVC = 1, pid = pid<br>Id r1, addr // 1st shadow value<br>Id r2, addr // 2nd shadow value<br>shadow-end                                                                                                                                                                                                                                                                                |  |  |

| <ol> <li>37.</li> <li>38.</li> <li>39.</li> <li>40.</li> <li>41.</li> <li>42.</li> <li>43.</li> <li>44.</li> <li>45.</li> </ol>                                                                                                         | end<br>// reads from shadow cache and writes to register<br>read-shadow-cache (pid, addr)<br>shadow-start 0x1, pid //init-SVC = 1, pid = pid<br>Id r1, addr // 1st shadow value<br>Id r2, addr // 2nd shadow value<br>shadow-end                                                                                                                                                                                                                                                                                |  |  |

| <ol> <li>37.</li> <li>38.</li> <li>39.</li> <li>40.</li> <li>41.</li> <li>42.</li> <li>43.</li> <li>44.</li> <li>45.</li> <li>46.</li> </ol>                                                                                            | end<br>// reads from shadow cache and writes to register<br>read-shadow-cache (pid, addr)<br>shadow-start 0x1, pid //init-SVC = 1, pid = pid<br>Id r1, addr // 1st shadow value<br>Id r2, addr // 2nd shadow value<br>shadow-end<br>end                                                                                                                                                                                                                                                                         |  |  |

| <ol> <li>37.</li> <li>38.</li> <li>39.</li> <li>40.</li> <li>41.</li> <li>42.</li> <li>43.</li> <li>44.</li> <li>45.</li> <li>46.</li> <li>47.</li> </ol>                                                                               | end<br>// reads from shadow cache and writes to register<br>read-shadow-cache (pid, addr)<br>shadow-start 0x1, pid //init-SVC = 1, pid = pid<br>Id r1, addr // 1st shadow value<br>Id r2, addr // 2nd shadow value<br>shadow-end<br>end<br>// reads from registers and writes to shadow memory<br>write-shadow-memory (addr)                                                                                                                                                                                    |  |  |