# UNIVERSITY OF CALIFORNIA, RIVERSIDE

# Department of Computer Science and Engineering Department of Electrical Engineering CS/EE120B – Introduction to Embedded Systems Final

March 20, 2001

| Name:       | Solution Key            |                     | Student ID#:         |

|-------------|-------------------------|---------------------|----------------------|

|             | Please print legib      | ly                  |                      |

| Lab Section | n: <b>21</b> (WF 6-10): | <b>22</b> (MW 2-6): | <b>23</b> (TR 6-10): |

(Numbers in parenthesis denote total possible points for question.)

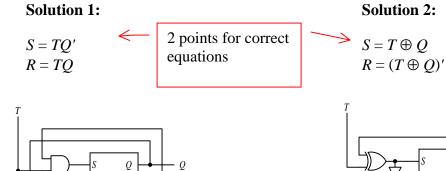

1. Design a T flip-flop using a SR flip-flop and basic gates.

(5)

#### Answer

The next-state table for the T flip-flop is

Q'

|   | $Q_{ m next}$ |       |  |  |  |  |  |  |  |  |  |

|---|---------------|-------|--|--|--|--|--|--|--|--|--|

| Q | T = 0         | T = 1 |  |  |  |  |  |  |  |  |  |

| 0 | 0             | 1     |  |  |  |  |  |  |  |  |  |

| 1 | 1             | 0     |  |  |  |  |  |  |  |  |  |

Converting the next-state table to the implementation table for the SR flip-flop, we get

|   | S          | R     | 1                    |

|---|------------|-------|----------------------|

| Q | T = 0      | T = 1 | 1 point for correct  |

| 0 | 0×         | 10    | implementation table |

| 1 | $\times 0$ | 0 1   | table                |

2 points for correct circuit

Final Page 2 of 8

2. Synthesize the FSM circuit using T flip-flops for the following next-state / output table. (5)

| Current State | Nex             | Output |   |

|---------------|-----------------|--------|---|

| $Q_2Q_1Q_0$   | $Q_{2next}$ $Q$ | Y      |   |

|               | C = 0           |        |   |

| 000           | 000             | 001    | 0 |

| 001           | 001             | 010    | 0 |

| 010           | 010             | 011    | 0 |

| 011           | 011             | 100    | 0 |

| 100           | 100             | 101    | 0 |

| 101           | 101             | 000    | 1 |

Final Page 3 of 8

## Answer

The implementation table is as follows:

| Current State $Q_2Q_1Q_0$ | Impleme $T_2 T$ |     |   |                     |  |  |  |  |

|---------------------------|-----------------|-----|---|---------------------|--|--|--|--|

| 2-2-2                     | C=0             | C=1 |   |                     |  |  |  |  |

| 000                       | 000             | 001 |   |                     |  |  |  |  |

| 001                       | 000             | 011 | K |                     |  |  |  |  |

| 010                       | 000             | 001 |   | 1 point for correct |  |  |  |  |

| 011                       | 000             | 111 |   | implementation      |  |  |  |  |

| 100                       | 000             | 001 |   | table               |  |  |  |  |

| 101                       | 000             | 101 |   |                     |  |  |  |  |

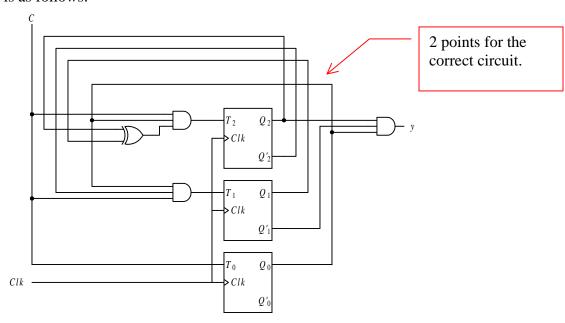

The next-state / output equations are as follows:

$$T_2 = CQ_2'Q_1Q_0 + CQ_2Q_1'Q_0$$

$$= CQ_0(Q_2 \oplus Q_1)$$

$$T_1 = CQ_2'Q_1'Q_0 + CQ_2'Q_1Q_0$$

$$= CQ_2'Q_0$$

$$T_0 = C$$

$$Y = Q_2Q_1'Q_0$$

$$2 \text{ points for the four equations (0.5 points each).}$$

The FSM circuit is as follows:

Final Page 4 of 8

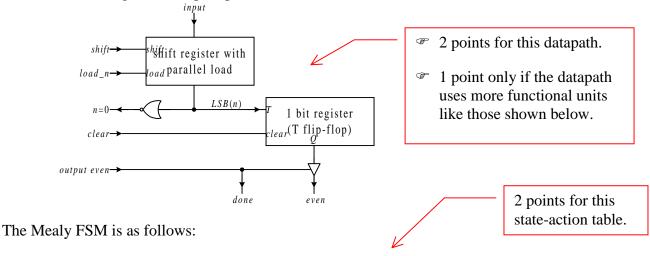

3. Design a customized datapath and a State-action table for the Mealy FSM that solves the following problem. Your datapath should use as few <u>single</u> functional units and registers as possible. Your FSM should have a *start* and a *done* signal. You should first write the high-level pseudo-code that solves the problem. (5)

Input (given) a 7-bit data. Output a '1' if there are odd number of 1 bits in the data, otherwise, output a '0'.

#### Answer

```

even = 0;

input n;

while n ≠ 0{

if (LSB(n) == 1)

even = not even;

n = n >> 1;

}

output even;

output done;

1 point for the pseudo-code

```

### For the datapath, we need:

- one shift register with parallel load for the variable *n*.

- a one bit register (T flip-flop) with load and clear for the variable *even*.

| Current S   |                       | Next State                                                       | Control and Datapath Actions                      |

|-------------|-----------------------|------------------------------------------------------------------|---------------------------------------------------|

| $Q_1 Q_0 N$ | ame                   | [Condition, State]                                               | [Condition, Actions]                              |

| 0.0         | <b>s</b> <sub>0</sub> | $\begin{bmatrix} start = 0, s_0 \end{bmatrix}$                   | even = 0                                          |

|             |                       | $\begin{bmatrix} start = 0, s_0 \\ start = 1, s_1 \end{bmatrix}$ | done = 0                                          |

|             |                       |                                                                  | output = Z                                        |

| 0 1         | $s_1$                 | $s_2$                                                            | n = input                                         |

| 10          | $s_2$                 | $\lceil n \neq 0, s_2 \rceil$                                    | $\left[ LSB(n) = 1, even = not \ even \right]$    |

|             |                       | $\begin{bmatrix} n \neq 0, s_2 \\ n = 0, s_3 \end{bmatrix}$      | $\left\lfloor n \neq 0, n = n >> 1 \right\rfloor$ |

| 1 1         | <b>S</b> 3            | $s_0$                                                            | output = even                                     |

|             |                       |                                                                  | done = 1                                          |

Final Page 5 of 8

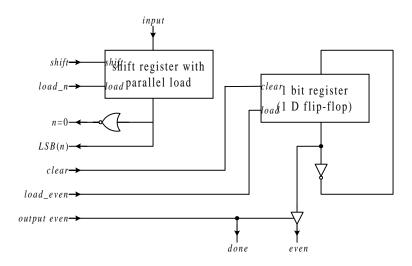

Other possible datapath:

## Datapath 2:

# Datapath 3:

Algorithm: Using a counter to count the number of ones and a "divider" to divide by two to see if it is even or odd.

Functional units require: counter, divider, comparator

Final Page 6 of 8

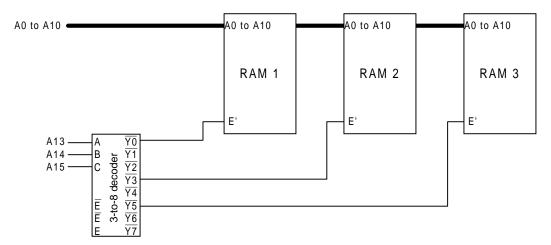

4. Given the following circuit for a memory system: (a) what are the starting addresses for the three RAM chips? (b) List all the addresses that would access the third location of RAM 1.(5)

Final Page 7 of 8

## Answer

(a)

RAM1 starting address: 0000, 0800, 1000, 1800 RAM2 starting address: 6000, 6800, 7000, 7800 RAM3 starting address: A000, A800, B000, B800 2 points for 0000, 6000, and A000 only.

2.5 points for all correct.

Reasoning:

|       | 15 | 14    | 13 | 12  | 11   | 10 | 9 | 8 | 7 | 6     | 5       | 4      | 3 | 2 | 1 | 0 |

|-------|----|-------|----|-----|------|----|---|---|---|-------|---------|--------|---|---|---|---|

|       | to | decod | er | not | used |    |   |   | d | ecode | d insid | le RAN | M |   |   |   |

| $Y_0$ | 0  | 0     | 0  | ×   | ×    | 0  | 0 | 0 | 0 | 0     | 0       | 0      | 0 | 0 | 0 | 0 |

| $Y_3$ | 0  | 1     | 1  | ×   | ×    | 0  | 0 | 0 | 0 | 0     | 0       | 0      | 0 | 0 | 0 | 0 |

| $Y_7$ | 1  | 1     | 1  | ×   | ×    | 0  | 0 | 0 | 0 | 0     | 0       | 0      | 0 | 0 | 0 | 0 |

(b)

Addresses that would access the third location of RAM 1:

2.5 points for all four correct addresses.

Reasoning:

| 15 | 14    | 13 | 12  | 11 | 10                   | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-------|----|-----|----|----------------------|---|---|---|---|---|---|---|---|---|---|

| to | decod | er | not |    | decoded inside RAM 1 |   |   |   |   |   |   |   |   |   |   |

| 0  | 0     | 0  | 0   | 0  | 0                    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0  | 0     | 0  | 0   | 1  | 0                    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0  | 0     | 0  | 1   | 0  | 0                    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0  | 0     | 0  | 1   | 1  | 0                    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

Final Page 8 of 8

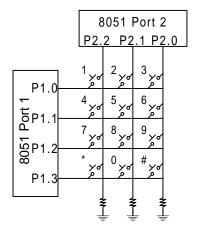

5. Given a 3×4 matrix keypad (like the telephone keypad) and the connections for the keypad to the 8051 as shown below. Note that each intersection of a vertical and horizontal wire is not connected unless the corresponding key is pressed.

- a) Which port (P1 or P2) should be the input port and which should be the output port? (1)

- b) Which one of the following code segments will return the correct key pressed? (2)

- ① P1 = 0x10;if (P2.2 == 0) return '1';

- ② P2 = 0x06; if(P1.2 == 0) return '7';

- ③ P1 = 0x04; if (P2.1 == 1) return '8';

- $9 ext{ P2} = 0x04;$ if (P1.3 == 1) return '\*';

- 9 P1 = 0x06; if(P2.0 == 1) return '6';

- c) Write a segment of C code (no longer than 5 lines) that will determine that there is no key pressed and return a space (''). (2)

#### Answer

a) P1 is the output port and P2 is the input port.

b) 3 2 points for this

```

c)

P1 = 0x0F;

if((P2.0 == 0) && (P2.1 == 0) && (P2.2 == 0)) return ';

2 points for this

```