Midterm 1 Page 1 of 5

# UNIVERSITY OF CALIFORNIA, RIVERSIDE

# Department of Computer Science and Engineering Department of Electrical Engineering CS/EE120B – Introduction to Embedded Systems Midterm 1 Version 2

26

| Name:_ | Solution Key         | Student ID#: |  |

|--------|----------------------|--------------|--|

|        | Please print legibly |              |  |

April 25, 2001

**Lab Section: 21** (TR 6-10):\_\_\_\_\_ **22** (WF 6-10):\_\_\_\_ **23** (WF 2-6):\_\_\_\_

(Numbers in parenthesis denote total possible points for question.)

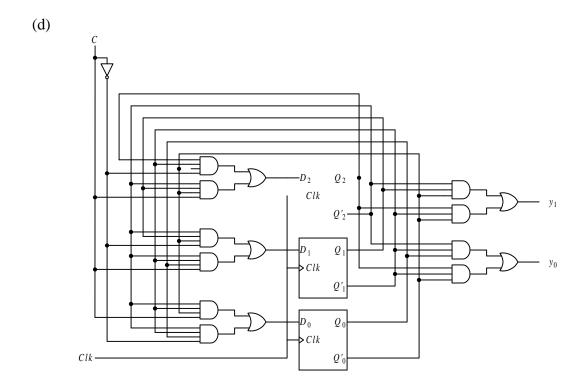

1. Draw a 4-bit shifter / rotator circuit having the following functional table

(4)

| $S_1$ | $S_0$ | Function     |

|-------|-------|--------------|

| 0     | 0     | Load         |

| 0     | 1     | Shift Left   |

| 1     | 0     | Rotate Right |

| 1     | 1     | No Change    |

### **Answer**

2. Are there any equivalent states in the following next-state/output table and if so, which states are equivalent? Give your reasons. (2)

| Current | Next State |            |         |         | Output |

|---------|------------|------------|---------|---------|--------|

| State   | CD = 00    | CD = 01    | CD = 10 | CD = 11 | Output |

| S1      | S2         | <b>S</b> 1 | S2      | S3      | 0      |

| S2      | S4         | <b>S</b> 3 | S1      | S2      | 0      |

| S3      | S2         | <b>S</b> 1 | S4      | S3      | 0      |

| S4      | S4         | S3         | S1      | S2      | 1      |

Midterm 1 Page 2 of 5

### Answer

There are NO equivalent states.

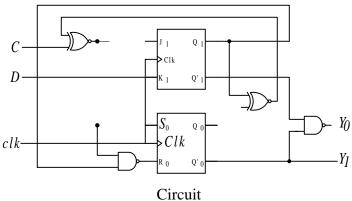

3. Derive (a) excitation equations, (b) characteristic equations, (c) next-state equations, (d) output equations, (e) next-state/output table, and (f) a state diagram for the circuit shown below. Be consistent with the label order for the inputs, states, and outputs, i.e. use the order CD,  $Q_1Q_0$ , and  $Y_1Y_0$  respectively; and use the state diagram template below to draw your state diagram. (12 points)

$$Q_1Q_0=01$$

## Answer

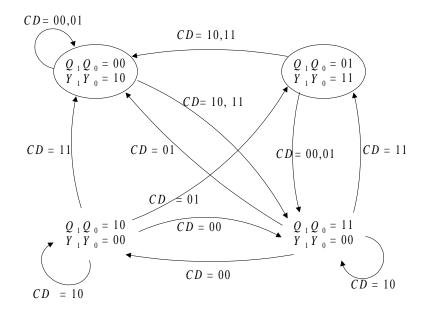

State diagram template to use for part (f).

(a) The excitation equations

$$J_1 = C \oplus Q_1 \oplus Q_0$$

$$K_1 = D$$

$$S_0 = C \oplus Q_1 \oplus Q_0$$

$$R_0 = [(C \oplus Q_1 \oplus Q_0) \ Q_1]'$$

(b) The characteristic equations

For the JK flip-flop:  $Q_{1next} = K'Q + JQ'$ For the SR flip-flop:  $Q_{0next} = S + R'Q$  Midterm 1 Page 3 of 5

# (c) The next-state equations

$$Q_{1next} = K_1'Q_1 + J_1Q_1'$$

$$= D'Q_1 + (C \oplus Q_1 \oplus Q_0)Q_1'$$

$$Q_{0next} = S_0 + R_0'Q_0$$

$$= (C \oplus Q_1 \oplus Q_0) + (C \oplus Q_1 \oplus Q_0) Q_1Q_0$$

$$= (C \oplus Q_1 \oplus Q_0)$$

# (d) The output equations

$$Y_1 = Q_0'$$

$Y_0 = (Q_1'Q_0')' = Q_1 + Q_0$

# (e) The next-state/output table

| Present  | Next State                     |       |       |       | Outputs  |

|----------|--------------------------------|-------|-------|-------|----------|

| State    | $Q_{1\  m next}Q_{0\  m next}$ |       |       |       |          |

| $Q_1Q_0$ | CD=00                          | CD=01 | CD=10 | CD=11 | $Y_1Y_0$ |

| 00       | 00                             | 00    | 11    | 11    | 10       |

| 01       | 11                             | 11    | 00    | 00    | 01       |

| 10       | 11                             | 01    | 10    | 00    | 11       |

| 11       | 10                             | 00    | 11    | 01    | 01       |

# (f) The state diagram

Midterm 1 Page 4 of 5

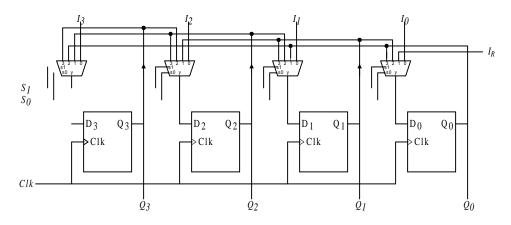

4. Use the "almost-one-hot" encoding and D flip-flops to synthesize a modulo-4 up counter with a count enable input C. The state for count 0 is also the initial state. The initial state is the next state for all the unused state combinations. The count is outputted as two bits  $y_1$  and  $y_0$ . You need to do the following:

(a) Derive the next-state/output table and the implementation tables. (2)

(b) Derive the excitation equations for the inputs to the D flip-flops. Do not simplify the equations. (2)

(c) Derive the output equations. Do not simplify the equations. (2)

(d) Draw the circuit. (2)

### Answer

(a) The next-state/output table (which is the same as the implementation table is shown below:

| Current State | Next State $Q_{2next} Q_{1next} Q_{0next}$ |              | Output                                      |

|---------------|--------------------------------------------|--------------|---------------------------------------------|

| $Q_2Q_1Q_0$   | C = 0                                      | <i>C</i> = 1 | <i>y</i> <sub>1</sub> <i>y</i> <sub>0</sub> |

| 000           | 000                                        | 001          | 00                                          |

| 001           | 001                                        | 010          | 01                                          |

| 010           | 010                                        | 100          | 10                                          |

| 100           | 100                                        | 000          | 11                                          |

(b)

$$D_2 = Q_2 Q_1' Q_0' C' + Q_2' Q_1 Q_0' C'$$

$D_1 = Q_2' Q_1 Q_0' C' + Q_2' Q_1' Q_0 C$

$D_0 = Q_2' Q_1' Q_0' C + Q_2' Q_1' Q_0 C'$

(c)

$$y_1 = Q_2'Q_1Q_0' + Q_2Q_1'Q_0'$$

$y_0 = Q_2'Q_1'Q_0 + Q_2Q_1'Q_0'$

Midterm 1 Page 5 of 5