Technology Mapping Page 1 of 4

## **Technology Mapping**

To reduce implementation cost and turnaround time, designers use gate-arrays.

These gate-arrays contains only m-input NAND and NOR gates where m is usually 3.

**Technology mapping** is the process where we convert a schematic (expression) with AND, OR, and NOT gates to NAND and NOR gates.

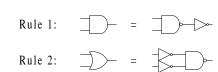

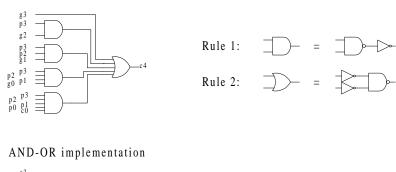

The conversion is based on the following rules:

Rule 1:

$$xy = ((xy)')'$$

Rule 2:

$$x + y = ((x + y)')' = (x'y')'$$

Rule 3:

$$xy = ((xy)')' = (x' + y')'$$

Rule 4:

$$x + y = ((x + y)')'$$

Rule 5:

$$x'' = x$$

Replace AND and OR gates with NAND gates by using Rules 1 and 2. Replace AND and OR gates with NOR gates by using Rules 3 and 4. Eliminate double inverters whenever possible by using Rule 5.

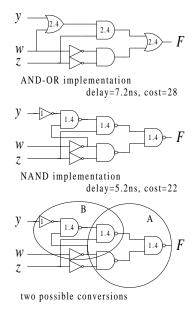

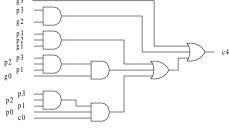

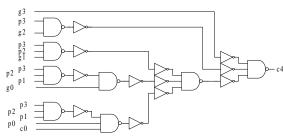

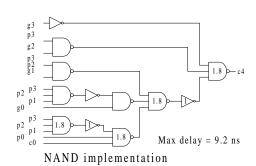

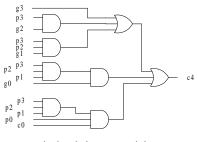

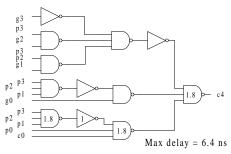

Example: Derive the NAND and NOR implementations of the carry function  $c_{i+1} = x_i y_i + x_i c_i + y_i c_i$

A better NOR implementation is to start with the product-of-sums expression  $c_{i+1} = (x_i + y_i)(x_i + c_i)(y_i + c_i)$

Technology Mapping Page 2 of 4

## Translation of Sum of Products and Product of Sums to NAND and NOR schematics:

| Form type          | Standard form<br>Implementation | NAND<br>Implementation | NOR<br>Implementation |

|--------------------|---------------------------------|------------------------|-----------------------|

| Sum of products    |                                 |                        |                       |

| Product<br>of sums |                                 |                        |                       |

## Four more identities:

**Technology Mapping** Page 3 of 4

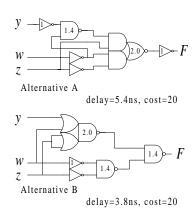

Example: Implement the following schematic using 2 and 3-input NAND gates:

using only 2 & 3-input gates

convert to NAND implementation

optimized decomposition

optimized NAND implementation

Technology Mapping Page 4 of 4

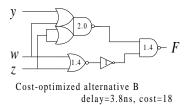

Example: Convert the expression w'z' + z(w + y) into a logic schematic using any of the gates from the library defined in Tables 3.14, 3.15 and 3.16.