Final Page 1 of 8

# UNIVERSITY OF CALIFORNIA, RIVERSIDE

# **Department of Computer Science and Engineering Department of Electrical Engineering** CS/EE120A - Logic Design **Final**

March 22, 2001

35

| Name: Solution Key        |                     | Student ID#:         |  |  |  |

|---------------------------|---------------------|----------------------|--|--|--|

| Please print legi         | bly                 |                      |  |  |  |

| Lab Section: 21 (MW 3-6): | <b>22</b> (TR 2-5): | <b>23</b> (MF 8-11): |  |  |  |

(Numbers in parenthesis denote total possible points for question.)

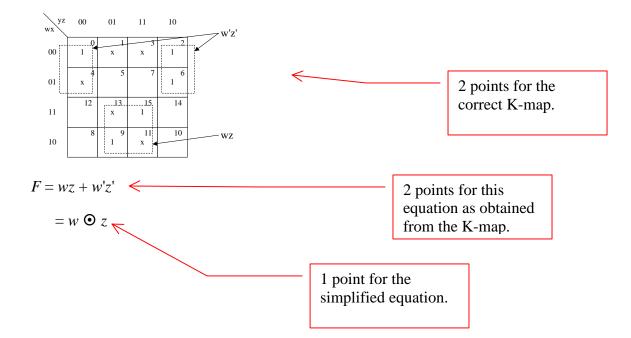

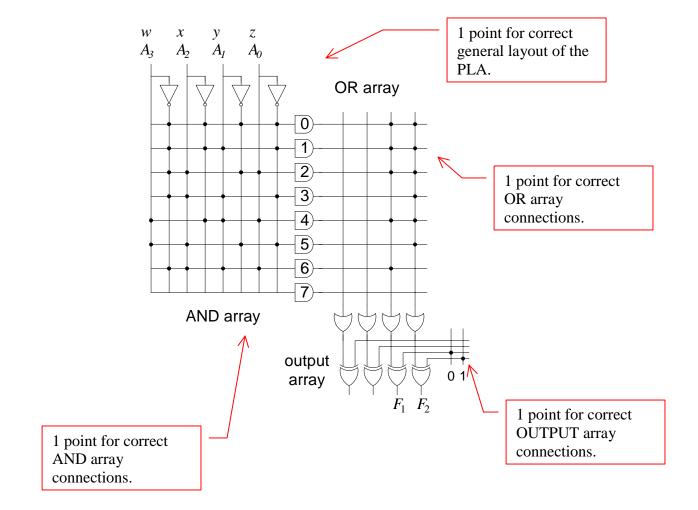

1. Use one  $4 \times 8 \times 4$  PLA (4 input columns, 8 rows of AND gates and 4 columns of OR gates) to implement the following two functions: (5)

$$F_1(w,x,y,z) = \Sigma(0,2,5,7,11)$$

$$F_2(w,x,y,z) = \Sigma(1,3,4,7,8,9,10,13,14,15)$$

#### Answer

There are not enough AND gates to implement both functions directly. We will implement  $F_2' = \Sigma(0,2,5,6,11,12)$  using 6 minterms of which 4 minterms are the same as those for  $F_1$ .  $F_1$ requires one more minterm  $m_7$  that is not yet implemented from  $F_2$ . So there are only a total of 7 minterms for the 2 equations. Thus, the following connection:

> 1 point for realizing that we need to implement  $F_1$  and  $F_2$ ' and knowing the correct minterms to implement.

Final Page 2 of 8

Final Page 3 of 8

2. Write the VHDL code at the dataflow level that solves the following problem. You need to have both the entity and architecture sections. (5)

Input (given) a 4-bit data. Output a '1' if there are odd number of 1 bits in the data, otherwise, output a '0'.

#### Answer

There can be several correct answers to this problem. Below are two possible solutions:

Must have the following entity defined for all solutions:

```

library IEEE;

use ieee.std_logic_1164.all;

2 points for getting

ENTITY EvenParity IS

PORT ( D : IN std logic vector(3 downto 0);

the correct entity.

F : OUT std logic );

END EvenParity;

```

#### Solution 1:

```

ARCHITECTURE Dataflow OF EvenParity IS

BEGIN

with D select

1 point for the

F \le '1' \text{ when } "0001" \mid "0010" \mid "0100" \mid "0111" \mid

overall architecture

"1000" | "1011" | "1101" | "1110",

structure.

'0' when others;

END Dataflow;

Solution 2:

ARCHITECTURE Dataflow OF EvenParity IS

BEGIN

F \le '1' \text{ when } D = "0001" \text{ or } D = "0010"

or D = "0100" or D = "0111"

or D = "1000" or D = "1011"

2 points for the

or D = "1101" or D = "1110"

correct dataflow

else '0';

code.

END Dataflow;

```

Deduct 2 points if code is written in behavioral level, i.e. using a process statement and / or case statement.

Final Page 4 of 8

3. Design a simplified combinational circuit that solves the problem in question 2 above. You need to come up with the truth table, the simplified function, and finally the circuit. (5)

### **Answer**

| $d_3$ | $d_2$ | $d_1$ | $d_0$ | $\boldsymbol{F}$ |    |          |

|-------|-------|-------|-------|------------------|----|----------|

| 0     | 0     | 0     | 0     | 0                |    |          |

| 0     | 0     | 0     | 1     | 1                |    |          |

| 0     | 0     | 1     | 0     | 1                |    |          |

| 0     | 0     | 1     | 1     | 0                |    |          |

| 0     | 1     | 0     | 0     | 1                |    |          |

| 0     | 1     | 0     | 1     | 0                |    |          |

| 0     | 1     | 1     | 0     | 0                | K  |          |

| 0     | 1     | 1     | 1     | 1                | '\ |          |

| 1     | 0     | 0     | 0     | 1                |    | 2 point  |

| 1     | 0     | 0     | 1     | 0                |    | the trut |

| 1     | 0     | 1     | 0     | 0                |    |          |

| 1     | 0     | 1     | 1     | 1                |    |          |

| 1     | 1     | 0     | 0     | 0                |    |          |

| 1     | 1     | 0     | 1     | 1                |    |          |

| 1     | 1     | 1     | 0     | 1                |    |          |

| 1     | 1     | 1     | 1     | 0                |    |          |

|       | •     | •     |       |                  | •  |          |

2 points for getting the truth table.

F = w'x'y'z + w'x'yz' + w'xy'z' + w'xyz + wx'y'z' + wx'yz + wxyz'

$= w'x'(y \oplus z) + w'x(y \oplus z)' + wx'(y \oplus z)' + wx(y \oplus z)$

$= [(y \oplus z) (w \oplus x)'] + [(y \oplus z)' (w \oplus x)]$

$= w \oplus x \oplus y \oplus z$

1 point for getting the correct but not simplified equation.

2 points for getting the correct simplified circuit.

The circuit can also be a 4-input XOR gate.

Final Page 5 of 8

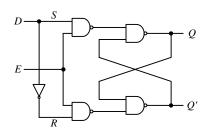

4. Design a D latch with active high enable using only NAND gates and inverters. The primary external signals are *D*, *E*, *Q*, and *Q'*. Clearly label these signals in your circuit. Also, write the truth table for the circuit. (5)

### **Answer**

3 points for getting the circuit correct.

| E | D | Q | Qnext | $Q_{next}'$ |

|---|---|---|-------|-------------|

| 0 | × | 0 | 0     | 1           |

| 0 | × | 1 | 1     | 0           |

| 1 | 0 | × | 0     | 1           |

| 1 | 1 | × | 1     | 0           |

2 points for getting the truth table correct.

Final Page 6 of 8

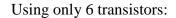

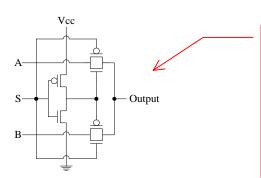

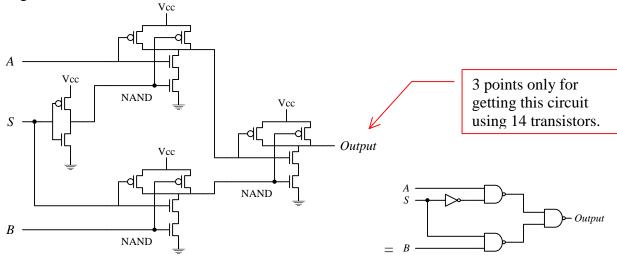

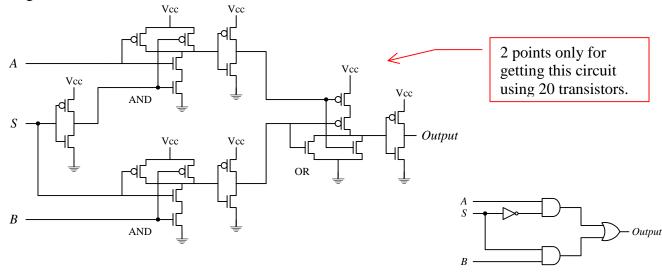

5. Design a 2-to-1 mux using as few CMOS transistors as possible. There should be only three inputs labeled *A*, *B*, and *S*. (5)

#### **Answer**

5 points for getting this circuit using only 6 transistors.

4 points only if it has both *S* and *S'*, i.e. without the inverter.

# Using 14 transistors:

## Using 20 transistors:

Final Page 7 of 8

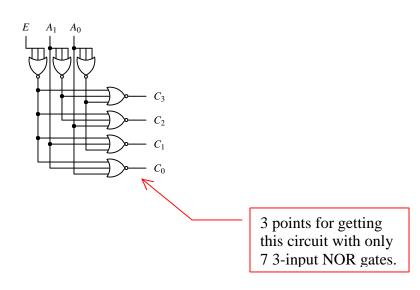

6. Design a 2-to-4 decoder using only 3-input NOR gates. To get full credit, you need to use as few gates as possible. (5)

### **Answer**

The truth table for the 2-to-4 decoder is as follows:

| E | $A_1$ | $A_0$ | $C_3$ | $C_2$ | $C_1$ | $C_0$ |

|---|-------|-------|-------|-------|-------|-------|

| 0 | ×     | ×     | 0     | 0     | 0     | 0     |

| 1 | 0     | 0     | 0     | 0     | 0     | 1     |

| 1 | 0     | 1     | 0     | 0     | 1     | 0     |

| 1 | 1     | 0     | 0     | 1     | 0     | 0     |

| 1 | 1     | 1     | 1     | 0     | 0     | 0     |

Deduct 2 points if it does not have an enable *E* input.

The equations are:

$$C_3 = EA_1A_0$$

$$C_2 = EA_1A_0'$$

$$C_1 = EA_1'A_0$$

$$C_0 = EA_1'A_0'$$

2 points for getting the correct equations.

To change the AND gates to NOR gates, we use the equality:

$$xyz = ((xyz)')' = (x' + y' + z')'$$

To change inverters to NOR gates, we simply connect the inputs together.

Thus, we get the following circuit:

Final Page 8 of 8

7. Simplify a four-literal (w, x, y, z) Boolean expression with the following 1-minterms and "don't-care"-minterms to use as few gates as possible:

#### Answer: