### UNIVERSITY OF CALIFORNIA RIVERSIDE

Functional Partitioning for Low Power

A Dissertation submitted in partial satisfaction of the requirements for the degree of

> Doctor of Philosophy in Computer Science by Enoch Oi-Kee Hwang June, 1999

Dissertation Committee: Dr. Frank Vahid, Chairperson Dr. Yu-Chin Hsu, Co-Chairperson Dr. Yang-Chang Hong

Copyright by Enoch Oi-Kee Hwang 1999 The Dissertation of Enoch Oi-Kee Hwang is approved:

Committee Co-Chairperson N Committee Chairperson

University of California, Riverside

### Acknowledgments

I want to thank my professors Dr. Frank Vahid and Dr. Yu-Chin Hsu for all the support and help given to me.

### Dedication

I want to dedicate this work to my loving wife Windy, my son Jonathan and my second expecting child.

#### Abstract of the Dissertation

#### Functional Partitioning for Low Power

by

#### Enoch Oi-Kee Hwang

### Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, June, 1999 Dr. Frank Vahid, Chairperson Dr. Yu-Chin Hsu, Co-Chairperson

Power reductions in VLSI systems have recently become a critical metric for design evaluation. Although power reduction techniques can be applied at every level of design abstraction, most automated power reduction techniques apply to the lower levels of design abstraction. Previous works have shown that sizable power reductions can be achieved simply by shutting down a system's sub-circuits when they are not needed. However, these shutdown techniques focus on shutting down only portions of the controller or the datapath of a single custom hardware processor. We therefore investigated the power reduction attainable by the evolving automated technique of functional partitioning in which a process is automatically divided into multiple simpler, mutually exclusive, communicating processors, and then shut down the inactive processors. By shutting down the entire inactive processor, we have in effect shut down both the controller and datapath. Power reduction is accomplished because only one smaller processor is active at a time. We have applied this functional partitioning technique to either the procedural or the finite-state machine with datapath (FSMD) behavioral level. From either level, the original process is partitioned into multiple parts. For the procedural level, a coarse-grained partitioning of procedures is done. Data transfers between the parts are simply the parameters in the procedural call. In contrast, FSMD partitioning has no concept of procedures, but rather states. A dataflow analysis is first performed to determine the data transfers between the parts. A power partitioning algorithm is then used to separate the states into multiple parts. The parts are then individually synthesized down to the gate level netlist. Finally, communication is added between the parts so that they are functionally equivalent to the original unpartitioned process.

Partitioning introduces extra power consumption for inter-processor communication. Thus, the problem that must be solved is one of partitioning such that the reduction in power for computations far outweighs the power increase for communication, while also minimizing the increase in total circuit size and execution time. Our results show that this functional partitioning technique can reduce power, on average, by 42% over unoptimized systems. In addition to power reduction, functional partitioning also provides solutions to a variety of synthesis problems.

## **Table of Contents**

| Table of Contents                                                           | viii |

|-----------------------------------------------------------------------------|------|

| List of Tables                                                              | xi   |

| List of Figures                                                             | xii  |

| Chapter 1. Introduction                                                     | 1    |

| References                                                                  |      |

| Chapter 2. Previous Work                                                    | 10   |

| 2.1. Transistor Level                                                       | 10   |

| 2.1.1. Transistor Sizing                                                    | 10   |

| 2.1.2. Transistor Reordering                                                | 10   |

| 2.2. Logic Gate Level                                                       | 11   |

| 2.2.1. Technology-independent                                               | 12   |

| 2.2.2. Technology-dependent                                                 |      |

| 2.3. Register Transfer Level                                                |      |

| 2.3.1. Sequential Circuit                                                   |      |

| 2.3.2. Combinational Circuit                                                | 14   |

| 2.4. Behavioral Level                                                       |      |

| 2.5. System Level                                                           | 17   |

| 2.6. Summary                                                                | 18   |

| References                                                                  | 19   |

| Chapter 3. Power Consumption                                                | 23   |

| 3.1. Power Dissipation                                                      |      |

| 3.1.1. Static Power Dissipation                                             | 24   |

| 3.1.2. Dynamic Power Dissipation due to Short-Circuit                       | 25   |

| 3.1.3. Dynamic Power Dissipation due to Capacitive Charging and Discharging | g26  |

| 3.2. Power Calculation                                                      | 28   |

| 3.3. Power Reduction                                                        | 30   |

| 3.4. Summary                                                                | 33   |

| References                                                                  | 34   |

| Chapter 4. Procedural Functional Partitioning                               |      |

| 4.1. Behavioral Synthesis                                                   | 35   |

| 4.2. Structural Partitioning                                |    |

|-------------------------------------------------------------|----|

| 4.3. Procedural Functional Partitioning                     |    |

| 4.4. Procedural Functional Partitioning Example             |    |

| 4.5. Summary                                                |    |

| References                                                  | 47 |

| Chapter 5. FSMD Functional Partitioning                     |    |

| 5.1. FSMD Definition                                        |    |

| 5.2. FSMD Functional Partitioning Technique                 |    |

| 5.3. Dataflow Analysis                                      |    |

| 5.3.1. Basic Dataflow Analysis                              |    |

| 5.3.2. Partition Dataflow Analysis                          | 54 |

| 5.4. FSMD Refinement                                        |    |

| 5.5. Preserving the Cycle-By-Cycle Behavior                 |    |

| 5.6. Critical Path Analysis                                 |    |

| 5.7. Preserving the Critical Path                           | 61 |

| 5.8. Summary                                                |    |

| References                                                  | 63 |

| Chapter 6. Power Estimation Model                           | 64 |

| 6.1. Internal Energy                                        |    |

| 6.2. FSMD Complexity                                        |    |

| 6.3. External Energy                                        |    |

| 6.4. Finding the Energy Bounds                              |    |

| 6.4.1. Internal energy bounds                               |    |

| 6.4.2. External energy bounds                               |    |

| 6.4.3. Partitioned energy bounds                            |    |

| 6.5. Model accuracy                                         |    |

| 6.6. Summary                                                |    |

| References                                                  |    |

| Chapter 7. Partitioning Algorithm and Heuristic             |    |

| 7.1. Branch-and-Bound                                       |    |

| 7.2. Simulated Annealing                                    |    |

| 7.3. Summary                                                |    |

| References                                                  |    |

| Chapter 8. Experiments and Results                          |    |

| 8.1. Power Reduction for Procedural Functional Partitioning |    |

| 8.2. Power Reduction for FSMD Functional Partitioning       |    |

| 8.3. Power Usage Breakdown by Processor Components          |    |

| 8.4. Critical Path                                          |    |

| 8.5. Partitioning Algorithm and Heuristic                   |    |

| 8.6. Internal to External Energy Ratios                     |    |

| 8.7. Power Saving Techniques Compared                       |    |

| 8.8. Summary                                                |    |

| y                                                           |    |

| Referenc   | es         |  |

|------------|------------|--|

| Chapter 9. | Conclusion |  |

## **List of Tables**

| Table 7.1. Sample energy data.                                                | 77 |

|-------------------------------------------------------------------------------|----|

| Table 8.1. Procedural functional partitioning example statistics.             | 85 |

| Table 8.2. Procedural functional partitioning power reduction results.        | 86 |

| Table 8.3. FSMD functional partitioning example statistics                    | 88 |

| Table 8.4. FSMD functional partitioning power reduction results.              | 89 |

| Table 8.5. Breakdown of power consumption by components.                      | 90 |

| Table 8.6. Critical path and execution time results.                          | 92 |

| Table 8.7. Results from Branch-and-Bound and Simulated Annealing partitioning | 93 |

| Table 8.8. Branch-and-Bound statistics.                                       | 95 |

| Table 8.9. Effects of different external to internal energy ratios.           | 96 |

# **List of Figures**

| Figure 1.1. Sample unpartitioned FSMD code                                                                                                                                                                                                                                                                                                                                                                                                                              | 3    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.2. Unoptimized RTL design exmple                                                                                                                                                                                                                                                                                                                                                                                                                               | 4    |

| Figure 1.3. Guarded evaluation technique.                                                                                                                                                                                                                                                                                                                                                                                                                               | 4    |

| Figure 1.4. Selectively-clocked FSM technique.                                                                                                                                                                                                                                                                                                                                                                                                                          | 5    |

| Figure 1.5. FSMD functional partitioning technique.                                                                                                                                                                                                                                                                                                                                                                                                                     | 7    |

| Figure 2.1. Transistor implementation of a 2-input NAND gate.                                                                                                                                                                                                                                                                                                                                                                                                           | . 11 |

| Figure 2.2. Precomputation example of a comparator.                                                                                                                                                                                                                                                                                                                                                                                                                     | . 14 |

| Figure 2.3. Guarded evaluation technique: (a) unoptimized RTL circuit, and (b) optimized with transparent latches.                                                                                                                                                                                                                                                                                                                                                      |      |

| Figure 3.1. CMOS inverter model for static power dissipation evaluation                                                                                                                                                                                                                                                                                                                                                                                                 | . 24 |

| Figure 3.2. Parasitic diodes in a CMOS inverter                                                                                                                                                                                                                                                                                                                                                                                                                         | . 25 |

| Figure 3.3. Variables affecting power consumption.                                                                                                                                                                                                                                                                                                                                                                                                                      | . 28 |

| Figure 3.4. Sample netlist with four gates and six nets. The gates are annotated with the gate capacitance and the nets are annotated with the toggle count                                                                                                                                                                                                                                                                                                             | 30   |

| Figure 3.5. Combinational logic with: (a) common inputs, (b) latched inputs, and (c) partitioned inputs.                                                                                                                                                                                                                                                                                                                                                                |      |

| Figure 4.1. Example of the three levels of abstraction: (a) behavioral, (b) structural, and (c) physical.                                                                                                                                                                                                                                                                                                                                                               |      |

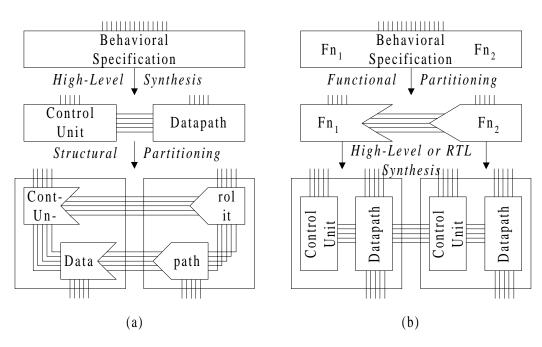

| Figure 4.2. Partitioning: (a) structurally, (b) functionally                                                                                                                                                                                                                                                                                                                                                                                                            | . 38 |

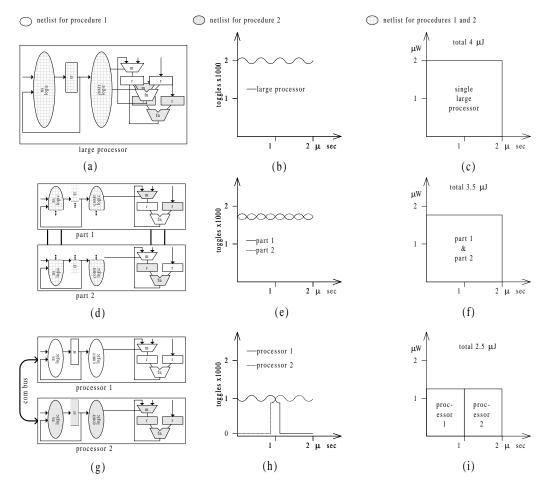

| Figure 4.3. Netlist with control unit and datapath, hypothetical switching activity, and power usage of processor with two procedures: (a) single large processor with two procedures; (b) switching activity of large processor; (c) power usage of large processor; (d) structural partitioning of processor; (e) switching activity of (d); (f) power usage of (d); (g) functional partitioning of processor; (h) switching activity of (g); (i) power usage of (g). | . 40 |

| Figure 4.4. Sample unpartitioned pseudo-code                                                                                                                                                                                                                                                                                                                                                                                                                            | . 43 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Figure 4.5. Sample partitioned pseudo-code                                                                                                                                                                                                   | 43 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

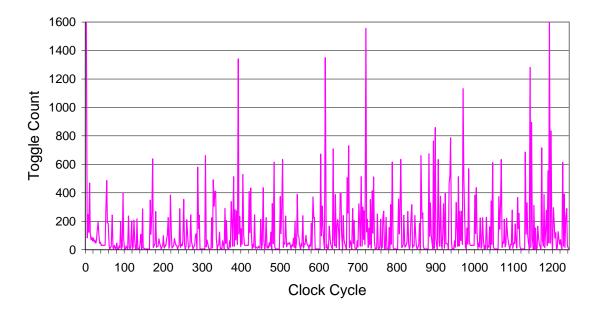

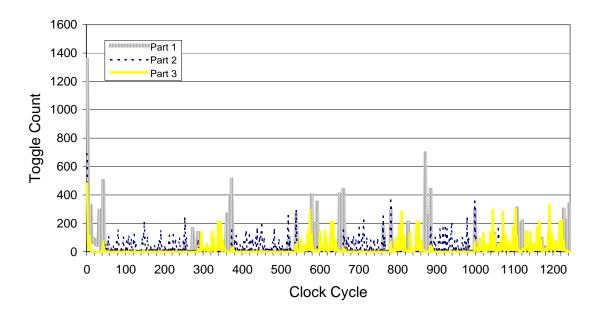

| Figure 4.6. Plot of switching activities for the <i>Fac</i> unpartitioned example. Total power is 19 mWatt.                                                                                                                                  | 44 |

| Figure 4.7. Plot of switching activities for the <i>Fac</i> partitioned example. Total power is 11 mWatt.                                                                                                                                    | 45 |

| Figure 5.1. Sample unpartitioned FSMD code                                                                                                                                                                                                   | 49 |

| Figure 5.2. FSMD functional partitioning algorithm.                                                                                                                                                                                          | 50 |

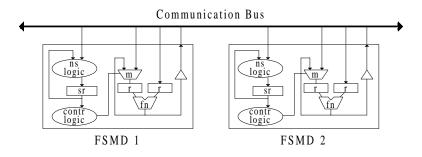

| Figure 5.3. Architectural model.                                                                                                                                                                                                             | 51 |

| Figure 5.4. Basic dataflow analysis algorithm.                                                                                                                                                                                               | 53 |

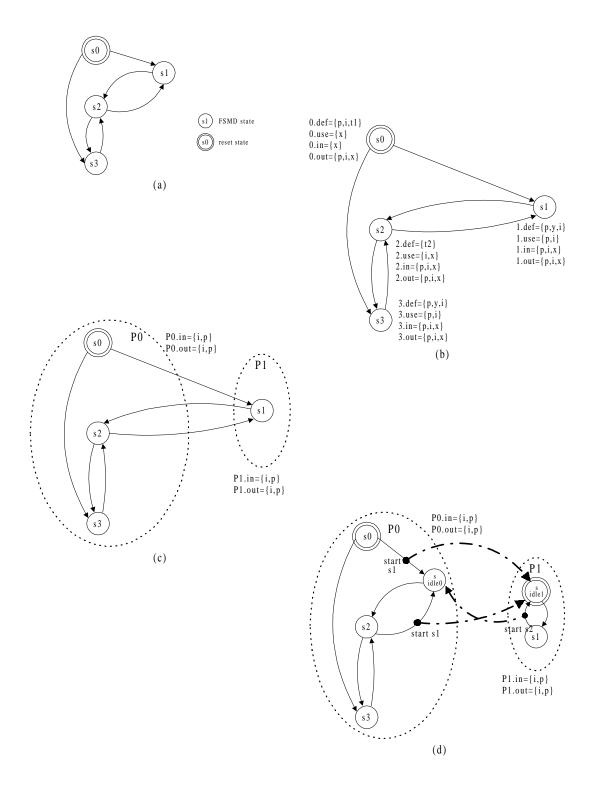

| Figure 5.5. (a) Control flow graph for Figure 5.1, (b) after basic dataflow analysis, (c) after partition dataflow analysis, and (c) result after refinement.                                                                                | 55 |

| Figure 5.6. Partition dataflow analysis algorithm.                                                                                                                                                                                           | 56 |

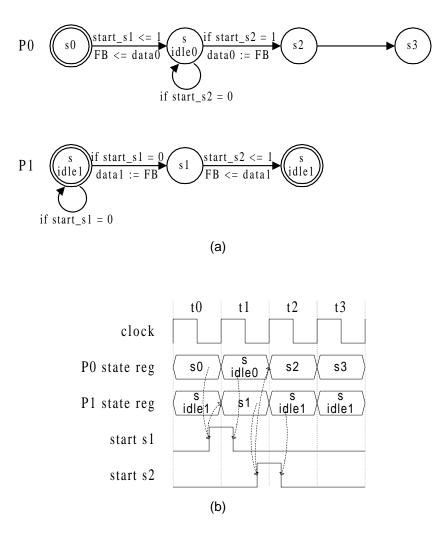

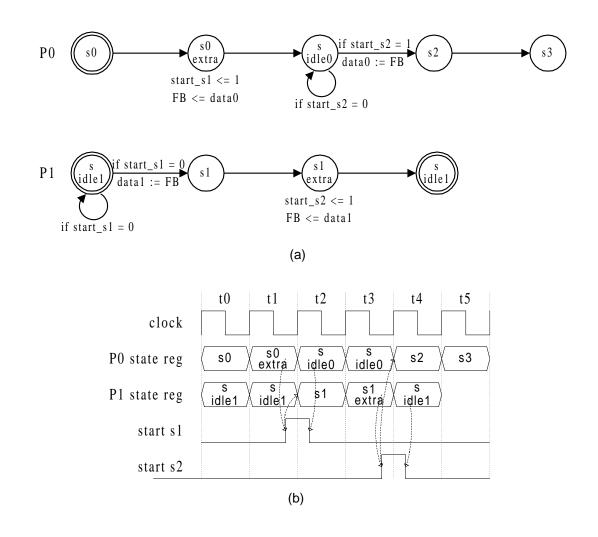

| Figure 5.7. Cycle-by-cycle behavior preservation: (a) execution, and (b) transition timing diagram.                                                                                                                                          | 59 |

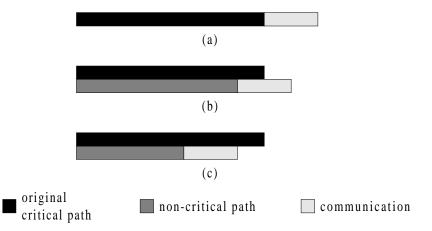

| Figure 5.8. Three different situations for adding the communication operations: (a) extending the critical path from original critical path, (b) extending the critical path from non-critical path, and (c) not extending the critical path | 60 |

| Figure 5.9. Critical path preservation: (a) execution, and (b) transition timing diagram.                                                                                                                                                    | 61 |

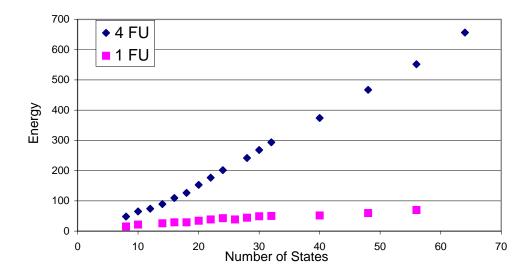

| Figure 6.1. Energy versus the number of identical states for a FSMD with one and four functional units.                                                                                                                                      | 67 |

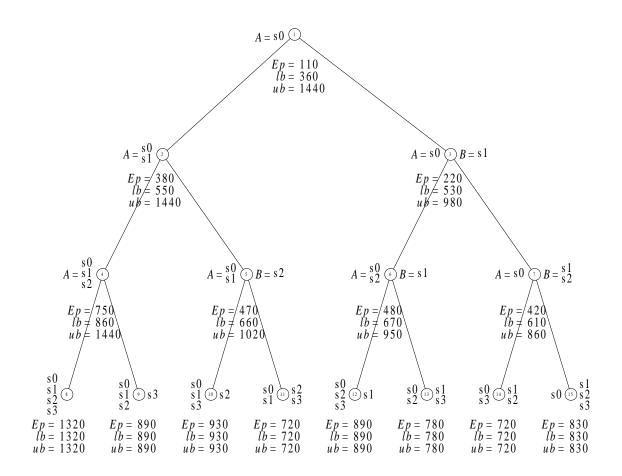

| Figure 7.1. Sample branch-and-bound binary tree                                                                                                                                                                                              | 78 |

| Figure 7.2. Simulated annealing heuristic                                                                                                                                                                                                    | 79 |

| Figure 7.3. Initial cost function.                                                                                                                                                                                                           | 81 |

| Figure 7.4. Incremental cost function                                                                                                                                                                                                        | 82 |

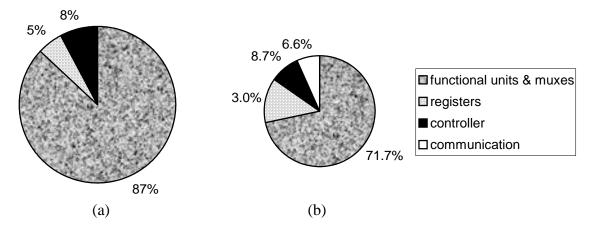

| Figure 8.1. Breakdown of power consumption by parts for: (a) unpartitioned, and (b) partitioned system                                                                                                                                       | 91 |

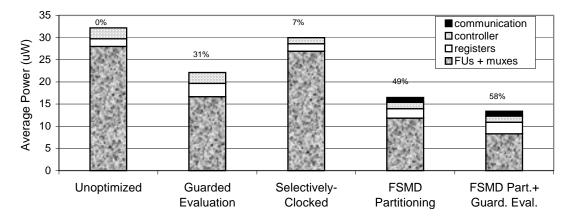

| Figure 8.2. Average power savings compared. Percentages show power savings.<br>Shorter bars are better                                                                                                                                       | 97 |

# **Chapter 1. Introduction**

Electronic circuit optimization for area and timing has been well studied. Recently, power consumption has become one of the more critical design parameters for very large scale integration (VLSI) systems. The reduction of area for an integrated circuit (IC), which was a big issue not too long ago, is not as big an issue today because with new IC production technologies, many millions of transistors can be put on a single IC. On the other hand, there is a trend towards portable battery operated devices. The shrinking sizes of integrated circuits calls for reduced power consumption in order to extend battery life for these portable devices. Furthermore, in the deep submicron technologies, there is a limitation of circuit density because of excessive heat generation from high power dissipation. Hence, power consumption is now one of the most important criteria in circuit designs.

While power reduction techniques can be applied at every level of design abstraction, most of the previous power optimization techniques apply to the lower levels of the design process; namely transistor and logic gate levels [1]. Recently, there is a focus on power reduction at the higher levels [2] where large power savings are possible merely by cutting down on wasted power in the circuit. We therefore investigate the power reduction attainable by the evolving automated behavioral level technique of functional partitioning.

Power is consumed when capacitors in the circuit are either charged or discharged due to switching activities. Power reduction at the higher levels is mainly achieved through the reduction of these switching activities by shutting down portions of the system when they are not needed [2]. The idea is that for a large system, not all components are required to be active at all times and thus, large power savings are possible merely by cutting down on wasted switching activities. Large VLSI circuits such as processors contain different components such as the controller, memory and functional units. Recent high-level shutdown techniques focus on shutting down only portions of the controller or the functional units of a single custom hardware processor. Two such areas of shutdown techniques for power reduction have been addressed in recent literature.

In *datapath* shutdown techniques, portions of the combinational logic in the datapath can be shut down for some cycles when those results are either precomputed or are not required. In [3], the output values are selectively *precomputed* using a few high order bits one cycle before they are needed. If precomputation (e.g., comparing the highest bits of a 32-bit comparison) indicates that the full computation is not necessary, then the entire original logic circuit can be turned off in the next clock cycle. Thus, switching activity is reduced and power is saved. The *guarded evaluation* technique in [4] tries to determine, on a per clock cycle basis, which part, of a combinational circuit are computing results

that will be used, and which are not. The parts that are not needed are then shut off, thus saving the power used in all the useless transitions in that part of the circuit.

For example, given the FSMD description in Figure 1.1, the corresponding unoptimized RTL description is shown in Figure 1.2. Suppose that the input for x is 0 in the FSMD code, then only states s0 and s3 will be executed, and so neither the adder nor the multiplier will be needed. These two functional units will be wasting power in the unoptimized circuit of Figure 1.2 because they will have switching activities even though

```

loop

case State Var is

when s0 =>

p := 1;

i := 1;

if (1 < x) then -- x is a primary input

State_Var := s1;

else

y \leq p;

State_Var := s3;

end if;

when s1 =>

p := p * 2;

y \leq p;

i := i + 1;

State Var := s2;

when s2 =>

if (i < x) then

State_Var := s1;

else

State_Var := s3;

end if;

when s3 =>

p := p - 1;

y <= p;

i := i - 1;

State_Var := s2;

end case;

end loop;

```

Figure 1.1. Sample unpartitioned FSMD code.

their results will not be needed. Furthermore, the controller can also be reduced to save power.

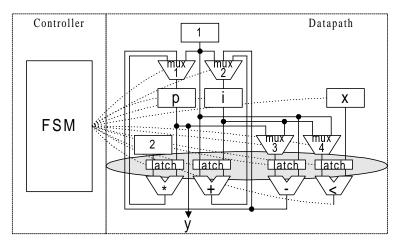

Figure 1.3 shows the result of applying the guarded evaluation technique to the unoptimized circuit of Figure 1.2. Latches are added in front of all the functional units. Since only the comparator and the subtract unit are needed in the execution of states s0

Figure 1.2. Unoptimized RTL design exmple.

Figure 1.3. Guarded evaluation technique.

and s3, the inputs to the adder and multiplier can be latched, thus, preventing the inputs from changing. Power is saved because there will be no switching activities in these two functional units during the execution of states s0 and s3.

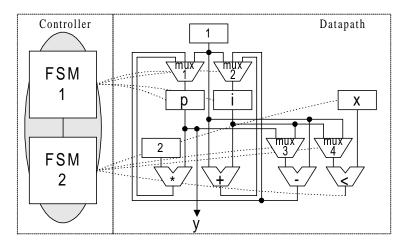

In *controller* shutdown techniques [5][6], the controller is partitioned into two or more mutually exclusive interacting FSMs and their clocks are selectively gated. Each FSM controls the execution of one section of computation. Only one of the interacting FSMs is active at any given clock cycle, while all the others are idle and their clock is stopped. Figure 1.4 shows an example of applying the selectively-clocked FSM technique. Here we have split the original FSM into two sub-FSMs. FSM1 includes state s1 which controls the portion of the datapath for the multiplier and adder while FSM2 includes states s0, s2, and s3, which controls the portion of the comparator and subtract unit. Since we only need the use of the comparator and subtract unit to execute states s0 and s3, FSM1 can be made inactive by stopping the clock to it.

Figure 1.4. Selectively-clocked FSM technique.

The power savings from this technique come directly from the fact that there are multiple smaller FSMs instead of one large one. As a result, we have a shorter local clock line, fewer states, and simpler and smaller next state logic. While this method prevents unnecessary power consumption in the control unit, there is no power reduction in the datapath.

While the above mentioned techniques show significant power reductions, they focus only on either the datapath or the controller for a single custom processor. It was recognized in [4] and [5] that the power savings would be even larger if both the controller and the datapath were considered together and if the techniques were applied on the complete circuit, rather than on individual blocks. Hence, we propose a new functional partitioning shutdown technique for reducing power where both the controller *and* the datapath are considered together.

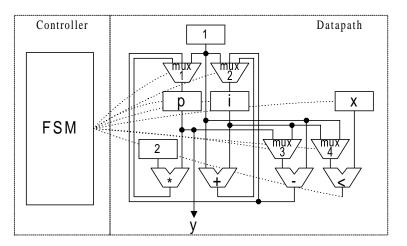

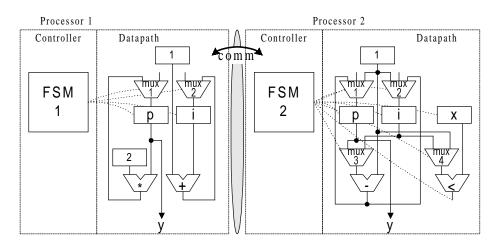

Our functional partitioning technique for power reduction is based on the finite state machine with datapath (FSMD) model. Instead of trying to separately optimize individual components of a system and then trying to combine the different optimized circuits together, our technique optimizes the original monolithic system by partitioning it. The original FSMD is first partitioned into several smaller mutually exclusive FSMDs. Each of these smaller FSMDs is then synthesized to its own custom processor, each having its own controller and datapath. The reason why FSMD functional partitioning can significantly reduce power is that each processor is smaller than the original one large processor implementing the entire process, and only one processor is executing a computation at any given time while the other processors will be idle. When a processor is idle, we have, in effect, shut down both the controller and the datapath for that processor. Thus, greater power saving is possible.

Figure 1.5 shows the result of applying the FSMD functional partitioning technique to the sample circuit of Figure 1.2. Here, we have two smaller mutually exclusive processors. The first processor contains the controller and datapath for executing state s1, and the second processor contains the controller and datapath for executing states s0, s2, and s3. Thus, when x=0, only processor 2 needs to be active. Processor 1 remains inactive in an idle state waiting for processor 2 to wake it up if necessary. The datapath of processor 1 is not consuming power because the inputs are not changing. The power consumed by both controllers is reduced because of their smaller size. Furthermore, the power consumed by processor 1's controller is reduced even more because it is in an idle state. The overhead in this technique is the communication between the processors and possible duplication of registers.

Figure 1.5. FSMD functional partitioning technique.

In addition to reducing power, FSMD functional partitioning also provides solutions to a variety of synthesis problems. These include I/O satisfaction by reducing total I/O by as much as 67% (which could impact physical design positively), reduced synthesis runtime by as much as 85%, and hardware / software tradeoffs [7]. Furthermore, the technique does not require the modification of synthesis tools because it is applied before synthesis. The relevance of using the FSMD model is that many circuit designs are specified at the register-transfer level using this model. However, partitioning introduces extra power consumption for inter-processor communication between the smaller FSMDs. Thus, the problem that must be solved is one of partitioning such that the reduction in power for computations far outweighs the power increase for communication, while also minimizing the increase in total circuit size and execution time, and preserving the cycle-by-cycle behavior.

#### References

- [1] Srinivas Devadas & Sharad Malik, "A Survey of Optimization Techniques Targeting Low power VLSI Circuits," *Proceedings of the Design Automation Conference*, pp. 242-247, 1995.

- [2] Enrico Macii, Massoud Pedram, & Fabio Somenzi, "High-Level Power Modeling, Estimation, and Optimization," *Proceedings of the Design Automation Conference*, pp. 31-38, 1997.

- [3] Mazhar Alidina, Jose Monteiro, Srinivas Devadas, & Abhijit Ghosh, "Precomputation-Based Sequential Logic Optimization for Low Power," *Proceedings of the International Conference on Computer Design*, pp. 74-81, October 1994.

- [4] Vivek Tiwari, Sharad Malik, & Pranav Ashar, "Guarded Evaluation: Pushing Power Management to Logic Synthesis/Design," *International Symposium on Low Power Design*, 1995.

- [5] L. Benini, P. Vuillod, G. De Micheli & C. Coelho, "Synthesis of Low-Power Selectively-Clocked Systems from High-Level Specification," *International Symposium on System Synthesis*, pp. 57-63, Nov. 1996.

- [6] J. Monteiro & A Oliveira, "Finite State Machine Decomposition For Low Power," *Proceedings of the Design Automation Conference*, pp. 758-763, 1998.

- [7] Frank Vahid, Thuy DmLe, and Yu-Chin Hus, "Functional Partitioning improvements over structural partitioning for packaging constraints and synthesis: tool performance," ACM Transactions on Design Automation of Electronic Systems 3, 2, pp. 181-208, April 1998.

## **Chapter 2.** Previous Work

Power reduction techniques can be applied at every level of design abstraction. In this chapter, we will review previous significant contributions on power reduction at various design abstraction level.

#### 2.1. Transistor Level

Power reduction at the transistor level deals with the physical aspect of the transistor and how they are laid out inside a gate. There are basically two methods for reducing power dissipation at this level: transistor sizing and transistor reordering.

#### 2.1.1. Transistor Sizing

The size of a transistor can have significant impact on the gate delay and the power dissipated by the gate. The larger the transistor size, the shorter the delay, but more power is consumed. Thus, the goal is to find the smallest transistor or gate that will still satisfy the delay constraint. Work in this area includes [1], [2], [3], [4] and [5].

#### 2.1.2. Transistor Reordering

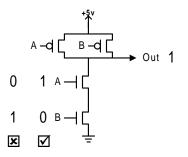

Gates (such as a NAND gate) have input pins that are functionally equivalent. In such a case, inputs can be permuted on these pins without affecting the correctness of the result. However, ordering the gate inputs will affect both the power and the delay of the gate. Consider the transistor implementation of a 2-input NAND gate as shown in Figure 2.1. It was observed that the power consumption for the NAND gate is lower when the inputs to pins A and B are 1 and 0 respectively as opposed to 0 and 1. Thus, an ordering of the inputs using minimal power can be found. Work in this area include [2], [4], [6], [7] and [8]. It was reported in [6] that average power reductions of 12% are achievable using transistor reordering techniques.

#### 2.2. Logic Gate Level

Power reduction at the logic gate level mainly deals with manipulating the logical expression to reduce the number of gates required to implement the expression and to reduce the switching activities. By reducing the number of gates, the overall capacitance in the circuit will also be reduced, thus, the power consumption. Using this technique to reduce power is basically a side effect from reducing the area. Optimization at this level occurs in two phases: technology-independent and technology-dependent optimization.

Figure 2.1. Transistor implementation of a 2-input NAND gate.

#### 2.2.1. Technology-independent

In the technology-independent phase, no knowledge of the actual physical gates is assumed; only logic equations are manipulated to reduce the area, number of gates, delay and power consumption. Optimization techniques in this phase include exploiting the don't-care sets for reducing the switching activities as in [9] and [10]; path balancing by adding buffers to reduce glitches as in [11], [12] and [13]; and factorization of logical expressions presented in [14].

Any gate in a combinational circuit has an associated don't-care set where the input combinations either never occur at the gate inputs or that they produce the same values at the circuit outputs. Since the power dissipation of a gate is dependent on the probability of the gate evaluating to a 1 or a 0, this probability can be changed by utilizing the don't-care sets.

It was observed in [13] that spurious transitions account for 10% to 40% of the switching activity in typical combinational logic circuits. In path balancing, the idea is to add delay buffers in a path in order to reduce the glitching activities of a circuit.

Factorization makes use of the fact that factoring an expression can reduce the number of literals, and therefore, reduce the number of transistors required to implement the expression. For example, the expression  $a \cdot c + a \cdot d + b \cdot c + b \cdot d$  can be factored into  $(a + b) \cdot (c + d)$ , thus, reducing the transistor count considerably.

#### 2.2.2. Technology-dependent

In the technology-dependent phase, logic equations are mapped to the target technology library gates, again optimizing for area, number, delay and power. A typical technology library will contain hundreds of gates with different transistor sizes. The problem is to find suitable gates requiring the least amount of power to satisfy the logic equations produced from the technology-independent phase. Much work has been done in this area in terms of area and delay. Work on extending the original approaches to power dissipation include [3], [15], [16] and [17].

#### 2.3. Register Transfer Level

Register transfer level (RTL) deals with the way data is transferred between registers from one clock cycle to the next. A circuit at the RT level can be broken down into two parts: sequential and combinational. The sequential portion contains the finite state machine (FSM) or controller for the circuit. The combinational or datapath portion contains the functional units, registers and multiplexers for performing the operations. The extent to which hardware is shared and the sequence of variables mapped to each register affect the total switched capacitance in the datapath. Functional units, registers and portions of the controller can be shut off during certain clock cycles to further reduce the power consumption.

#### 2.3.1. Sequential Circuit

For a sequential circuit, the states of a finite state machine can be encoded in such a way that if a state s has a large number of transitions to state t, then the two states should

be given uni-distant codes, so as to minimize the switching activity at the register output. Works in this area include [14], [18], [19] and [20].

Recent work in reducing the power consumption in the sequential circuit uses a partitioning technique on the FSM [21] and [22]. The controller is partitioned into two or more interacting FSMs. Each FSM controls the execution of one section of computation and only one sub-FSM is active at any given clock cycle. Power is saved because the remaining FSMs are idle. This technique was discussed in the introduction.

#### 2.3.2. Combinational Circuit

Switching activity is reduced through appropriate register allocation and binding techniques such as in [23] and [24]. Operand reordering and operand sharing between registers can also reduce switching as in [25] and [26]. The goal of operand reordering is to find an appropriate input operand order for commutative operations in such a way that switching activity is reduced. The operand sharing technique attempts to schedule and bind operations to functional units in such a way that the activity of the input operands is

Figure 2.2. Precomputation example of a comparator.

reduced. Operations sharing the same operand are scheduled in control steps as near as possible. Thus, the potential for a functional unit to reuse the same operand value (and, therefore, to decrease its input activity) is higher. Precomputation logic can be added to the datapath to compute the output values for a subset of input conditions as in [27] and [28]. If the output values can be precomputed, then the switching activity in the original circuit can be reduced. Of course the power savings in the original circuit is offset by the power consumed in the extra logic.

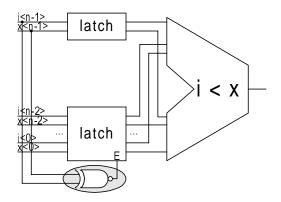

An example taken from [27] is a *n*-bit comparator that computes the function i < x. The optimized circuit with precomputation logic is shown in Figure 2.2. In this example, the precomputation logic is the exclusive NOR gate. The comparison can be precomputed using only the most significant bit of the two inputs *i*<*n*-1> and *x*<*n*-1>. Certainly if *i*<*n*-1> is less than *x*<*n*-1> then *i* < *x*. Thus, if the output can be determined from this precomputation, then the remaining bits need not be compared. By latching the remaining bits when the condition is satisfied, the amount of switching activities in the comparator is reduced and thus, power is saved.

Similar to disabling portions of the controller, unnecessary functional units and registers can also be shut off during certain cycles in the execution. During these times of unnecessary activity, the clock signal to registers can be stopped or the register can be disabled as in [30] and [31]; inputs to functional units can be latched as in [29].

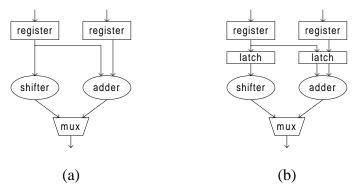

Figure 2.3 shows an example taken from [29] of an ALU containing an adder and a shifter. A multiplexer is used to select the result from either one of the functional units. In

any clock cycle only one of the two functions needs to be computed. However, the multiplexer does the selection after both units have completed their evaluation. The proposed *guarded evaluation* technique to reduce the power from the unnecessary functional unit is to place a transparent latch with an enable at the input to each of the functional units. The input to the functional unit that is not required can be latched and thus unnecessary switching activities can be prevented.

#### 2.4. Behavioral Level

At the behavioral level, power reduction is obtained mainly by reducing the switching activities using circuit transformations or partitioning. Transformations of the circuit are typically aimed at reducing either the number of cycles in a computation or the number of resources used in the computation during high-level synthesis as in [32], [33], [34], [35] and [36]. The basic idea is to reduce the number of control steps so that slower control clock cycles can be used for a fixed throughput, allowing for a reduction in supply voltage. The reduction in control step requirements is most often possible due to the

Figure 2.3. Guarded evaluation technique: (a) unoptimized RTL circuit, and (b) optimized with transparent latches.

exploitation of concurrency. Transformations that affect the amount of concurrency include retiming/pipelining, algebraic transformations, and loop transformations.

Partitioning provides the possibility of disabling mutually exclusive or inactive portions of the circuit when not needed in the execution during a certain time as in [21], [22], [29], [37] and [38]. Except for [38], these techniques are applied only to a small portion of the whole circuit. In [21] and [22], only portions of the finite state machine is disabled, and in [29] and [37] only portions of the datapath is disabled. In [38] both the controller and the datapath are disabled.

Coding techniques for reducing the switching activities on the I/O pins and address busses were presented in [39], [40] and [41]. In [41], different bus interfaces including bus width and coding schemes are compared for low power. More parallelism in a circuit can be introduced to speed it up and then reduces the voltage until it realizes its originally required speed as shown in [42].

#### 2.5. System Level

The main focus for power savings at the system level is from turning off portions of the system that are not being used and thus minimizing the use of power-intensive operations. This includes turning off the monitor and the disk drive [43]; turning off inactive hardware modules [44] and providing optimum supply voltage and/or mixed voltages to the modules [44] and [45]. Communications to and from memory modules can also be minimized as in [46]. Software may be compiled so as to minimize the power dissipation when it is executed on a given hardware platform as shown in [47] and [48].

#### 2.6. Summary

In this chapter, we have reviewed previous significant contributions on power reduction at various design abstraction levels. Recent research in power reduction is focusing more at the higher design abstraction levels.

#### References

- [1] Lin & Hwang, "Power reduction by gate sizing with path-oriented slack calculation," *Proceedings of the 1st Asia-Pacific DAC*, 1995, pp7-12.

- [2] C.H. Tan & J. Allen, "Minimization of Power in VLSI Circuits Using Transistor Sizing, Input Ordering, and Statistical Power Estimation," *Proceedings of the Int'l. Workshop on Low Power Design*, April 1994, pp 75-80.

- [3] Y. Tamiya, Y. Matsunaga, & M. Fujita, "LP based cell selection with constraints of timing, area and power consumption," *Proc. of the IEEE ICCAD*, 1994, pp378-381.

- [4] M. Pedram, "Power estimation and optimization at the logic level," *Int. J. High Speed Electron. Syst.*, June 1994, pp179-202.

- [5] Berkelaar & Jess, "Gate sizing in MOS digital circuits with linear programming," *Proc. of the ACM European DAC*, 1990, pp217-221.

- [6] E. Musoll & J. Cortadella, "Optimizing CMOS Circuits for Low Power using Transistor Reordering," *European Design & Test Conference*, 1996

- [7] Shen, Lin, & Wang, "Transistor reordering rules for power reduction in CMOS gates," *ICCAD*, 1995.

- [8] Prasad & Roy, "Circuit optimization for minimization of power consumption under delay constraint," *Proc. of the 1994 Int. Workshop on Low Power Design*, pp15-20.

- [9] A. Shen, S. Devadas, A. Ghosh, & K. Keutzer, "On Average Power Dissipation and Random Pattern Testability of Combinational Logic Circuits," *Proc. of the Int. Conf. on CAD*, Nov. 1992, pp402-407.

- [10] S. Iman & M. Pedram, "Multi-Level Network Optimization for Low Power," *Proc.* of the Int. Conf. on CAD, Nov. 1994, pp371-377.

- [11] C. Lemonds & S. Shetti, "A Low Power 16 by 16 Multiplier Using Transition Reduction Circuitry," *Proceedings of the Int'l Workshop on Low Power Design*, April 1994, pp 139-142.

- [12] Murgai, Brayton, & Sangiovanni-Vincentelli, "Decomposition of Logic Functions for Minimum Transition Activity," *EDTC*, 1995, pp

- [13] A. Ghosh, S. Devadas, K. Keutzer, and J. White, "Estimation of Average Switching Activity in Combinational and Sequential Circuits," *Proceedings of the Design Automation Conference*, pp. 253-256, June 1992.

- [14] K. Roy & S. Prasad, "SYCLOP: Synthesis of CMOS Logic for Low Power Applications," Proc. Of the Int. Conf. On Comp. Design: VLSI in Computers and Processors, Oct. 1992, pp464-467.

- [15] V. Tiwari, P. Ashar & S. Malik, "Technology Mapping for Low Power," Proc. of the 30th DAC, June 1993, pp74-79.

- [16] C.Y. Tsui, M. Pedram & A. Despain, "Technology Decomposition and Mapping Targeting Low power Dissipation, *Proc. of the 30th DAC*, June 1993, pp68-73.

- [17] B. Lin, "Technology Mapping for Low Power Dissipation," Proc. of the Int. Conf. On Comp. Design: VLSI in Computers and Processors, Oct. 1993.

- [18] S.H. Chow, Y.C. Ho, T.T. Hwang, & C.L. Liu, "Low Power Realization of Finite State Machines – A Decomposition Approach," ACM Trans. on Design Automation of Electronic Systems, July 1996, pp315-340.

- [19] C.Y. Tsui, M. Pedram, C.A. Chen, & A.M. Despain, "Low Power State Assignment Targeting Two- and Multi-level Logic Implementations," *Proc. of the Int. Conf. on CAD*, Nov. 1994, pp82-87.

- [20] G.D. Hachtel, M. Hermida, A. Pardo, M. Poncino, & F. Somenzi, "Re-Encoding Sequential Circuits to Reduce Power Dissipation," *Proc. of the Int. Conf. on CAD*, Nov. 1994, pp70-73.

- [21] L. Benini, P. Vuillod, G. DeMicheli, & Claudionor Coelho, "Synthesis of Low-Power Selectively-Clocked Systems from High-Level Specification," *ISSS*, 1996, p57-63.

- [22] J. Monteiro & A. Oliveira, "Finite State Machine Decomposition for Low Power," Proceedings of the Design Automation Conference, pp. 758-763, 1998.

- [23] Jui-Ming Chang, Massoud Pedram, "Register Allocation and Binding for Low Power", *Proceedings of the Design Automation Conference*, pp. 29-35, 1995.

- [24] E. Musoll & J. Cortadella, "Scheduling and Resource Binding for Low Power," Proceedings of the International Conference on Computer Aided Design, pp104-109, 1995.

- [25] E. Musoll & J. Cortadella, "High-level synthesis techniques for reducing the activity of functional units," *ISLPD*, 1995.

- [26] Kim & Choi, "Power-conscious high level synthesis using loop folding," *DAC*, pp.441-445, 1997.

- [27] M. Alidina, J. Monteiro, S. Devadas, A. Ghosh, & M. Papaefthymiou, "Precomputation-Based Sequential Logic Optimization for Low Power," *IEEE Transactions on VLSI Systems*, pp426-436, December 1994.

- [28] J. Monteiro, J. Rinderknecht, S. Devadas, & A. Ghosh, "Optimization of Combinational and Sequential Logic Circuits for Low Power Using Precomputation," *Proc. of the 1995 Chapel Hill Conf. on Advanced Research on VLSI*, March 1995.

- [29] Vivek Tiwari, Sharad Malik, & Pranav Ashar, "Guarded Evaluation; Pushing Power Management to Logic Synthesis/Design," *International Symposium on Low Power Design*, 1995.

- [30] G. Tellez, A. Farrahi, & M. Sarrafzadeh, "Acitvity-driven clock design for low power circuits," *Proc. of the IEEE Int. Conf. on CAD*, 1995, pp62-65.

- [31] T. Lang, E. Musoll, & J. Cortadella. "Reducing Energy Consumption of Flip-Flops," Universitat Politècnica de Catalunya DAC Technical Report 4, 1996.

- [32] A. Chandrakasan, M. Potkonjak, R. Mehra, J. Rabaey, & R. Brodersen, "Optimizing Power Using Transformations," *IEEE Trans. on CAD of IC and Systems*, Jan. 1995, pp12-31.

- [33] A. Chandrakasan, M. Potkonjak, J. Rabaey, & R. Brodersen, "Hyper-LP: A System for Power Minimization Using Architectural Transformations," *Proceedings of the International Conference on Computer Aided Design*, pp. 300-303, 1992.

- [34] A. Raghunathan, & N. Jha, "Behavioral synthesis for low power," *Proceedings of the International Conference on Computer Aided Design*, Oct. 1994, pp318-322.

- [35] A. Raghunathan, & N. Jha, "ILP formulation for Low Power Based on Minimizing Switched Capacitance during Data Path Allocation," *Proc. of the Int. Sym. on Circuits & Systems*, 1995.

- [36] R. Mehra & J. Rabaey, "Exploiting regularity for low-power design," *ICCAD*, 1996, pp166-172.

- [37] Vaishnav & Pedram, "Delay Optimal Partitioning Targeting Low Power VLSI Circuits," *ICCAD*, 1995, pp638-643.

- [38] Enoch Hwang, Frank Vahid, & Yu-Chin Hsu, "FSMD Functional Partitioning for Low Power," *Proceedings of the Design, Automation and Test in Europe*, pp. 22-28, March 1999.

- [39] Su, Tsui, & Despain, "Low power architecture design and compilation techniques for high-performance processors," *COMPCON 1994 Digest of Technical Papers*, 1994, pp489-498.

- [40] Stan & Burleson, "Limited-weight codes for low power I/O," *Proc. of the 1994 International Workshop on Low-Power Design*, 1994, pp209-214.

- [41] Tony Givargis, & Frank Vahid, "Interface Exploration for Reduced Power in Core-Based Systems, "*International Symposium on System Synthesis*, pp. 117-122, 1998.

- [42] A. Chandrakasan, S. Sheng, & R. Brodersen, "Low-power CMOS design," IEEE J. Solid-State Circuits, 1992, pp472-484.

- [43] Inki Hong & Miodrag Potkonjak, "Power Optimization in Disk-Based Real-Time Application Specific Systems," *ICCAD*, 1996, p634-637.

- [44] Chandrakasan, Sheng & Brodersen, "Low-power techniques for portable real-time DSP applications," *Proc. of VLSI Design*, 1992.

- [45] R. Martin & J. Knight, "Power-profiler: optimizing ASICs power consumption at the behavioral level," *Proc. of the 32nd DAC*, 1995, pp42-47.

- [46] Wuytack, Catthoor, Franssen, Nachtergaele, & DeMan, "Global communication and memory optimizing transformations for low power systems," *Proc. of the 1994 Int. Workshop on LP Design*, 1994, pp203-208.

- [47] V. Tiwari, S. Malik, & A. Wolfe, "Power analysis of embedded software: a first step towards software minimization," *IEEE Trans. VLSI Sys.*, Dec 1994, pp437-445.

- [48] V. Tiwari, S. Malik & A. Wolfe, "Compilation Techniques for Low Energy: an overview," *Proc. of IEEE Symposium on Low Power Electronics*, Oct. 1994, pp38-39.

## **Chapter 3.** Power Consumption

In this chapter, we will look at the various factors affecting power consumption in a circuit, how power is calculated in a circuit, and finally show how partitioning a circuit can reduce power consumption.

#### **3.1.** Power Dissipation

Power consumption of a CMOS circuit is composed of three components [1]: 1) dynamic power consumption due to capacitive charging and discharging when a signal toggles ( $P_d$ ); 2) dynamic power consumption due to short circuit dissipation ( $P_{sc}$ ); and 3) static power consumption due to leakage currents ( $P_s$ ). Thus, the total power consumption P of a CMOS circuit is

$$P = P_d + P_{sc} + P_s \tag{3.1}$$

Every time when the output of a gate switches from a '0' to a '1' or vice versa, the loading capacitors (from the gates that are connected to this output) need to be charged or discharged. This gives the dynamic power term  $P_d$ . Also during this time when the gate switches, there is a moment when there is a path created between the power supply and ground, thus, causing the short circuit dissipation  $P_{sc}$ . During times of inactivity, current

is still being drawn because of parasitic diodes within a gate. This contributes to the static leakage current  $P_s$ . The following sections will look at these three terms in more detail.

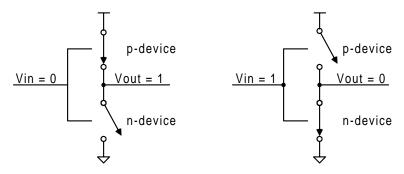

### 3.1.1. Static Power Dissipation

Consider a complementary CMOS gate as shown in Figure 3.1. If the input  $V_{in} = `0, `$  the associated n-device is "OFF" and the p-device is "ON." The output voltage is  $V_{DD}$  or logic '1.' When the input  $V_{in} = `1, `$  the associated n-channel device is biased "ON" and the p-channel device is "OFF." In this case the output voltage is 0 volts ( $V_{SS}$ ). Since one of the transistors is always "OFF" when the gate is in either of these logic states, there is no DC current path from  $V_{DD}$  to  $V_{SS}$ , and the resultant quiescent (steady-state) current, and hence the static power  $P_s$ , is zero.

However, there is some small static dissipation due to reverse bias leakage between diffusion regions and the substrate. A profile of an inverter shown in Figure 3.2 shows how the source-drain diffusions and the n-well diffusion form parasitic diodes with the psubstrate. Since parasitic diodes are reverse-biased, their leakage current contributes to the static power dissipation. The static power dissipation is the product of the device

Figure 3.1. CMOS inverter model for static power dissipation evaluation.

leakage current and the supply voltage. Thus, the total static power dissipation,  $P_s$ , is obtained from

$$P_s = \sum_{1}^{n} leakage \, crrent \times V_{DD} \tag{3.2}$$

where

$$n =$$

number of devices.

A useful estimate is to allow a leakage current of 0.1*nA* to 0.5*nA* per device at room temperature.

## 3.1.2. Dynamic Power Dissipation due to Short-Circuit

When a gate switches from a '0' to a '1' or vice versa, there is a moment when there is a path created between the power supply and ground, thus, causing the short circuit dissipation  $P_{sc}$ . The short-circuit power dissipation is given by

Figure 3.2. Parasitic diodes in a CMOS inverter.

$$P_{sc} = \frac{\beta}{12} (V_{DD} - 2V_t)^3 \frac{t_{rf}}{t_p}$$

(3.3)

where

$\beta$  = gain factor of the transistor which is dependent on both the transistor manufacturing process parameters and the device geometry, and is given by

$$\beta = \frac{\mu \varepsilon}{t_{ox}} \left( \frac{W}{L} \right)$$

where  $\mu$  is the dielectric constant,  $\varepsilon$  is the permittivity of the gate insulator,  $t_{ox}$  is the thickness of the gate insulator, W is the width of the channel, and L is the length of the channel.

$V_t$  = threshold voltage  $\approx 0.7$  v.

$t_{rf}$  = rising and falling time of the input waveform (assuming that they are equal).

$t_p$  = period of the input waveform.

As the load capacitance on the output of the gate is increased, the significance of the short-circuit dissipation is reduced by the capacitive dissipation  $P_d$ .

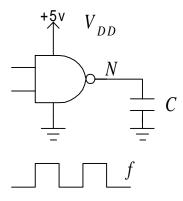

# 3.1.3. Dynamic Power Dissipation due to Capacitive Charging and Discharging

Each time during a signal transition from either '0' to '1' or, alternatively, from '1' to '0', current is required to charge or discharge the output capacitive load. This dynamic dissipation can be modeled by assuming that the rise and fall time of the step input is much less than the repetition clock period  $t_p$ . The average dynamic power  $P_d$  dissipated

during switching for a square-wave input  $V_{in}$ , and having a repetition frequency of  $f_p = 1/t_p$ , is given by

$$P_{d} = \frac{1}{t_{p}} \int_{0}^{t_{p}/2} i_{n}(t) V_{out} dt + \frac{1}{t_{p}} \int_{t_{p}/2}^{t_{p}} i_{p}(t) (V_{DD} - V_{out}) dt$$

(3.4)

where

$i_n$  = n-device transient current.

$i_p$  = p-device transient current.

For a step input and with  $i_n(t) = C_L d_{Vout}/dt$ , and  $i_p(t) = C_L d(V_{DD} - V_{out})/dt$  where  $C_L$  = load capacitance, we get the equation

$$P_{d} = \frac{C_{L}}{t_{p}} \int_{0}^{V_{dd}} V_{out} \, dV_{out} + \frac{C_{L}}{t_{p}} \int_{V_{dd}}^{0} (V_{DD} - V_{out}) \, d(V_{DD} - V_{out})$$

$$= \frac{C_{L} V_{DD}^{2}}{t_{p}}$$

$$= C_{L} V_{DD}^{2} f_{p}$$

(3.5)

In the behavioral context, this translates to

$$P_d = \frac{1}{2} C V_{DD}^2 f N$$

watt (3.6)

where *C* is the total loading capacitance of the gate output,  $V_{DD}$  is the supply voltage, *f* is the clock frequency, and *N* is the transition probability of the gate output. The transition probability or switching frequency is defined as the average number of gate output transitions per clock cycle and is given by

$$N_i = \frac{t_p n_i}{T_{exec}} \tag{3.7}$$

where  $t_p = 1/f$  is the clock period,  $n_i$  is the total number of toggles at net *i*, and  $T_{exec}$  is the total execution time. These values are illustrated in Figure 3.3.

## **3.2.** Power Calculation

To simplify the total power calculation, many of the power calculation tools for complex circuits only consider  $P_d$  as an approximation to the total power because it has been shown that  $P_d$  accounts for over 90% of the total power [2].

Given a digital circuit,  $P_d$  is calculated for all the nets in the circuit and the sum of them is the average power consumption for the entire circuit

Figure 3.3. Variables affecting power consumption.

$$Power = \frac{1}{2t_p} V^2 \sum_{\forall i} C_i N_i \quad \text{watts}$$

$$= \frac{1}{2t_p} V^2 \sum_{\forall i} C_i \frac{t_p n_i}{T_{exec}}$$

$$= \frac{V^2}{2T_{exec}} \sum_{\forall i} C_i n_i$$

(3.8)

where *i* is an individual net in the circuit.

The total energy consumed for the entire circuit is

$$Energy = Power \times T_{exec} \quad \text{watt-second}$$

$$= \frac{V^2}{2T_{exec}} \sum_{\forall i} C_i n_i T_{exec}$$

$$= \frac{V^2}{2} \sum_{\forall i} C_i n_i \quad \text{joules}$$

(3.9)

Hence, to evaluate the energy usage of a circuit, we need to know the number of toggles and the loading capacitance for each net in the circuit, and the voltage used. The number of toggles can be obtained by simulation and counting the number of times the signal switches for each net. The capacitance for each gate can be obtained from the technology library used for the synthesis of the circuit. Knowing the capacitance for each gate, the loading capacitance for each net can be calculated from analyzing the netlist to see how the gates are connected.

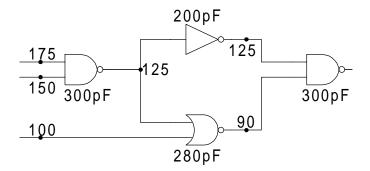

For example, the netlist of Figure 3.4 has four gates and six nets. The nets are annotated with the toggle count and the gates are annotated with the gate capacitance. Assuming that the operating voltage is 5V, the energy consume by this netlist is:

$$Energy = \frac{5V^2}{2} \begin{bmatrix} (175 \times 3 \times 10^{-10} F) + (150 \times 3 \times 10^{-10} F) + (100 \times 2.8 \times 10^{-10} F) \\ + (125 \times (2 \times 10^{-10} F + 2.8 \times 10^{-10} F) + (125 \times 3 \times 10^{-10} F) + (90 \times 3 \times 10^{-10} F) \end{bmatrix}$$

$$= \frac{5V^2}{2} \begin{bmatrix} 525 \times 10^{-10} F + 450 \times 10^{-10} F + 280 \times 10^{-10} F \\ + 600 \times 10^{-10} F + 375 \times 10^{-10} F + 270 \times 10^{-10} F \end{bmatrix}$$

$$= \frac{5V^2}{2} \begin{bmatrix} 2500 toggles \times 10^{-10} F \end{bmatrix}$$

$$= 3.125 \times 10^{-6} J$$

$$= 3.125 \mu J$$

#### **3.3.** Power Reduction

Power reduction for a system can be achieved from all levels of the system design. At the lower levels of the design process, power reduction is obtained mainly through the reduction of the capacitance in the circuit. At the behavioral level, power reduction is obtained mainly from reducing the switching activities within the circuit.

Figure 3.4. Sample netlist with four gates and six nets. The gates are annotated with the gate capacitance and the nets are annotated with the toggle count.

Switching activities in a circuit are reduced primarily by eliminating useless switching activities through proper power management. This can be accomplished either by disabling portions of the system that are not performing useful work, or by partitioning the system into several parts such that the switching activities are localized in only one part at a time. Partitioning is possible if the parts are mutually exclusive in their execution. Thus, only one part needs to be active at any one time while the remaining parts are inactive. This is analogous to deactivating certain devices in the system that is not needed, for example, powering down the disk drive when not in use.

An easy and effective method to disable a part is to prevent any changes to the inputs of the part. This in turn will prevent switching activities within the part. Thus, when the inputs to the circuit do not change, then there will be no switching activities in the entire circuit. For example, if the initial inputs to a NAND gate are all 1's, then the output is a 0. This output will remain at a 0 if the inputs do not change. Since this output is connected to the inputs of other logic gates, all the outputs to the other gates will also remain the same. Thus, there will be switching activities in the circuit only if the inputs

Figure 3.5. Combinational logic with: (a) common inputs, (b) latched inputs, and (c) partitioned inputs.

change in value. Of course the reverse is not always true. For example, for a two input NAND gate, the output is a 1 for inputs  $\{0,0\}$ ,  $\{0,1\}$ , and  $\{1,0\}$ .

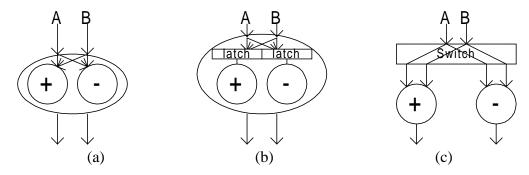

Consider a combinational logic circuit containing two functional units with common inputs as shown in Figure 3.5(a). Assume that the computation requires the evaluation of an addition followed by a subtraction. While performing the addition, the input signals will also propagate to the gates in the subtraction unit. Thus, the subtraction unit is using power even though the result from the subtraction unit is not needed. Similarly when the subtraction is being performed, the addition unit is consuming power but the result from the addition unit is not needed.

There are basically two general methods to reduce the useless switching activities. In the first method, we can insert transparent latches at the inputs of the two functional units as shown in Figure 3.5(b). The latches can prevent the inputs to the functional unit that is not needed for a particular cycle from changing. For this method, the two functional units and the newly added latches are all within the same part. In the second method, we can partition the circuit such that the switching activities are localized in only one part at a time. Thus, we would put the addition unit and the subtraction unit in two different parts so that the input to one will not affect the input to the other as shown in Figure 3.5(c). The switch will control which part gets the input. When the inputs to a part remain constant there will be no switching activities within the entire part thus power is reduced.

As we will see in the following sections, the second method will result in more power reductions than the first method because the first method is only applied to the combinational logic in the datapath, whereas, the second method is applied to the entire processor, namely the datapath *and* the controller. Thus, we want to apply this partitioning idea to the whole processor.

## 3.4. Summary

In this chapter, we have shown how power is consumed and calculated in a CMOS circuit. The idea of partitioning a circuit was also introduced for power reduction.

## References

- [1] Neil H. E. Weste, & Kamran Eshraghian, *Principles of CMOS VLSI Design*, Addison-Wesley Publishing, California, 1993.

- [2] A. Chandrakasan, T. Sheng, & R. Brodersen, "Low Power CMOS Digital Design," *Journal of Solid State Circuits*, Vol. 27, No. 4, pp. 473-484, April 1992.

## Chapter 4. Procedural Functional Partitioning

In this chapter, we will look at procedural functional partitioning and how power is reduced using this technique. In order to understand this, we need to have a general concept of the behavioral synthesis process. We will then show why the traditional method of structural partitioning does not reduce power and then show how functional partitioning is different and thus can reduce power.

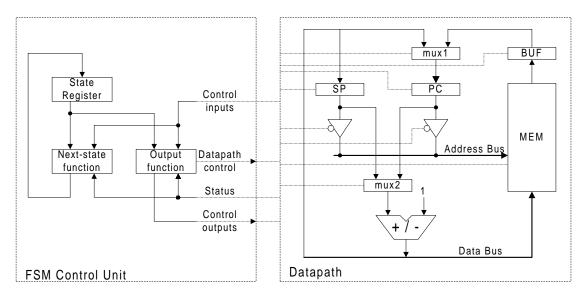

## 4.1. Behavioral Synthesis

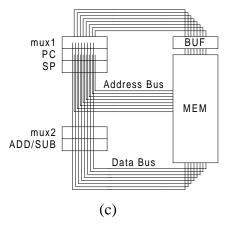

Synthesis is the process of transforming and optimizing a digital circuit design from a high level of abstraction to a lower level of abstraction. In behavioral synthesis, the input is a behavioral description of the design specified in a Hardware Description Language (HDL) such as VHDL or Verilog. The synthesis process translates the behavioral description first into a structural description and finally to a physical gate level circuit netlist as shown in Figure 4.1. Figure 4.1(a) shows a behavioral description of a sample segment of code. Figure 4.1(b) shows the corresponding structural description with the separate FSM control unit and the datapath. Figure 4.1(c) shows the physical layout. The

```

if IR(3) = '0' then

PC := PC + 1;

else

BUF := MEM(PC);

MEM(SP) := PC + 1;

SP := SP - 1;

PC := BUF;

end if;

```

Figure 4.1. Example of the three levels of abstraction: (a) behavioral, (b) structural, and (c) physical.

major steps in the synthesis process include scheduling, allocation, and finally the generation of the gate level circuit netlist.

The internal data representation of a behavioral description is usually a control data flow graph (CDFG), which captures all the control and data-flow dependencies of the given behavioral description. Scheduling algorithms then partition this CDFG into subgraphs so that each subgraph is executed in one control step. Each control step corresponds to one state of the controlling finite state machine. Within a control step, a separate functional unit is required to execute each operation assigned to that step. Thus, the total number of functional units required in a control step directly corresponds to the number of operations scheduled in it. If more operations are scheduled into each control step, more functional units are necessary, which results in fewer control steps for the design implementation.

Allocation consists of two tasks: unit selection and unit binding. Unit selection determines the number and types of components to be used in the design. These components can be either functional units, storage elements, or interconnect wires. Unit binding maps the variables and operations in the scheduled CDFG to the selected components. For every operation in the CDFG, we need a functional unit that is capable of executing the operation. For every variable that is used across several control steps in the scheduled CDFG, we need a storage unit to hold the data values during the lifetime of the variable. Finally, for every data transfer in the CDFG, we need a set of interconnection units to effect the transfer.

When a circuit is synthesized from a behavioral description to a gate level netlist, only one FSM control unit and one datapath is generated as shown in Figure 4.1(b). The control unit consists of the state register, logic for generating the next state, and logic for generating control signals to control the operation of the datapath. The datapath consists of the data registers, functional units, multiplexers, and connecting wires for executing the operations of the specified behavioral instructions. At each cycle or time step, control signals from the control unit is sent to the datapath to perform the operations scheduled for that cycle. The state register is then updated by the next-state function in the control unit and the cycle repeats.

## 4.2. Structural Partitioning

Partitioning a design has been used as a solution to many circuit packaging problems.

Figure 4.2. Partitioning: (a) structurally, (b) functionally.

Traditionally, partitioning a circuit is performed at the structural level. In structural partitioning (also known as circuit or netlist partitioning), as shown in Figure 4.2(a), a circuit is first synthesized from the behavioral level to the structural or gate level netlist. The partitioning is then performed at the gate level.

From a power reduction perspective, structural partitioning does not reduce switching activity. The reason is that behavioral synthesis, as mentioned in the previous section, generates only one control unit and one datapath from the design specification. Even though partitioning the netlist creates more than one physical partition, there is still logically only one processor consisting of one datapath and one control unit. When a primary input signal changes, the entire datapath may be affected regardless of which partition they are in. Moreover, all the gates in the control unit must also be active in order to provide the correct control signals to the datapath. Thus, even though, we have more than one part, the switching activities are not localized within a part. This results in much unnecessary switching activities and so power is not reduced.

Consider an unpartitioned processor containing two procedures, *Procedure1* and *Procedure2*, with common primary inputs as shown in Figure 4.3(a). Suppose we want to evaluate *Procedure1* followed by *Procedure2* sequentially. While performing *Procedure1*, the input signals will also propagate to the gates in *Procedure2* because they are all interconnected. A hypothetical switching activities for the gates of the control unit and datapath for both *Procedure1* and *Procedure2* are shown in Figure 4.3(b). Thus, power is being used by *Procedure2* although the result from it is not needed. In fact, the

amount of power used by *Procedure2* is the same regardless of whether the result is needed or not. Similarly when *Procedure2* is being performed, *Procedure1* is consuming power but the result from it is not needed.

If we take a hypothetical situation where both procedures require  $1\mu W$  of power and  $1\mu$ sec to execute, then for both procedures to execute sequentially, a total of  $2\mu W$  of

Figure 4.3. Netlist with control unit and datapath, hypothetical switching activity, and power usage of processor with two procedures: (a) single large processor with two procedures; (b) switching activity of large processor; (c) power usage of large processor; (d) structural partitioning of processor; (e) switching activity of (d); (f) power usage of (d); (g) functional partitioning of processor; (h) switching activity of (g); (i) power usage of (g).

power is required for 2 $\mu$ sec resulting in a total of 4 $\mu$ J of energy being consumed by the single large processor as illustrated in Figure 4.3(c).

Figure 4.3(d) shows the result of structural partitioning the large processor of Figure 4.3(a). Here, the single datapath and control unit netlist is divided into two parts resulting in gates from both *Procedure1* and *Procedure2* to be spread across the two parts. As a result, even if we need the result from only one procedure, there will still be switching activities from both parts. Thus, the switching activities and energy consumption are decreased only slightly from the single large processor as shown in Figure 4.3(e) and Figure 4.3(f).

### 4.3. Procedural Functional Partitioning

In procedural functional partitioning, the focus is on partitioning coarse-grained functions and procedures [1]. The behavioral process is first partitioned into several smaller mutually exclusive parts. Each of these smaller parts is then synthesized to its own custom processor, having its own controller and datapath as shown in Figure 4.2(b). From a power reduction perspective, functional partitioning can significantly reduce switching activity. The main reason is that partitioning occurs *before* synthesis, hence each part is a processor containing its own control unit and datapath. Each processor is now smaller than the original large processor implementing the entire process, and only one processor is executing a computation at any given time. Thus, at a given time, switching activity is limited to only one small processor; the other processors will be idle. A processor is made idle by preventing its primary inputs from changing as discussed in

Section 3.3. When a processor is idle, we have, in effect shut down both the controller and the datapath for that processor. Thus, power reduction is possible through functional partitioning because it reduces the overall switching activities of the entire system by localizing the activities within smaller processors, hence, power consumed per operation is less.

In our hypothetical example, we would first partition *Procedure1* and *Procedure2*. Synthesis is then applied to the two parts individually resulting in two separate processors having there own control units and datapaths as shown in Figure 4.3(g). Being two separate processors, the inputs to one will now have no effect to the inputs of the other. With two smaller mutually exclusive processors, the total amount of switching activities at any one time is reduced by about half as shown in Figure 4.3(h). However, partitioning introduces new switching activities for inter-processor communication. It is only during inter-processor communication that both processors will have switching activities at the same time. Thus, in our hypothetical example, each processor might now consume  $1.25\mu$ W of power, resulting in a total energy of 2.5\muJ as shown in Figure 4.3(i).

#### 4.4. Procedural Functional Partitioning Example

We performed an experiment to compare the switching activities between an unpartitioned and a partitioned system. The example shown is for a factorization problem. Given the pseudo-code shown in Figure 4.4, we can partition it into three parts as shown in Figure 4.5. The program calls three separate procedures, *mod*, *divide*, and

```

input x;

\operatorname{count} := 2;

while ((count * count) <= x) loop

mod(x,count,mod_result);

divide(x,count,divide_result);

is_prime(count,prime_result1);

is_prime(divide_result,prime_result2);

if (mod\_result = 0) and (prime\_result1 = 1) and

(prime_result2 = 1) then

answer1 <= divide_result;

answer2 <= count;

exit;

else

count := count + 1;

end if;

end loop;

```

Figure 4.4. Sample unpartitioned pseudo-code.