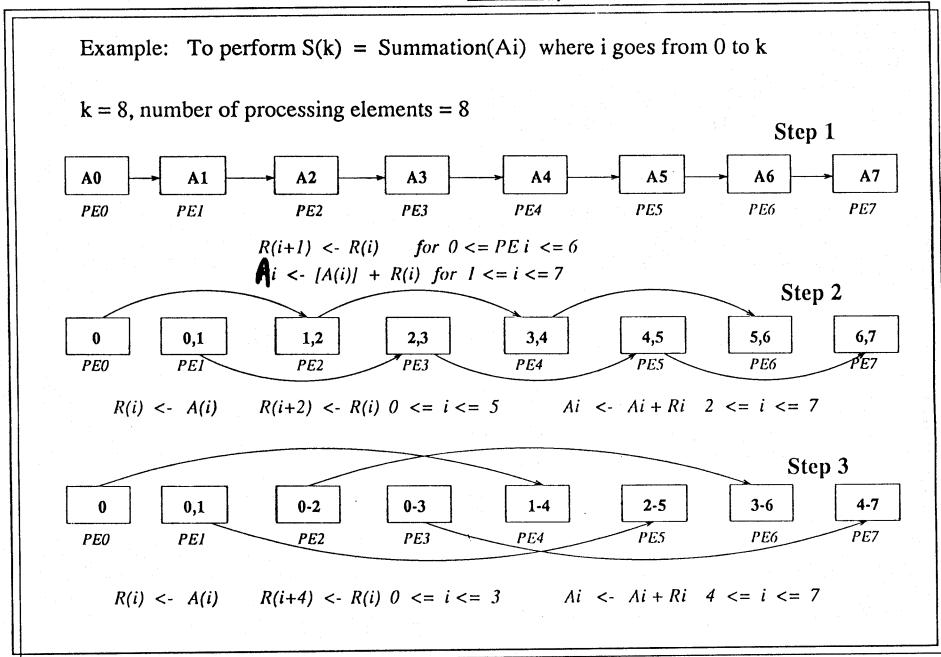

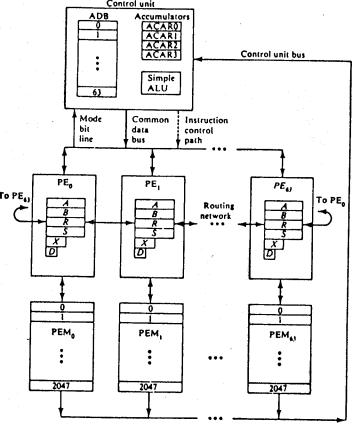

### How does an SIMD computer work?

- A Host computer is necessary to do the I/O operations.

- The user program is loaded into the control memory.

- The data is distributed to all the memory modules.

- The control unit decodes the instn and executes it if it is a scalar instn. If it is a vector instn, it broadcasts the control signals to the PEs to do the executions.

- Before broadcasting the control signals, the CU broadcasts an enable vector which will enable the PE's.

### Masking and Data Routing Mechanisms

A,B,C -- working registers

$Si = status (1 \ active, 0 \ inactive)$

Ri -- Data routing register

Di -- holds address

Ii -- Index register

**Texas A&M University**

**Texas A&M University**

# Matrix Multiplication

#### Example 5.3: An $O(n^3)$ algorithm for SISD matrix multiplication

For

$$i = 1$$

to  $n$  Do

For  $j = 1$  to  $n$  Do

$c_{ij} = 0$  (initialization)

For  $k = 1$  to  $n$  Do

$c_{ij} = c_{ij} + a_{ik} \cdot b_{kj}$  (scalar additive multiply)

End of  $k$  loop

End of  $j$  loop

End of  $i$  loop

Note:

$$c_{ij} = \sum_{k=1}^{n} a_{ik} \cdot b_{kj}$$

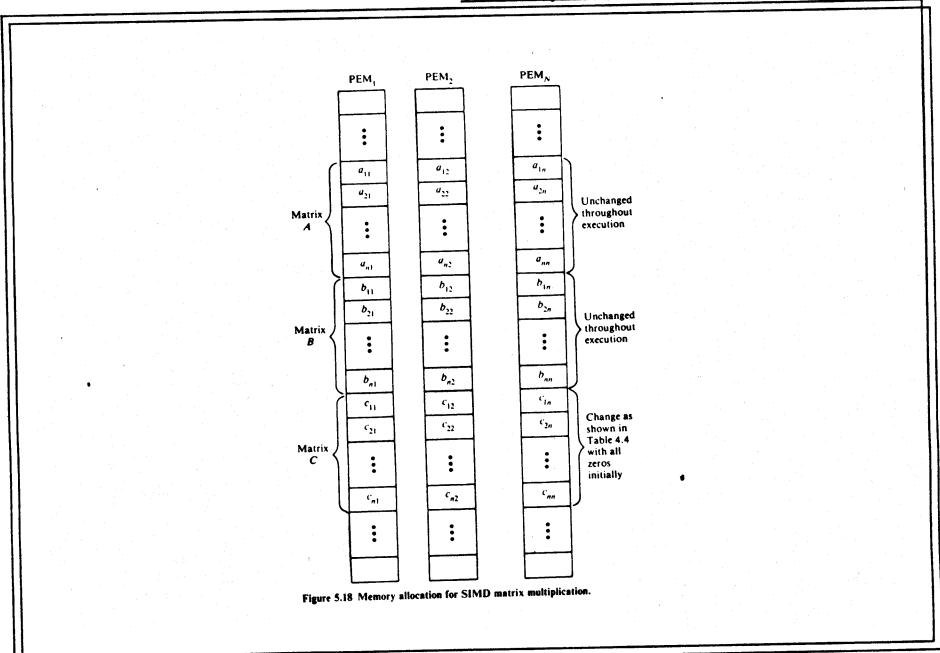

#### Example 5.4: An $O(n^2)$ algorithm for SIMD matrix multiplication

For

$$\ell = 1$$

to  $n$  Do

Par for  $k = 1$  to  $n$  Do

$c_{ik} = 0$  (vector load)

For  $j = 1$  to  $n$  Do

Broadcast  $a_{ij}$

Par for  $k = 1$  to  $n$  Do

$c_{ik} = c_{ik} + a_{ij} \cdot b_{jk}$  (vector multiply)

End of  $j$  loop

End of  $j$  loop

### The Computer Science Department

Table 5.4 Successive contents of the C array in memory

| Outer<br>loop<br>i | Inner<br>loop<br>j | Parallel SIMD operations on $k = 1, 2,, n$                                                                                                                     |                                                                                                                                                                |                                                                                                                                                                |

|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                    | $c_{i1} \leftarrow c_{i1} + a_{ij} \times b_{j1}$                                                                                                              | $c_{i2} \leftarrow c_{i2} + a_{ij} \times b_{j2} \cdots$                                                                                                       | $c_{in} \leftarrow c_{in} + a_{ij} \times b_{jn}$                                                                                                              |

| l                  | 1 2                |                                                                                                                                                                | $c_{12} \leftarrow c_{12} + a_{11} \times b_{12} c_{12} \leftarrow c_{12} + a_{12} \times b_{22}$                                                              | $c_{1n} \leftarrow c_{1n} + a_{11} \times b_{1n} c_{1n} \leftarrow c_{2n} + a_{12} \times b_{2n}$                                                              |

|                    | n :                | <b>:</b>                                                                                                                                                       | $\vdots \qquad \vdots \qquad$                  | $\vdots$ $c_{1n} \leftarrow c_{1n} + a_{1n} \times b_{nn}$                                                                                                     |

| 2                  | 1<br>2<br>:        | $c_{21} \leftarrow c_{21} + a_{22} \times b_{21}$ $\vdots$                                                                                                     | $c_{22} \leftarrow c_{22} + a_{21} \times b_{12}$ $c_{22} \leftarrow c_{22} + a_{22} \times b_{22}$ $\vdots$ $c_{22} \leftarrow c_{22} + a_{2n} \times b_{n2}$ | $c_{2n} \leftarrow c_{2n} + a_{21} \times b_{1n} c_{2n} \leftarrow c_{2n} + a_{22} \times b_{2n} \vdots c_{2n} \leftarrow c_{2n} + a_{2n} \times b_{2n}$       |

| :                  | :                  | :                                                                                                                                                              | :                                                                                                                                                              | :                                                                                                                                                              |

| n                  | 1<br>2<br>:        | $c_{n1} \leftarrow c_{n1} + a_{n1} \times b_{11}$ $c_{n1} \leftarrow c_{n1} + a_{n2} \times b_{21}$ $\vdots$ $c_{nn} \leftarrow c_{nn} + a_{nn} \times b_{n1}$ | $c_{n2} \leftarrow c_{n2} + a_{n1} \times b_{12}$ $c_{n2} \leftarrow c_{n2} + a_{n2} \times b_{22}$ $\vdots$ $c_{n2} \leftarrow c_{n2} + a_{nn} \times b_{n2}$ | $c_{nn} \leftarrow c_{nn} + a_{n1} \times b_{1n}$ $c_{nn} \leftarrow c_{nn} + a_{n2} \times b_{2n}$ $\vdots$ $c_{nn} \leftarrow c_{nn} + a_{nn} \times b_{nn}$ |

| Local memory       |                    | PEM <sub>1</sub>                                                                                                                                               | PEM <sub>2</sub>                                                                                                                                               | PEM,                                                                                                                                                           |

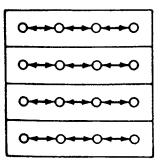

#### nxn Mesh

Phase 1

Phase 2

Figure 1.3.27 An O(n) algorithm for multiplying two  $n \times n$  matrices A and B with elements  $a_{ij}$  and  $b_{ij}$ , respectively, on an  $n \times n$  mesh. Initially, processor (i, j) of the mesh holds elements  $a_{ij}$  and  $b_{ij}$ , and at the end of the algorithm, processor (i, j) will hold the ijth element  $\sum_{m=1}^{n} a_{im}b_{mj}$  of the product AB.

The algorithm consists of three phases, each requiring O(n) time. In the first phase, each processor (i, j) broadcasts  $a_{ij}$  to the processors in the ith row;

these are n multinode broadcasts, one within each row, requiring O(n) time. In the second phase, each processor (i,j) broadcasts  $b_{ij}$  to the processors in the jth column; these are n multinode broadcasts, one within each column, requiring O(n) time. At the end of two phases, each processor (i,j) holds the values  $a_{im}$  and  $b_{mj}$  for  $m=1,2,\ldots,n$ , and can form the ijth element  $\sum_{m=1}^{n} a_{im}b_{mj}$  of the product AB in time O(n) (which is the third phase). Note that phases 1 and 2 can be done in parallel, assuming that simultaneous communication along all incident links is possible. Also, by appropriately interleaving additions, multiplications, and communications, the algorithm can be made more economical in terms of time and storage.

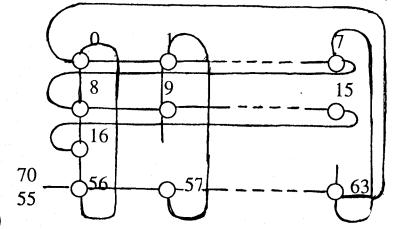

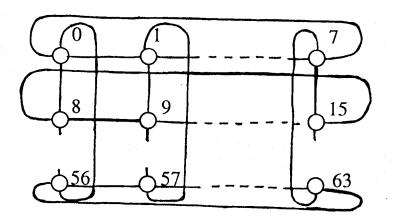

# The Illiac IV Architecture

• Distributed memory architecture

• 64 PEs connected as an 8X8 2-D mesh with end around

connection.

Figure 6.4 A 64-PE liliac IV array. (Courtesy of IEEE Proc. Bouknight et al., April 1972.)

LDB: Local Data Buffer

PEM<sub>i</sub>: 2K X 64 bits memory

64, 64-bits each

## The Illiac IV Network

PEi is connected to PE it, PE i-7, PE i+8, and PE i-8 mod 64. (End

around connection)

2-D Torus (wrap around)

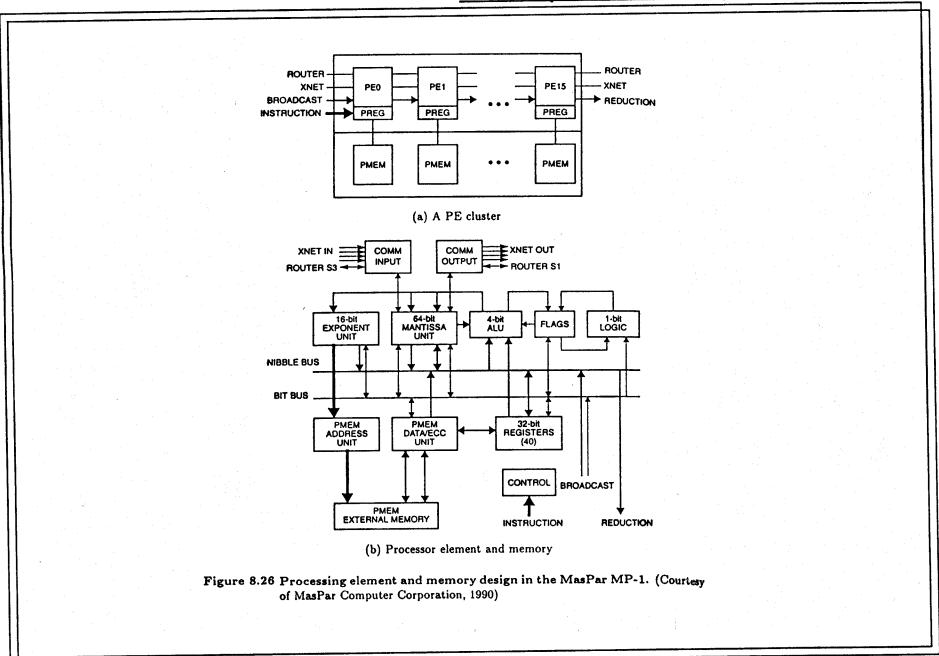

### Maspar MP-1 Architecture

- Configuration with 1K-16K PE's are available

- Each PE has a 4-bit ALU, 1-bit logic unit, a 64-bit mantissa unit, a 16-bit exponent unit, communication input and output ports.

- Each PE has 40 32-bit registers available to the programmer.

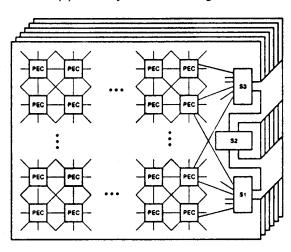

- Each processor board has 1024 PE's arranged as 64 PE clusters (PEC's) with 16 PE's per cluster.

- Each PEC is a chip connected to 8 neighbors via an octagonal mesh.

- Another network, called Multistage Crossbar Network, with three router stages gives a function of 1024X1024 crossbar for routing from any PEC to another PEC.

#### The Computer Science Department

#### The Computer Science Department

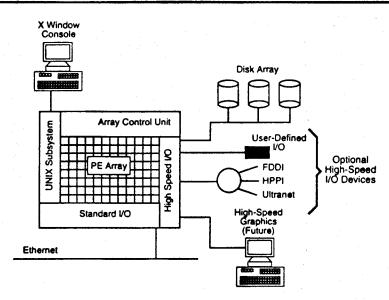

(a) MP-1 System Block Diagram

(b) Array of PE clusters

Figure 8.25 The MasPar MP-1 architecture. (Courtesy of MasPar Computer Corporation, 1990)