# P1394a Draft Standard for a High Performance Serial Bus (Supplement)

Sponsor

Microprocessor and Microcomputer Standards Committee of the IEEE Computer Society

Not yet Approved by

**IEEE Standards Board**

Not yet Approved by American National Standards Institute

**Abstract:** Supplemental information for a high-speed serial bus that integrates well with most IEEE standard 32-bit and 64-bit parallel buses is specified. It is intended to extend the usefulness of a low-cost interconnect between external peripherals, IEEE Std 1394-1995. This standard follows the ISO/IEC 13213:1994 Command and Status Register (CSR) architecture.

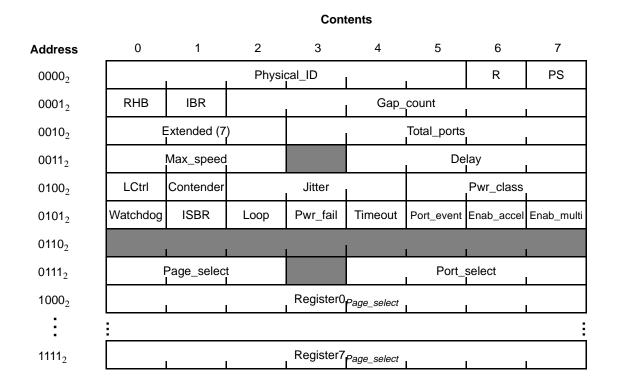

Keywords: bus, computers, high-speed serial bus, interconnect

ISBN x-xxxxx-xxx-x

The Institute of Electrical And Electronics Engineers, Inc. 345 East 47th Street, New York, NY 10017-2394, USA

Copyright © 1997 – 1999 by the Institute of Electrical And Electronics Engineers, Inc. All rights reserved. Published 1999. Printed in the United States of America.

This is an unapproved IEEE Standards Draft, subject to change. Permission is hereby granted for IEEE Standards Committee participants to reproduce this document for purposes of IEEE standardization activities, including balloting and coordination. If this document is to be submitted to ISO or IEC, notification shall be given to the IEEE Copyright Administrator. Permission is also granted for member bodies and technical committees of ISO and IEC to reproduce this document for purposes of developing a national position. Other entities seeking permission to reproduce this document for these or other uses must contact the IEEE Standards Department for the appropriate license. Use of the information contained in this unapproved draft is at your own risk.

**IEEE Standards** documents are developed within the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members of the committees serve voluntarily and without compensation. They are not necessarily members of the Institute. The standards developed within IEEE represent a consensus of the broad expertise on the subject within the Institute as well as those activities outside of IEEE that have expressed an interest in participating in the development of the standard.

Use of an IEEE Standard is wholly voluntary. The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a document is more than five years old and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of all concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 USA

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying all patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

Authorization to photocopy portions of any individual standard for internal or personal use is granted by the Institute of Electrical and Electronics Engineers, Inc., provided that the appropriate fee is paid to Copyright Clearance Center. To arrange for payment of licensing fee, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; (508) 750-8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

# Introduction

(This introduction is not part of the draft standard, IEEE P1394a, Standard for a High Performance Serial Bus (Supplement).)

Standards development is an ongoing process and is, perhaps, never complete. In 1994, the working group responsible for IEEE Std 1394-1995, Standard for a High Performance Serial Bus, reluctantly elected to close the door to new material. Although many enhancements were well understood in principle (some were even making their way into contemporary silicon designs), significant work remained to document the details. Consensus emerged to publish the completed work and later to prepare a supplement. This document is that supplement: it extends and corrects facilities of Serial Bus.

In January, 1996, an informal study group was convened by Dr. Gerald Marazas, Chair of the IEEE P1394 working group. The meeting was held in Dallas, TX, at the same time as a quarterly meeting of the nascent 1394 Trade Association. The topic was unfinished business in Serial Bus; brainstorming quickly identified six major areas of interest. Some of the areas readily resolved into clusters of related activity which became other Serial Bus standards projects still active at the time of writing: IEEE P1394.1, Serial Bus to Serial Bus bridges and IEEE P1394b, gigabit extensions (including new media) to Serial Bus. The topics that were deemed essentially complete (*e.g.*, the alternate 4-pin cable and connector, the PHY arbitration enhancements and miscellaneous corrections to the 1995 standard) were gathered together under the banner of P1394a. Immediately next month, the IEEE P1394a study group met to select a Chair and draft a Project Authorization Request (PAR). The first official meeting of P1394a took place in October, 1996; the working group continued to meet monthly until its last meeting in February, 1998.

The working group organized the new effort as a "supplement" rather than a new Serial Bus standard intended to replace IEEE Std 1394-1995, Standard for a High Performance Serial Bus, in its entirety. This decision was based upon the belief that the changes in P1394a were localized to a few areas and that we would be able to complete our work rapidly if we did not have to reissue the entire standard. In retrospect this was an awkward choice. The reader who wishes to be informed of the current Serial Bus standard is forced to consult both the original standard and this supplement. The working group hopes that in the process of international standardization that it is possible to editorially combine the two documents into a single volume.

P1394a Draft 2.0 failed the sponsor ballot conducted by the IEEE and generated a large number of comments. In an effort to resolve these comments and pave the way for a successful recirculation ballot, the Ballot Response Committee (BRC) was convened by the P1394a Chair, Peter Johansson. It first met in the fall of 1998 and continued meeting into 1999 to complete this revision of the draft standard, which is to be resubmitted to the ballot pool for approval.

## Patent notice

Note: Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying all patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

The patent holder has, however, filed a statement of assurance that it will grant a license under these rights without compensation or under reasonable rates and nondiscriminatory, reasonable terms and conditions to all applicants desiring to obtain such a license. The IEEE makes no representation as to the reasonableness of rates and/or terms and conditions of the license agreement offered by the patent holder. Contact information may be obtained from the IEEE Standards Department.

## **Committee membership**

The following is a list of voting members of the IEEE P1394a working group at the time of publication.

#### Peter Johansson, Chair and Editor Prashant Kanhere, Secretary

Richard Baker Steven Bard Max Bassler Joe Bennett Vilas Bhade Brad Bickford Charles Brill Mike Brown David Brunker Richard Churchill Dan Colegrove Claude Cruz Bill Duckwall Firooz Farhoomand Steve Finch Bill Frank John Fuller Eric Hannah Yasumasa Hasegawa Jerry Hauck John Hill Jack Hollins David Johnson Tom Jones Marcus Kellerman Al Kelley

Mark Knecht David LaFollette Steven Larky Thang Le Robert Liu Hirokazu Mamezaki Takashi Matsui Keiji Miura Bill Northey Farrell Ostler James Piccione Bill Prouty David Scott John Smolka John Ta Ju-ching Tang Motoyasu Tsunoda Renard Ulrey Sushant Verman Colin Whitby-Strevens Paul Wiener David Wooten Roy Yasoshima Phil Young Michael Zarreii Peng Zhang

The following is a list of other major participants in the IEEE P1394a working group (those that attended at least 3 working group meetings since its inception).

| Kazuyuki Abe<br>Eric Anderson<br>Oleg Awsienko<br>Jim Busse<br>Ed Butler | Lou Fasano<br>Taka Fujimori<br>James Gay<br>Sreekanth Godey<br>John Grant | Farrukh Latif<br>Paul S. Levy<br>Cyrus Momeni<br>Neil Morrow<br>Ganesh Murthy | James Skidmore<br>Michael Sorna<br>Peter Teng<br>C. Brendan Traw<br>Tom Trodden |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Carissa Cheung                                                           | Shinichi Hatae                                                            | Karl Nakamura                                                                 | Kent Waterson                                                                   |

| Alistair Coles                                                           | Keith Heilmann                                                            | Takayuki Nyu                                                                  | Lee Wilson                                                                      |

| David Doman                                                              | Burke Henehan                                                             | Kugao Ouchi                                                                   | Calto Wong                                                                      |

| Jim Doyle                                                                | Joe Herbst                                                                | Bill Russell                                                                  | Takao Yasuda                                                                    |

| Sagar Edara                                                              | David Instone                                                             | Bradley Saunders                                                              | Patrick Yu                                                                      |

| Mike Eneboe                                                              | Diana Klashman                                                            | Hisato Shima                                                                  |                                                                                 |

The following people served on the ballot response committee:

| Steven Bard       | John Fuller       | Peter Johansson      | Peter Teng            |

|-------------------|-------------------|----------------------|-----------------------|

| Max Bassler       | Larry Getzin      | Hirokazu Mamezaki    | Tom Trodden           |

| Sagar Edara       | Yasumasa Hasegawa | David Scott          | Renard Ulrey          |

| Firooz Farhoomand | Jerry Hauck       | Michael Shinkarovsky | Colin Whitby-Strevens |

| Lou Fasano        | David James       | James Skidmore       | David Wooten          |

The following persons were members of the balloting group:

Names to be supplied by the IEEE upon publication as a standard

# Contents

| 1. Overview                 |                                                          |     |

|-----------------------------|----------------------------------------------------------|-----|

| 1.1 Scope                   |                                                          |     |

|                             |                                                          |     |

|                             | nization                                                 |     |

|                             |                                                          |     |

|                             | tion                                                     |     |

| 1.5 Document notat          |                                                          | 2   |

| 2. References               |                                                          | 9   |

| 3. Definitions              |                                                          | 11  |

| 3.1 Conformance gl          | lossary                                                  |     |

| 3.2 Technical gloss         | ary                                                      | 11  |

| 4. New features (informativ | ve)                                                      | 17  |

| 4.1 Connection deb          | ounce                                                    | 17  |

| 4.2 Cable arbitratio        | n enhancements                                           |     |

| 4.3 Performance op          | timization via PHY "pinging"                             | 20  |

|                             | ion                                                      |     |

| •                           | spend and resume                                         |     |

| 5. Alternative cable media  | attachment specification                                 | 25  |

| 5.1 Connectors              |                                                          | 25  |

| 5.2 Cables                  |                                                          |     |

|                             | cable assembly performance criteria                      |     |

|                             | tion performance criteria                                |     |

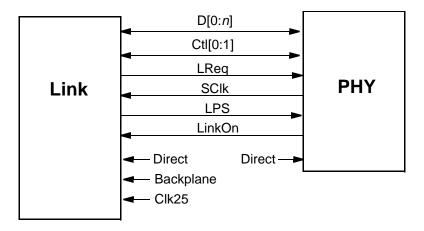

| 6. PHY/Link interface spec  | cification                                               | 43  |

| 6 1 Initialization an       | nd reset                                                 | 45  |

|                             | errupt indications                                       |     |

|                             |                                                          |     |

| 1                           |                                                          |     |

|                             |                                                          |     |

|                             |                                                          |     |

|                             |                                                          |     |

|                             | cteristics (cable environment)                           |     |

| 7. PHY register map         |                                                          | 69  |

| 7 1 PHV register m          | ap (cable environment)                                   | 69  |

|                             | ap (backplane environment)                               |     |

| e                           | and PHY                                                  |     |

|                             |                                                          |     |

| 8. Cable physical layer per | formance enhancement specifications                      |     |

| 1 00                        |                                                          |     |

|                             |                                                          |     |

| -                           | d ground                                                 |     |

| 8.4 Data signal rise        | and fall times                                           |     |

| © 1997 – 1999 IEEE          | This is an unapproved standards draft, subject to change | vii |

|       | <ul><li>8.5 Cable PHY packets</li><li>8.6 Cable PHY line states</li></ul>   |  |

|-------|-----------------------------------------------------------------------------|--|

|       |                                                                             |  |

|       | 8.7 Cable interface timing constants                                        |  |

|       | 8.8 Gap timing                                                              |  |

|       | 8.9 Node variables                                                          |  |

|       | 8.10 Port variables                                                         |  |

|       | 8.11 Cable physical layer operation                                         |  |

| 9. As | synchronous streams                                                         |  |

|       | 9.1 Asynchronous stream packet format                                       |  |

|       | 9.2 Global asynchronous stream packet (GASP) format                         |  |

|       | 9.3 Loose vs. strict isochronous packet reception                           |  |

| 10. C | Clarifications and corrigenda                                               |  |

|       | 10.1 Link event indication (LK_EVENT.indication)                            |  |

|       | 10.2 Malformed packets                                                      |  |

|       | 10.3 Cycle start.                                                           |  |

|       | 10.4 Read response for data block                                           |  |

|       | 10.5 Maximum isochronous data payload                                       |  |

|       | 10.6 Transaction codes (tcode)                                              |  |

|       | 10.7 Response codes (rcode)                                                 |  |

|       | 10.8 Tag (isochronous stream packets)                                       |  |

|       | 10.9 Acknowledge codes (ack_code)                                           |  |

|       | 10.10 Priority arbitration for PHY packets and response packets             |  |

|       | 10.11 Transaction layer services                                            |  |

|       | 10.12 Retry protocols                                                       |  |

|       | 10.13 CSR Architecture transactions mapped to Serial Bus                    |  |

|       | 10.14 Serial Bus control request (SB_CONTROL.request)                       |  |

|       | 10.15 Serial Bus event indication (SB_EVENT.indication)                     |  |

|       | 10.16 Node capabilities taxonomy                                            |  |

|       | 10.17 NODE_IDS register                                                     |  |

|       | 10.18 SPLIT_TIMEOUT register                                                |  |

|       | 10.19 Command reset effects                                                 |  |

|       | 10.20 PRIORITY_BUDGET register                                              |  |

|       | 10.21 CHANNELS_AVAILABLE register                                           |  |

|       | 10.22 BROADCAST_CHANNEL register                                            |  |

|       | 10.23 Unit registers                                                        |  |

|       | 10.24 SPEED_MAP registers                                                   |  |

|       | 10.25 Configuration ROM Bus_Info_Block                                      |  |

|       | 10.26 Node_Unique_ID                                                        |  |

|       | 10.27 Determination of the root (cable environment)                         |  |

|       | 10.28 Determination of the isochronous resource manager (cable environment) |  |

|       | 10.29 Determination of the bus manager (cable environment)                  |  |

|       | 10.30 Isochronous resource allocation                                       |  |

|       | 10.31 Gap count optimization                                                |  |

|       | 10.32 Automatic activation of the cycle master                              |  |

|       | 10.33 Abdication by the bus manager                                         |  |

|       | 10.34 Internal device physical interface                                    |  |

|       | 10.35 Transaction integrity safeguards                                      |  |

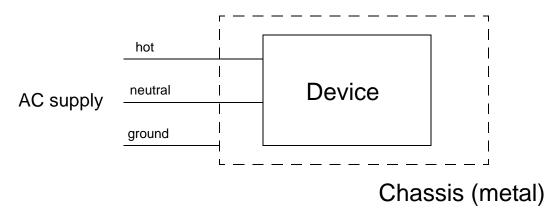

| Anne  | ex A Cable environment electrical isolation                                 |  |

|       | A.1 Grounding characteristics of AC powered devices                         |  |

This is an unapproved standards draft, subject to change © 1997 – 1999 IEEE

| A.2 Electrical isolation<br>A.3 Agency requirements        |     |

|------------------------------------------------------------|-----|

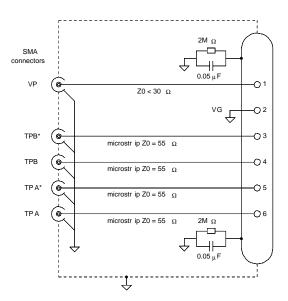

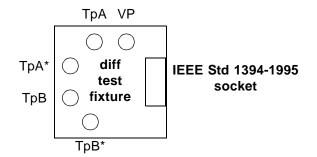

| Annex B Serial Bus cable assembly test procedures          |     |

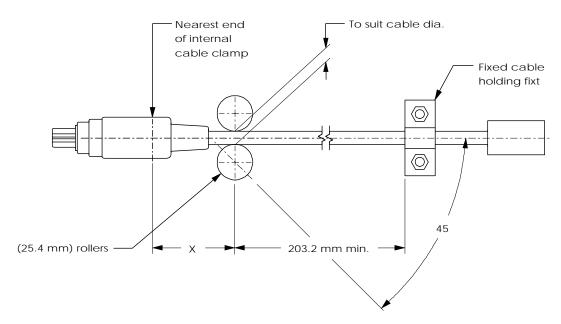

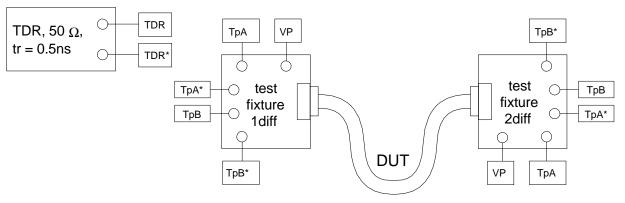

| B.1 Differential test fixture                              | 175 |

| B.2 Signal pairs characteristic and discrete impedance     |     |

| B.3 DC resistance test procedure                           |     |

| B.4 Crosstalk                                              | 179 |

| Annex C Serial Bus topology management (cable environment) |     |

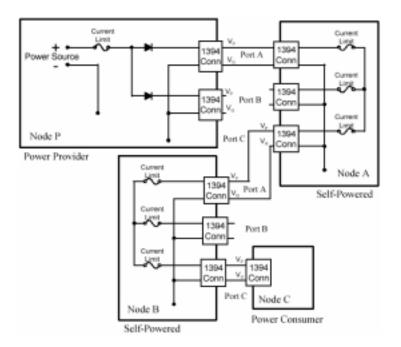

| C.1 Power distribution                                     |     |

| C.2 Performance optimization                               |     |

# P1394a Draft Standard for a High Performance Serial Bus (Supplement)

## 1. Overview

## 1.1 Scope

This is a full-use standard whose scope is to provide a supplement to IEEE Std 1394-1995 that defines or clarifies features and mechanisms that facilitate management of Serial Bus resources, at reconfiguration or during normal operation, and that defines alternate cables and connectors that may be needed for specialized applications.

The following are included in this supplement:

- a) Cables and connectors for a 4-pin variant (from the 6-pin already standardized);

- b) Standardization of the PHY/link interface, previously published as an informative annex to IEEE Std 1394-1995;

- c) Performance enhancements to the PHY layer that are interoperable with the existing standard, *e.g.*, a method to shorten the arbitration delay when the last observed Serial Bus activity is an acknowledge packet;

- d) A redefinition of the isochronous data packet, transaction code  $A_{16}$ , to permit its use in either the asynchronous or isochronous periods;

- e) More stringent requirements on the power to be supplied by a cable power source and a clarification of electrical isolation requirements; and

- f) Significant *corrigenda* and clarifications to the existing standard that do not clearly fall within any of the topics described above.

The preceding are arranged in no particular order.

## 1.2 Purpose

Experience with Serial Bus has revealed some areas in which additional features or improvements may result in better performance or usability. This supplement to IEEE Std 1394-1995 reflects their consideration by a variety of users and their refinement into generally useful facilities or features.

## **1.3 Document organization**

This standard contains this overview, a list of definitions, an informative summary description, sections of technical specification and application annexes. The new reader should read the informative summary and the sections that precede it before the remainder of the document.

# 1.4 Service model

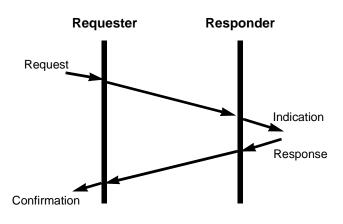

IEEE Std 1394-1995 and this supplement both use a protocol model with multiple layers. Each layer provides services to the next higher layer and to Serial Bus management. These services are abstractions of a possible implementation; an actual implementation may be significantly different and still meet all the requirements. The method by which these services are communicated between the layers is not defined by this standard. Four types of service are defined by this standard:

- a) Request service. A request service is a communication from a layer to a lower or adjacent layer to request some action. A request may also communicate parameters that may or may not be associated with an action. A request may or may not be confirmed. A data transfer request usually triggers a corresponding indication on peer node(s). (Since broadcast addressing is supported on the Serial Bus, it is possible for the request to trigger a corresponding indication on multiple nodes.)

- b) *Indication service*. An indication service is a communication from a layer to a higher or adjacent layer to indicate a change of state or other event detected by the originating layer. An indication may also communicate parameters that are associated with the change of state or event. Indications are not necessarily triggered by requests; an indication may or may not be responded to by a response. A data transfer indication is originally caused by a corresponding request on a peer node.

- c) *Response service*. A response service is a communication from a layer to a lower or adjacent layer in response to an indication; a response is always associated with an indication. A response may communicate parameters that indicate its type. A data transfer response usually triggers a corresponding confirmation on a peer node.

- d) *Confirmation service*. A confirmation service is a communication from a layer to a higher or adjacent layer to confirm a request service; a confirmation is always associated with a request. A confirmation may communicate parameters that indicate the completion status of the request or that indicate other status. For data transfer requests, the confirmation may be caused by a corresponding response on a peer node.

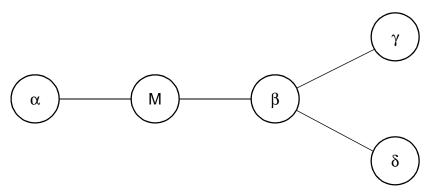

If all four service types exist, they are related as shown by figure 1-1.

Figure 1-1—Service model

# 1.5 Document notation

## 1.5.1 Mechanical notation

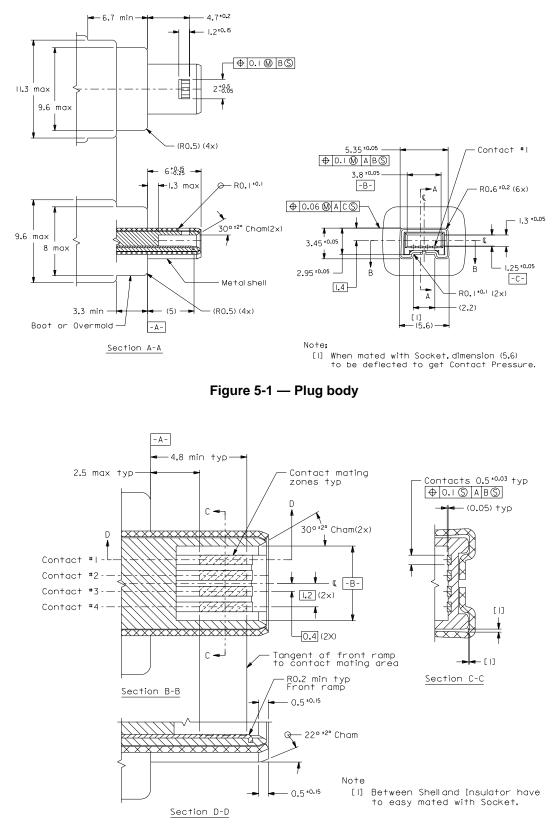

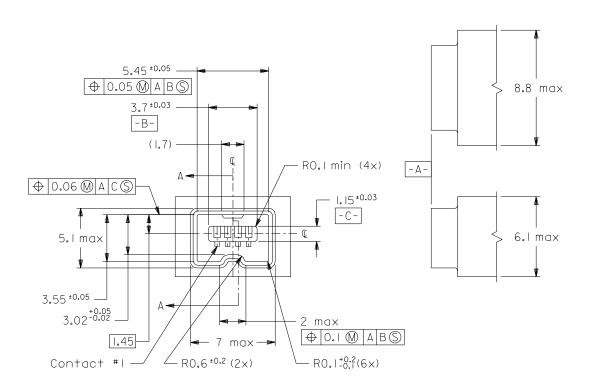

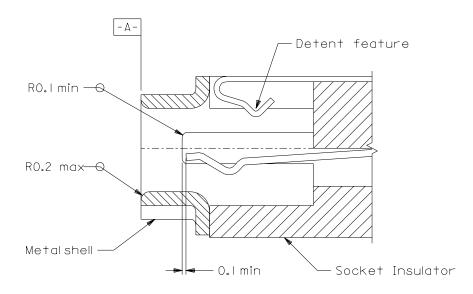

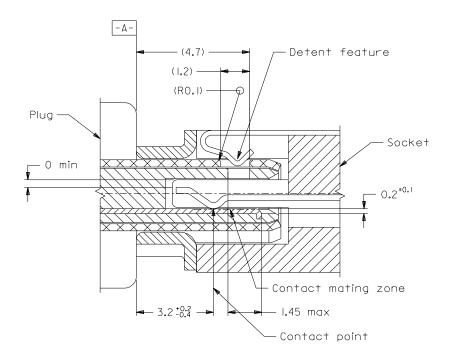

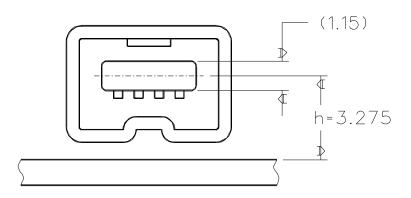

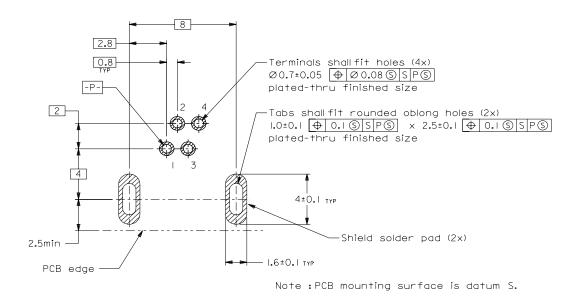

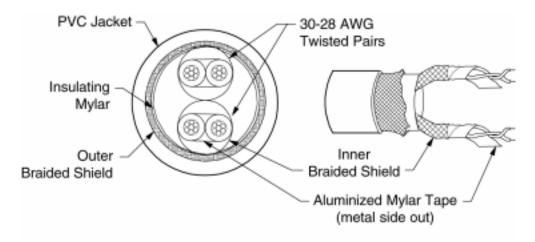

All mechanical drawings in this document use millimeters as the standard unit and follow ANSI Y14.2 and ANSI Y14.5-1982 formats.

# 1.5.2 Signal naming

All electrical signals are shown in all uppercase characters and active-low signals have the suffix "\*". For example: TPA and TPA\* are the normal and inverted signals in a differential pair.

# 1.5.3 Size notation

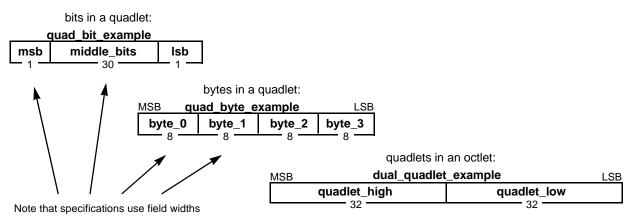

The Serial Bus description avoids the terms word, half-word and double-word, which have widely different definitions depending on the word size of the processor. In their place, the Serial Bus description uses terms established in previous IEEE bus standards, which are independent of the processor. These terms are illustrated in table 1-1.

| Size (in bits) | 16-bit word notation | 32-bit word notation | IEEE standard notation<br>(used in this standard) |

|----------------|----------------------|----------------------|---------------------------------------------------|

| 4              | nibble               | nibble               | nibble                                            |

| 8              | byte                 | byte                 | byte                                              |

| 16             | word                 | half-word            | doublet                                           |

| 32             | long-word            | word                 | quadlet                                           |

| 64             | quad-word            | double               | octlet                                            |

| Table 1-1—Size no | otation examples |

|-------------------|------------------|

|-------------------|------------------|

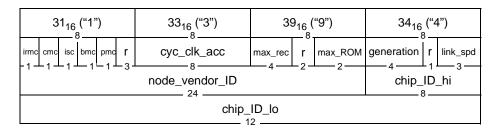

The Serial Bus uses big-endian ordering for byte addresses within a quadlet and quadlet addresses within an octlet. For 32-bit quadlet registers, byte 0 is always the most significant byte of the register. For a 64-bit quadlet-register pair, the first quadlet is always the most significant. The field on the left (most significant) is transmitted first; within a field the most significant (leftmost) bit is also transmitted first. This ordering convention is illustrated in figure 1-2.

Figure 1-2—Bit and byte ordering

Although Serial Bus addresses are defined to be big-endian, their data values may also be processed by little-endian processors. To minimize the confusion between conflicting notations, the location and size of bit fields are usually specified by width, rather than their absolute positions, as is also illustrated in figure 1-2.

When specific bit fields must be used, the CSR Architecture convention of consistent big-endian numbering is used. Hence, the most significant bit of a quadlet ("msb" in figure 1-2) will be labeled "quad\_bit\_example[0]," the most significant byte of a quadlet ("byte\_0") will be labeled "quad\_byte\_example[0:7]," and the most significant quadlet in an octlet ("quadlet\_high") will be labeled "dual\_quadlet\_example[0:31]."

The most significant bit shall be transmitted first for all fields and values defined by this standard, including the data values read or written to control and status registers (CSRs).

# 1.5.4 Numerical values

Decimal, hexadecimal and binary numbers are used within this document. For clarity, the decimal numbers are generally used to represent counts, hexadecimal numbers are used to represent addresses and binary numbers are used to describe bit patterns within binary fields.

Decimal numbers are represented in their standard 0, 1, 2,... format. Hexadecimal numbers are represented by a string of one or more hexadecimal (0-9, A-F) digits followed by the subscript 16. Binary numbers are represented by a string of one or more binary (0,1) digits, followed by the subscript 2. Thus the decimal number "26" may also be represented as " $1A_{16}$ " or " $11010_2$ ". In C code examples, hexadecimal numbers have a "0x" prefix and binary numbers have a "0b" prefix, so the decimal number "26" would be represented by "0x1A" or "0b11010."

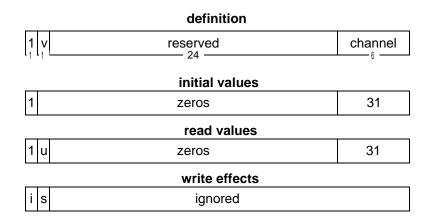

## 1.5.5 Packet formats

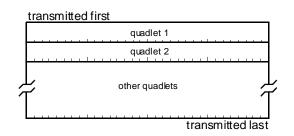

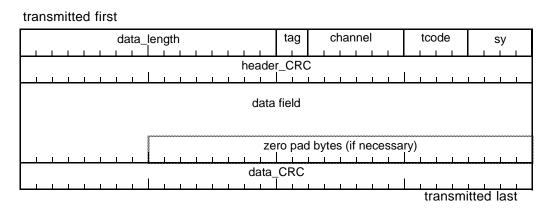

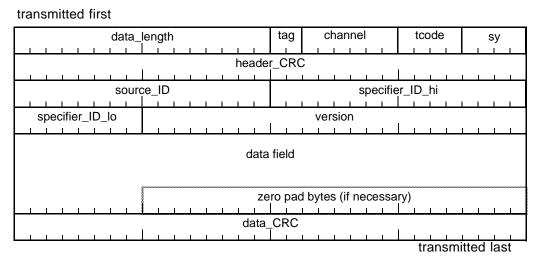

Most Serial Bus packets consist of a sequence of quadlets. Packet formats are shown using the style given in figure 1-3.

Figure 1-3—Example packet format

Fields appear in packet formats with their correct position and widths. Field widths are also stated explicitly in field descriptions. Bits in a packet are transmitted starting with the upper leftmost bit and finishing with the bottom rightmost bit. Given the rules in 1.6.3, this means that all fields defined in this standard are sent most significant bit first.

# 1.5.6 Register formats

All Serial Bus registers are documented in the style used by the CSR Architecture.

# 1.5.7 C code notation

The conditions and actions of the state machines are formally defined by C code. Although familiar to software engineers, C code operators are not necessarily obvious to all readers. The meanings of C code operators, arithmetic, relational logical and bitwise, both unary and binary, are summarized in table 1-2.

| Operator        | Description                                                                                              |  |

|-----------------|----------------------------------------------------------------------------------------------------------|--|

| +, -, * and /   | Arithmetic operators for addition, subtraction, multiplication and integer division                      |  |

| %               | Modulus; x % y produces the remainder when x is divided by y                                             |  |

| >, >=, < and <= | Relational operators for greater than, greater than or equal, less than and less than or equal           |  |

| == and !=       | Relational operators for equal and not equal; the assignment operator, =, should not be confused with == |  |

Table 1-2—C code operators summary

| Operator | Description                                                                                                                                                 |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ++       | Increment; i++ increments the value of the operand after it is used in the expression while ++i incre-<br>ments it before it is used in the expression      |

|          | Decrement; post-decrement, i, and pre-decrement,i, are permitted.                                                                                           |

| &&       | Logical AND                                                                                                                                                 |

|          | Logical OR                                                                                                                                                  |

| !        | Unary negation; converts a nonzero operand into 0 and a zero operand into 1                                                                                 |

| &        | Bitwise AND                                                                                                                                                 |

|          | Bitwise inclusive OR                                                                                                                                        |

| ٨        | Bitwise exclusive OR                                                                                                                                        |

| <<       | Left shift; x << 2 shifts the value of x left by two bit positions and fills the vacated positions with zero                                                |

| >>       | Right shift; vacated bit positions are filled with zero or one according to the data type of the operand but in this supplement are always filled with zero |

| ~        | One's complement (unary)                                                                                                                                    |

#### Table 1-2—C code operators summary (Continued)

A common construction in C is conditional evaluation, in the form (expr)? expr1 : expr2. This indicates that if the logical expression expr evaluates to nonzero value then expr1 is evaluated, otherwise expr2 is evaluated. For example, x = (q > 5)? x + 1: 14; first evaluates q > 5. If TRUE, x is incremented otherwise x is assigned the value 14.

The descriptions above are casual; if in doubt, the reader is encouraged to consult ISO/IEC 9899:1990.

The C code examples assume the data types listed in table 1-3 are defined.

#### Table 1-3—Additional C data types

| Data type | Description                                                                        |  |

|-----------|------------------------------------------------------------------------------------|--|

| timer     | A real number, in units of seconds, that autonomously increments at a defined rate |  |

| Boolean   | A single bit, where 0 encodes FALSE and 1 encodes TRUE                             |  |

All C code is to be interpreted as if it could be executed instantaneously, but time may elapse when conditional expressions are evaluated as part of iterated C code. Time elapses unconditionally only when the following function is called:

void wait\_time(float time);// Wait for time, in seconds, to elapse

### 1.5.8 State machine notation

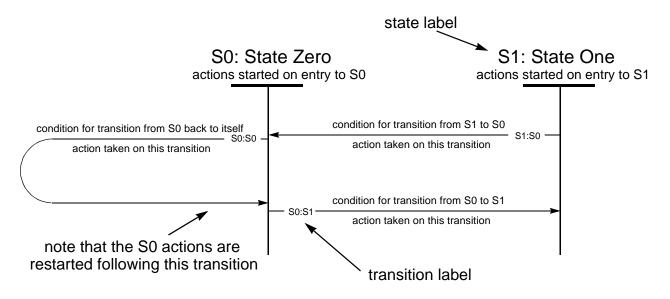

All state machines in this standard use the style shown in figure 1-4.

Figure 1-4—State machine example

These state machines make three assumptions:

- Time elapses only within discrete states;

- State transitions are logically instantaneous, so the only actions taken during a transition are setting flags and variables and sending signals. These actions complete before the next state is entered; and

- Every time a state is entered, the actions of that state are started. Note that this means that a transition that points back to the same state will repeat the actions from the beginning. All the actions started upon entry complete before any tests are made to exit the state.

#### 1.5.9 CSR, ROM and field notation

This standard describes CSRs and fields within them. To distinguish register and field names from node states or descriptive text, the register name is always capitalized. For example, the notation STATE\_CLEAR.*lost* is used to describe the *lost* bit within the STATE\_CLEAR register.

All CSRs are quadlets and are quadlet aligned. The address of a register is specified as the byte offset from the beginning of the initial register space and is always a multiple of four. When a range of register addresses is described, the ending address is the address of the last register.

This document describes a number of configuration ROM entries and fields within these entries. To distinguish ROM entry and field names from node states or descriptive text, the first character of the entry name is always capitalized. Thus, the notation Bus\_Info\_Block.cmc is used to describe the cmc bit within the Bus\_Info\_Block entry.

Entries within temporary data structures, such as packets, timers and counters, are shown in lowercase (following normal C language conventions) and are formatted in a fixed-space typeface. Examples are arb\_timer and connected[i].

NOTE—Within the C code, the character formatting is not used, but the capitalization rules are followed.

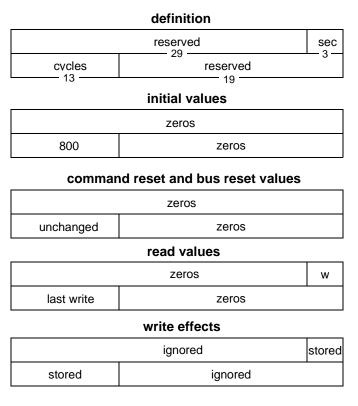

# 1.5.10 Register specification format

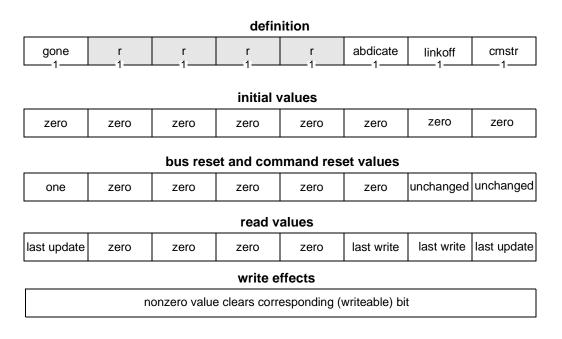

This document defines the format and function of Serial Bus-specific CSRs. Registers may be read only, write only or both readable and writable. The same distinctions may apply to any field within a register. A CSR specification includes the format (the sizes and names of bit field locations), the initial value of the register, the value returned when the register is read and the effect(s) when the register is written. An example register is illustrated in figure 1-5.

| definition         |                        |          |           |          |          |

|--------------------|------------------------|----------|-----------|----------|----------|

| unit_depend<br>12- | vendor dependent<br>16 | sig<br>1 | resv<br>1 | why<br>1 | not<br>1 |

|                    | initial value          |          |           |          |          |

| unit_depend        | zeros                  | 1        | 0         | 0        | 0        |

| read value         |                        |          |           |          |          |

| last write         | last update            | w        | 0         | u        | u        |

| write effect       |                        |          |           |          |          |

| stored             | ignored                | s        | i         | i        | е        |

#### Figure 1-5—CSR format specification (example)

The register definition lists the names of register fields. These names are descriptive, but the fields are defined in the text; their function should not be inferred solely from their names. However, the register definition fields in figure 1-5 have the meanings specified by table 1-4.

#### Table 1-4—Register definition fields

| Name             | Abbreviation  | Definition                                                                                                                                                            |

|------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| unit dependent   | unit_depend   | The meaning of this field shall be defined by the unit architecture(s) of the node.                                                                                   |

| vendor dependent | vendor_depend | The meaning of this field shall be defined by the vendor of the node.<br>Within a unit architecture, the unit-dependent fields may be defined to be vendor dependent. |

A node's CSRs shall be initialized when power is restored (power reset) and may be initialized when a bus reset occurs or a quadlet is written to the node's RESET\_START register (command reset). If a CSR's bus reset or command reset values differ from its initial values, they shall be explicitly specified.

The read value fields in figure 1-5 have the meanings specified by table 1-5.

#### Table 1-5—Read value fields

| Name        | Abbreviation | Definition                                                                                               |

|-------------|--------------|----------------------------------------------------------------------------------------------------------|

| last write  | W            | The value of the data field shall be the value that was previously written to the same register address. |

| last update | u            | The value of the data field shall be the last value that was updated by node hardware.                   |

The write-effect fields in figure 1-5 have the meanings specified by table 1-6.

Table 1-6—Write value fields

| Name    | Abbreviation | Definition                                                                                                                                           |

|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| stored  | S            | The value of the written data field shall be immediately visible to reads of the same register.                                                      |

| ignored | i            | The value of the written data field shall be ignored; it shall have no effect on the state of the node.                                              |

| effect  | e            | The value of the written data field shall have an effect on the state of the node, but may not be immediately visible to reads of the same register. |

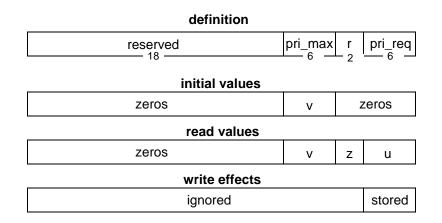

## 1.5.11 Reserved CSR fields

Reserved fields within a CSR conform to the requirements of the conformance glossary in this standard (see clause 3.1). Within a CSR, such a field that is labeled *reserved* (sometimes abbreviated as lowercase r or *resv*). Reserved fields behave as specified by figure 1-6: they shall be zero and any attempt to write to them shall be ignored.

| definition     |

|----------------|

| reserved<br>   |

| initial values |

| zeros          |

| read values    |

| zeros          |

| write effects  |

| ignored        |

|                |

#### Figure 1-6—Reserved CSR field behavior

This is straight-forward as it applies to read and write requests. The same rules apply to lock requests, but the behaviors are less obvious; see clause 10.11.5 for details.

# 2. References

This standard shall be used in conjunction with the following publications. When the following publications are superseded by an approved revision, the revision shall apply.

ANSI/EIA-364-B-90, Electrical Connector Test Procedures Including Environmental Classifications.<sup>1</sup>

IEC 61883-1:1998, Consumer Audio/Video Equipment - Digital Interface (Part 1: General)

IEEE Std 1394-1995, Standard for a High Performance Serial Bus

ISO/IEC 9899: 1990, Programming languages-C.<sup>2</sup>

ISO/IEC 13213: 1994 [ANSI/IEEE Std 1212, 1994 Edition], Information technology—Microprocessor systems—Control and Status Registers (CSR) Architecture for microcomputer buses.

This standard shall also be used in conjunction with the following publications under development. When approved as a standard, the approved version shall apply.

IEEE P1394b, Draft Standard for a High Performance Serial Bus (Supplement)

<sup>&</sup>lt;sup>1</sup> ANSI publications are availabale from Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036-8002, USA.

<sup>&</sup>lt;sup>2</sup> ISO/IEC publications are available from the ISO Central Secretariat, Case Postale 56, 1 rue de Varembé, CH-1211, Genève 20, Switzerland/Suisse. ISO publications are also available in the United States from the American National Standards Institute.

# 3. Definitions

# 3.1 Conformance glossary

Several keywords are used to differentiate between different levels of requirements and optionality, as defined below. This clause replaces existing clause 2.1 of IEEE Std 1394-1995, "Conformance glossary," in its entirety; the following definitions shall apply to both IEEE Std 1394-1995 and this supplement.

**3.1.1 expected:** A keyword used to describe the behavior of the hardware or software in the design models assumed by this standard. Other hardware and software design models may also be implemented.

**3.1.2 ignored:** A keyword that describes bits, bytes, quadlets, octlets or fields whose values are not checked by the recipient.

**3.1.3 may:** A keyword that indicates flexibility of choice with no implied preference.

**3.1.4 reserved:** A keyword used to describe objects—bits, bytes, quadlets, octlets and fields—or the code values assigned to these objects; the object or the code value is set aside for future standardization by the IEEE. A reserved object shall be zeroed by its originator or, upon development of a future IEEE standard, set to a value specified by such a standard. The recipient of a reserved object shall not check its value. The recipient of an object whose code values are defined by this standard shall check its value and reject reserved code values.

**3.1.5 shall:** A keyword indicating a mandatory requirement. Designers are required to implement all such mandatory requirements to ensure interoperability with other products conforming to this standard.

**3.1.6 should:** A keyword indicating flexibility of choice with a strongly preferred alternative. Equivalent to the phrase "is recommended."

# 3.2 Technical glossary

The following are terms that are used within this standard:

3.2.1 acknowledge: An acknowledge packet.

**3.2.2 acknowledge packet:** An 8-bit packet that may be transmitted in response to the receipt of a primary packet. The most and least significant nibbles are the one's complement of each other.

**3.2.3 acronym:** A contrived reduction of nomenclature yielding mnemonics (ACRONYM).

**3.2.4 active port:** A connected, enabled port that observes bias and is capable of detecting all Serial Bus signal states and participating in the reset, tree identify, self-identify and normal arbitration phases.

**3.2.5 arbitration:** The process by which nodes compete for control of the bus. Upon completion of arbitration, the winning node is able to transmit a packet or initiate a short bus reset.

**3.2.6 arbitration reset gap:** The minimum period of idle bus (longer than a normal subaction gap) that separates fairness intervals.

**3.2.7 arbitration signalling:** A protocol for the exchange of bidirectional, unclocked signals between nodes during arbitration.

**3.2.8 asynchronous packet:** A primary packet transmitted in accordance with asynchronous arbitration rules (outside of the isochronous period).

**3.2.9 base rate:** The lowest data rate used by Serial Bus in a backplane or cable environment. In multiple speed environments, all nodes are able to receive and transmit at the base rate. The base rate for the cable environment is 98.304 MHz  $\pm$  100 ppm.

3.2.10 boundary node: A node with two or more ports, at least one of which is active and another suspended.

**3.2.11 bus manager:** The node that provides power management, sets the gap count in the cable environment and publishes the topology of the bus and the maximum speed for data transmission between any two nodes on the bus. The bus manager node may also be the isochronous resource manager node.

**3.2.12 byte:** Eight bits of data.

**3.2.13 cable PHY:** Abbreviation for the cable physical layer.

**3.2.14 channel:** A relationship between a group of nodes, talkers and listeners. The group is identified by a number between zero and 63. Channel numbers are allocated cooperatively through isochronous resource management facilities.

**3.2.15 concatenated transaction:** A split transaction comprised of concatenated subactions.

3.2.16 connected PHY: A peer cable PHY at the other end of a particular physical connection from the local PHY.

**3.2.17 CSR Architecture:** ISO/IEC 13213:1994 [ANSI/IEEE Std 1212, 1994 Edition], Information technology—Micro-processor systems—Control and Status Registers (CSR) Architecture for microcomputer buses.

**3.2.18 cycle master:** The node that generates the periodic cycle start packet 8000 times a second.

**3.2.19 cycle start packet:** A primary packet sent by the cycle master that indicates the start of an isochronous period.

**3.2.20 disabled port:** A port configured to neither transmit, receive or repeat Serial Bus signals. A disabled port shall be reported as disconnected in a PHY's self-ID packet(s).

**3.2.21 disconnected port:** A port whose connection detect circuitry detects no peer PHY at the other end of a cable. It is not important whether the peer PHY is powered or the peer port is enabled.

**3.2.22 doublet**: Two bytes, or 16 bits, of data.

**3.2.23 fairness interval:** A time period delimited by arbitration reset gaps. Within a fairness interval, the total number of asynchronous packets that may be transmitted by a node is limited. Each node's limit may be explicitly established by the bus manager or it may be implicit.

3.2.24 gap: A period of idle bus.

**3.2.25 initial node space:** The 256 terabytes of Serial Bus address space that is available to each node. Addresses within initial node space are 48 bits and are based at zero. The initial node space includes initial memory space, private space, initial register space and initial units space. See either ISO/IEC 13213:1994 or IEEE Std 1394-1995 for more information on address spaces.

**3.2.26 initial register space:** A two kilobyte portion of initial node space with a base address of FFFF F000  $0000_{16}$ . This address space is reserved for resources accessible immediately after a bus reset. Core registers defined by ISO/IEC 13213:1994 are located within initial register space as are Serial Bus-dependent registers defined by IEEE Std 1394-1995.

**3.2.27 initial units space:** A portion of initial node space with a base address of FFFF F000  $0800_{16}$ . This places initial units space adjacent to and above initial register space. The CSR's and other facilities defined by unit architectures are expected to lie within this space.

**3.2.28 isochronous:** Uniform in time (*i.e.*, having equal duration) and recurring at regular intervals.

**3.2.29 isochronous period:** A period that begins after a cycle start packet is sent and ends when a subaction gap is detected. During an isochronous period, only isochronous subactions may occur. An isochronous period begins, on average, every  $125 \,\mu s$ .

3.2.30 isochronous gap: For an isochronous subaction, the period of idle bus that precedes arbitration.

**3.2.31 isochronous resource manager:** A node that implements the BUS\_MANAGER\_ID, BANDWIDTH\_AVAILABLE, CHANNELS\_AVAILABLE and BROADCAST\_CHANNEL registers (some of which permit the cooperative allocation of isochronous resources). Subsequent to each bus reset, one isochronous resource manager is selected from all nodes capable of this function.

**3.2.32 isochronous subaction:** Within the isochronous period, either a concatenated packet or a packet and the gap that preceded it.

**3.2.33 isolated node:** A node without active ports; the node's ports may be disabled, disconnected or suspended in any combination.

**3.2.34 kilobyte:** A quantity of data equal to  $2^{10}$ , or 1024, bytes.

**3.2.35 link layer:** The Serial Bus protocol layer that provides confirmed and unconfirmed transmission or reception of primary packets.

**3.2.36 listener:** An application at a node that receives a stream packet.

**3.2.37 nibble:** Four bits of data.

**3.2.38 node:** A Serial Bus device that may be addressed independently of other nodes. A minimal node consists of only a PHY without an enabled link. If the link and other layers are present and enabled they are considered part of the node.

**3.2.39 node ID:** A 16-bit number that uniquely differentiates a node from all other nodes within a group of interconnected buses. The 10 most significant bits of node ID are the same for all nodes on the same bus; this is the bus ID. The six least-significant bits of node ID are unique for each node on the same bus; this is called the physical ID. The physical ID is assigned as a consequence of bus initialization.

**3.2.40 null packet:** A packet in which no clocked data is transmitted on Serial Bus between DATA\_PREFIX and DATA\_END.

**3.2.41 octlet:** Eight bytes, or 64 bits, of data.

**3.2.42 originating port:** A transmitting port on a PHY which has no active receiving port. The source of the transmitted packet is either the PHY's local link or the PHY itself.

3.2.43 packet: A sequence of bits transmitted on Serial Bus and delimited by DATA\_PREFIX and DATA\_END.

**3.2.44 payload:** The portion of a primary packet that contains data defined by an application.

**3.2.45 PHY packet:** A 64-bit packet where the most significant 32 bits are the one's complement of the least significant 32 bits.

3.2.46 physical ID: The least-significant 6 bits of the node ID. On a particular bus, each node's physical ID is unique.

**3.2.47 physical layer (PHY):** The Serial Bus protocol layer that translates the logical symbols used by the link layer into electrical signals on Serial Bus media. The physical layer is self-initializing. Physical layer arbitration guarantees that only one node at a time is sending data. The mechanical interface is defined as part of the physical layer. There are different physical layers for the backplane and for the cable environment.

**3.2.48 ping:** A term used to describe the transmission of a PHY packet to a particular node in order to time the response packet(s) provoked.

**3.2.49 port:** The part of the PHY that allows connection to one other node.

**3.2.50 primary packet:** Any packet that is not an acknowledge or a PHY packet. A primary packet is an integral number of quadlets and contains a transaction code in the first quadlet.

3.2.51 quadlet: Four bytes, or 32 bits, of data.

3.2.52 repeating port: A transmitting port on a PHY that is repeating a packet from the PHY's receiving port.

**3.2.53 request:** A primary packet (with optional data) sent by one node's link (the requester) to another node's link (the responder).

**3.2.54 response:** A primary packet (with optional data) sent in response to a request subaction.

**3.2.55 resuming port:** A previously suspended port which has observed bias or has been instructed to generate bias. In either case, the resuming port engages in a protocol with its connected peer PHY in order to reestablish normal operations and become active.

**3.2.56 self-ID packet:** A PHY packet transmitted by a cable PHY during the self-ID phase or in response to a PHY ping packet.

**3.2.57 speed code:** The code used to indicate bit rates for Serial Bus.

**3.2.58 split transaction:** A transaction where unrelated subactions may take place on the bus between its request and response subactions.

**3.2.59 subaction gap:** For an asynchronous subaction, the period of idle bus that precedes arbitration.

**3.2.60 subaction:** A complete link layer operation: optional arbitration, packet transmission and optional acknowledgment.

**3.2.61 suspend initiator:** An active port that transmits the TX\_SUSPEND signal and engages in a protocol with its connected peer PHY to suspend the connection.

**3.2.62 suspend target:** An active port that observes the RX\_SUSPEND signal. A suspend target requests all of the PHY's other active ports to become suspend initiators while the suspend target engages in a protocol with its connected peer PHY to suspend the connection.

**3.2.63 suspended domain:** One or more suspended nodes linked by suspended connection(s). Two nodes are part of the same suspended domain if there is a physical connection between them and all ports on the path are suspended. A boundary node is adjacent to one or more suspended domain(s) but not part of the suspended domain(s).

**3.2.64 suspended node:** An isolated node with at least one port that is suspended.

**3.2.65 suspended port:** A connected port not operational for normal Serial Bus arbitration but otherwise capable of detecting both a physical cable disconnection and received bias.

**3.2.66 talker:** An application at a node that transmits a stream packet.

**3.2.67 terabyte:** A quantity of data equal to  $2^{40}$ , or 1099511627776, bytes.

**3.2.68 transaction layer:** The Serial Bus protocol layer that defines a request-response protocol for read, write and lock operations.

**3.2.69 transaction:** A request and the optional, corresponding response.

**3.2.70 transmitting port:** Any port transmitting clocked data or an arbitration state. A transmitting port is further characterized as either originating or repeating.

3.2.71 unified transaction: A transaction completed in a single subaction.

**3.2.72 unit:** A component of a Serial Bus node that provides processing, memory, I/O or some other functionality. Once the node is initialized, the unit provides a CSR interface. A node may have multiple units, which normally operate independently of each other.

**3.2.73 unit architecture:** The specification document that describes the interface to and the behaviors of a unit implemented within a node.

# 4. New features (informative)

The changes to IEEE Std 1394-1995 contained in this supplement are related to each other only in that they are incremental enhancements or extension to the existing standard. This section provides an informative description of some of these new facilities, which is intended as a foundation for the reader's better understanding of the normative specifications that follow.

# 4.1 Connection debounce

In the cable environment, Serial Bus configures itself and assigns a unique 6-bit physical ID to each of the 63 devices that may be interconnected within a single arbitration domain. The bus initialization and configuration process is triggered by a change in connection status at any PHY port: one or more devices have been added or removed and the connection topology has changed.

IEEE Std 1394-1995 specifies that a change in detected bias voltage causes an instantaneous connection status change and commences bus initialization. Unfortunately, this idealized model fails to account for two aspects of the physical world:

- The connection process is asymmetric. When two nodes are connected, it is extraordinary for bias to be detected by both at the same time. The node that detects bias first immediately commences a bus reset but is unable to complete bus initialization until the other node detects bias and also commences a bus reset. During this interval, which may be on the order of tens of milliseconds, the first node is unable to send or receive packets. If that node is connected to others, that entire Serial Bus is unable to operate normally; and

- The connection process is not smooth. As the plug and connector scrape together, electrical contact is made and broken many times. Bus initialization requires no more than approximately 200 µs but the completion of the insertion proceeds at a human pace. What appears to the user as one new connection may generate a storm of connections and disconnections.

All of this occurs quickly by human standards but the disruption caused to normal bus operations is particularly serious for isochronous data.

The problem of contact scrape is fairly simple to resolve: implement a connection time-out before new connections are confirmed. Disconnections may be detected immediately. There is no need to measure the connection time-out with great precision. An *n*-stage counter could derive a clock tick from the PHY's 24.576 MHz clock on the order of 5 ms; an overall time-out in the vicinity of 340 ms is adequate to debounce the contact scrape.

The problem of connection asymmetry is not solved by the connection timer. The first step in its solution is to require that all arbitration line states (except BUS\_RESET) be ignored during the connection time-out interval. If BUS\_RESET is observed, skip the remaining connection time-out interval and commence a bus reset. This works well when the connection is between two P1394a (new) PHYs or between an isolated node with a new PHY connected to an IEEE Std 1394-1995 (old) PHY of an operational bus.

In the case where an isolated node with an old PHY is connected to a new PHY of an operational bus, the old PHY generates a storm of bus resets which are propagated by the new PHY. This may be avoided if the new PHY implements an additional "reset detect" time-out of approximately 80 ms before it responds to BUS\_RESET.

## 4.2 Cable arbitration enhancements

At the time IEEE Std 1394-1995 was in the final steps towards becoming a standard, a number of valuable performance enhancements had been identified. Their overall effect is to reclaim Serial Bus bandwidth used unnecessarily in arbitration and make it available for data transmission. This both increases the throughput of the bus as a whole and reduces the latency of individual transactions.

# 4.2.1 Arbitrated (short) bus reset

The addition of connection debounce, described above, does much to reduce the time the bus is unusable during bus initialization. However, even under ideal circumstances, *e.g.*, a bus reset initiated by software, that involve no physical connection changes, bus initialization as specified by IEEE Std 1394-1995 is still more time consuming than it needs to be. Bus initialization is composed of three phases: reset, tree identify and self-identify. The last phase, self-identify, requires approximately one microsecond per node or about 70  $\mu$ s worst case when there are 63 nodes. Tree identify is also quite rapid and takes less than 10  $\mu$ s. The longest phase is bus reset and it lasts about 167  $\mu$ s while the BUS\_RESET signal is propagated. The total duration of bus initialization is longer than the nominal isochronous cycle time, 125  $\mu$ s, and may disrupt two isochronous periods. This compels device designers to add additional buffer depth to preserve the smooth flow of isochronous data from the perspective of their application. If sufficient time could be trimmed from bus initialization the necessity for larger buffers could be reduced.

The reason for the long duration of BUS\_RESET is that a transmitting node is unable to detect this arbitration line state. It is only after packet transmission is complete that the node will observe the reset. Hence BUS\_RESET must be asserted longer than the longest possible packet transmission. This guarantees the success of bus reset regardless of the bus activity in progress.

Suppose a node arbitrates for and is granted control of Serial Bus; now all the other nodes are in the receive state. If BUS\_RESET is transmitted, all the nodes will detect it. In this case, the bus reset duration can be shortened to approximately 1.3  $\mu$ s. The worst case bus initialization time is improved from roughly 250  $\mu$ s to 80  $\mu$ s for a bus fully populated by 63 devices<sup>1</sup>. Typical bus initialization times would be shorter, for example approximately 20  $\mu$ s for a bus with 16 devices.

The concept is simple but requires analysis for particular cases:

- Parent port disconnection. A prerequisite for arbitrated (short) bus reset is the ability to arbitrate. Since there is no longer a connection to the root, the long bus reset defined by IEEE Std 1394-1995 is all that is available;

- Child port disconnection. The node requests the bus and, if granted control of the bus, initiates a short reset. If the arbitration request ultimately fails because of an arbitration state time-out, a long bus reset is initiated;

- New connection (root node or a node with a parent port). After the connection time-out, the node requests the bus and, if granted control of the bus, initiates a short reset. If the arbitration request ultimately fails because of an arbitration state time-out, a long bus reset is initiated; and

- New connection (isolated node). The isolated node should defer bus reset in anticipation that the other node, after its connection time-out, successfully arbitrates and initiates a short reset. If the isolated node fails to observe BUS\_RESET within a second, it initiates a long bus reset.

When two buses are connected it is extremely unlikely that timings align to produce a short bus reset. Both nodes that sense the new connection are behaving as in the third item above and one will likely win arbitration before the other. When the slower node observes BUS\_RESET it initiates a long reset. Even in the event that the slower node fails to sense the reset, the other node's bus initialization process will time out and a long bus reset will result.

## 4.2.2 Ack-accelerated arbitration

The timing strategy for asynchronous arbitration specified by IEEE Std 1394-1995 is straightforward: arbitration cannot start until the bus is idle for a subaction gap time. For a bus with few nodes the subaction gap might be one microsecond while for a bus with 63 nodes it could be  $5 \mu s$ . This design was adopted when simplicity, proof of concept and time to market were of greater importance to Serial Bus than the extraction of the last possible bit of bandwidth. However, the penalty of wasted bus idle time becomes increasingly onerous as transmission rates and the number of connected nodes increase.

<sup>&</sup>lt;sup>1</sup> The calculation is based on the assumption that worst case PHY repeater delay and cable delay together are less than 500 ns; this would permit up to 100 m of cable.

The duration of a subaction gap is determined by bus topology; it is necessary for it to be greater than the worst case round-trip propagation time between any two nodes on the bus. This ensures that, after the transmission of an asynchronous primary packet, no node starts arbitration before the acknowledge packet has been transmitted and received. Unfortunately this makes no distinction between acknowledge packets and primary packets: an acknowledge packet never follows an acknowledge packet. Arbitration can start immediately after an acknowledge packet is observed.

NOTE—In a sense this is not a new form of arbitration but exactly the form of arbitration used for isochronous packets. Since there are no acknowledge packets during the isochronous period, isochronous arbitration starts as soon as an idle gap is detected after a packet.

# 4.2.3 Fly-by concatenation

IEEE Std 1394-1995 defines one arbitration enhancement, concatenated subactions. This is a method of completing a split transaction without relinquishing the bus in between the acknowledge packet and the response packet. From the standpoint of the link that receives both the acknowledge packet and the response packet, it is impossible to distinguish between concatenated subactions and closely spaced subactions separated by an intervening arbitration. This provides an opportunity to reclaim more Serial Bus bandwidth for data transmission.

Suppose a node has a packet ready for transmission when an unrelated packet addressed to the same node is received and acknowledged. Are there any consequences if the node concatenated the packet awaiting transmission to the acknowledge packet? This sequence of received packet, acknowledge packet and transmitted packet is indistinguishable from the concatenated subactions permitted by IEEE Std 1394-1995—except for the content of the transmitted packet. Provided that fair arbitration is observed and some timing and topology issues are considered, Serial Bus operates as before.

One consideration is that fly-by concatenation may be used only when the candidate packet is received on a child port or is originated by the node's link. When a packet is received on a parent port it is likely that other nodes are simultaneously receiving the packet. If more than one node attempted fly-by concatenation, their transmitted packets would collide. When a packet is originated by the node's link or received on a child port, packet reception is unique: it is not possible for any other node to be receiving the same packet on a child port at the same time.

When a packet is received on a child port or is originted by the node's link, there are two opportunities for fly-by concatenation:

- after an acknowledge packet, an unrelated asynchronous primary packet may be concatenated; or

- after a cycle start packet or isochronous packet, an isochronous packet may be concatenated.

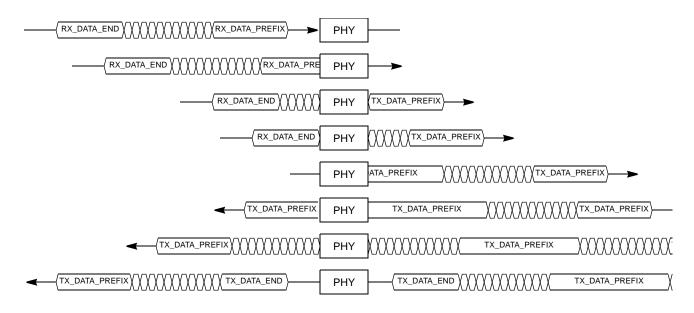

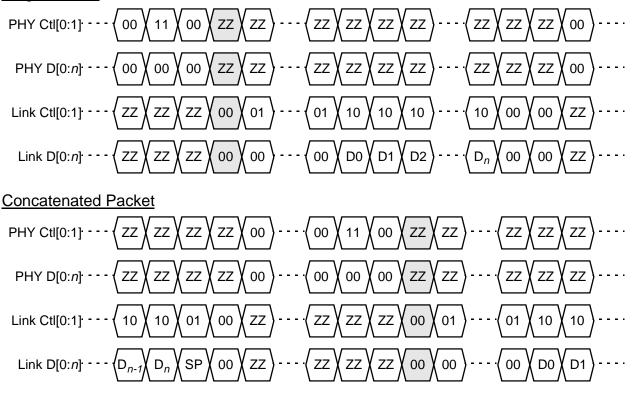

Figure 4-1 — Fly-by concatenation

Fly-by concatenation is illustrated by figure 4-1. The transmitted packet appears concatenated on the repeating ports but as a separate packet transmitted by the child port. The figure shows a two-port PHY with a child port at the left. At the outset, a packet is about to be received by the child port. In the succeeding snapshots of Serial Bus state for both ports of the PHY time moves down the page. As the received packet is repeated by the other port it is seen to emerge, first the data prefix (now signaled as TX\_DATA\_PREFIX by the repeating port), then the clocked data of the packet. The packet retransmission is nearly complete as trailing TX\_DATA\_PREFIX is signaled by the repeating port; the use of data prefix instead of data end on retransmission signals concatenation. In the last snapshots, the concatenated packet is seen to emerge from both ports of the PHY; on the original receiving port the new packet appears as a single, unconcatenated packet.

# 4.2.4 Multi-speed packet concatenation

IEEE Std 1394-1995 was published before 200 Mbit/s and faster PHYs were available. As a consequence, the details of operation at speeds other than S100 are sketchy and in some cases susceptible to multiple interpretations, each of which is arguably reasonable. As an example, IEEE Std 1394-1995 contains a contradictory requirement that PHYs signal speed only for the first packet of a multiple packet sequence but expect to observe a separate speed signal for each received packet.

Apart from the interoperability problems, multi-speed packet concatenation is an essential building block for the enhancements specified by this supplement because it permits:

- concatenation of a read response of arbitrary speed after an acknowledge packet;

- concatenation of isochronous packets without regard to the speed of each; and

- fly-by concatenation without regard to the speed of the concatenated packet.

The deficiencies of IEEE Std 1394-1995 with respect to multi-speed packet concatenation are corrected in both the PHY/link interface specified in section 5 and the PHY state machines and C language code in section 7. Complete interoperability with older PHYs cannot be guaranteed but is promoted by a requirement that S100 packets cannot be concatenated after faster packets.

## 4.2.5 Arbitration enhancements and cycle start

There are interoperability problems created by the enhancements described above when utilized by nodes other than the cycle master (root). The problem arises when the cycle master needs to transmit a cycle start packet. Existing nodes give precedence to arbitration requests from child ports over their own requests. When none of the nodes implement arbitration enhancements, this is not a problem: a subaction gap will appear at the end of any transaction in progress and the root, by virtue of its natural arbitration priority, will win arbitration and be able to send the cycle start packet. If some or all of the child nodes are employing arbitration enhancements, the root may be unable to win arbitration for a protracted period. IEEE Std 1394-1995 is designed to accommodate a delayed cycle start packet, but only up to the extent of the longest asynchronous primary packet. The delay caused by the root's children could violate isochronous timing assumptions and disrupt the flow of isochronous data.

The solution is to define new requests over the interface between the link and PHY so that the link may selectively disable and enable ack-accelerated and fly-by concatenation enhancements when a cycle start is due to be transmitted. All nodes except the cycle master are required to disable these accelerations from the time of their local cycle synchronization event until a cycle start packet is observed. Once the cycle start packet is observed it is safe to reenable acceleration.

## 4.3 Performance optimization via PHY "pinging"

The simplest performance improvement that a bus manager can make is to tune the "gap count" to the topology of Serial Bus. The gap count determines the value of two fundamental time intervals, the subaction gap and the arbitration reset gap. The smaller the gap count, the less idle bus time consumed by these gaps.

IEEE Std 1394-1995 contains recommendations that permit the bus manager to reduce the gap count from the default  $3F_{16}$  in effect after bus reset. The bus manager<sup>2</sup> calculates the worst case round-trip propagation delay between any two nodes on the bus. The calculation should be based upon the greatest hop count between any two nodes (as determined from the self-ID packets) and an assumption that cable lengths do not exceed 4.5 meters. Some implementations do not analyze the self-ID packets to determine the greatest hop count but assume a maximum hop count of 16. Approximate as they are, neither the cable length nor maximum hop count assumption is reliable, since they are not normative requirements of IEEE Std 1394-1995.

This supplement provides an alternate method for the bus manager to optimize gap count: the PHY "ping" packet. This is a packet that is addressed to any one of the 63 local nodes on a bus. In response, the addressed PHY returns a set of self-ID packets. The originator of the ping packet may time the transaction and calculate a round-trip time between itself and the targeted PHY.

With these tools, the bus manager can readily calculate the round-trip time between any two leaf nodes, as explained in more detail in annex C.

NOTE—For the purpose of calculating the round-trip time, the contents of the packet returned by the PHY are unimportant. The return of the self-ID packet(s) permits some additional diagnostic utility in the bus manager. Alternatively, the bus manager could address some other packet, such as the remote access packets defined for the suspend / resume facility, and time the packet sent in response.

# 4.4 Priority arbitration

A fundamental part of IEEE Std 1394-1995 is the concept of "fairness", which ensures that all nodes on the bus are each able to arbitrate within a bounded time period: no node may starve another node's arbitration requests. Within any particular period (called a "fairness interval") the order in which nodes are granted the bus is arbitrary, but each node is guaranteed fair access.

This mechanism is useful to promote equal access to the bus, but individual nodes may consume bus time awaiting their chance to arbitrate. These inefficiencies can be significant, particularly in cases where there are few nodes attached to the bus.

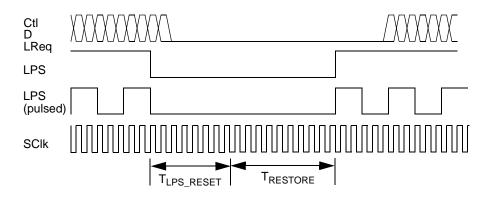

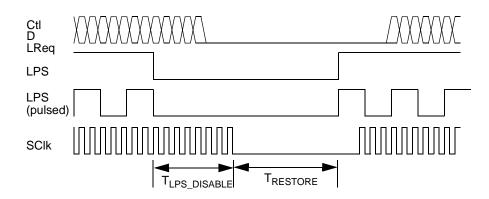

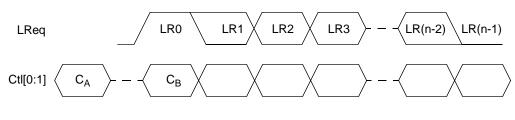

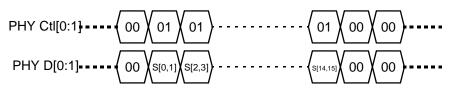

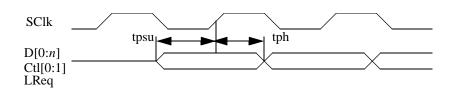

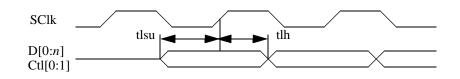

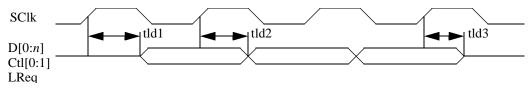

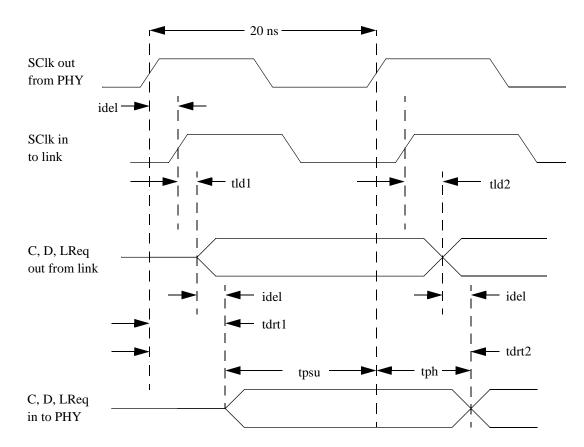

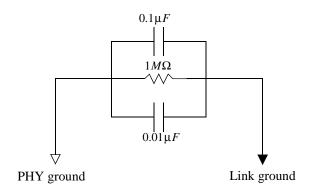

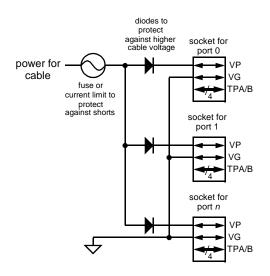

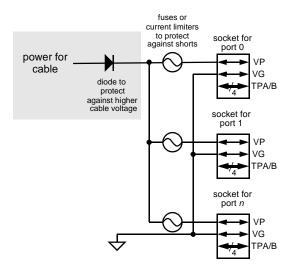

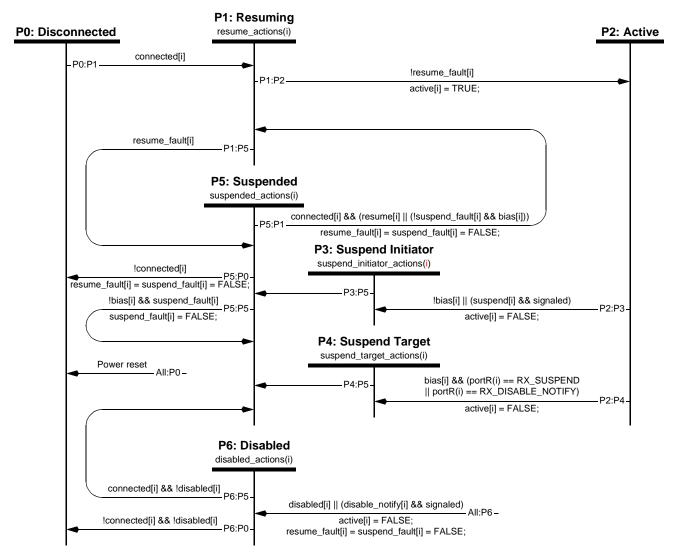

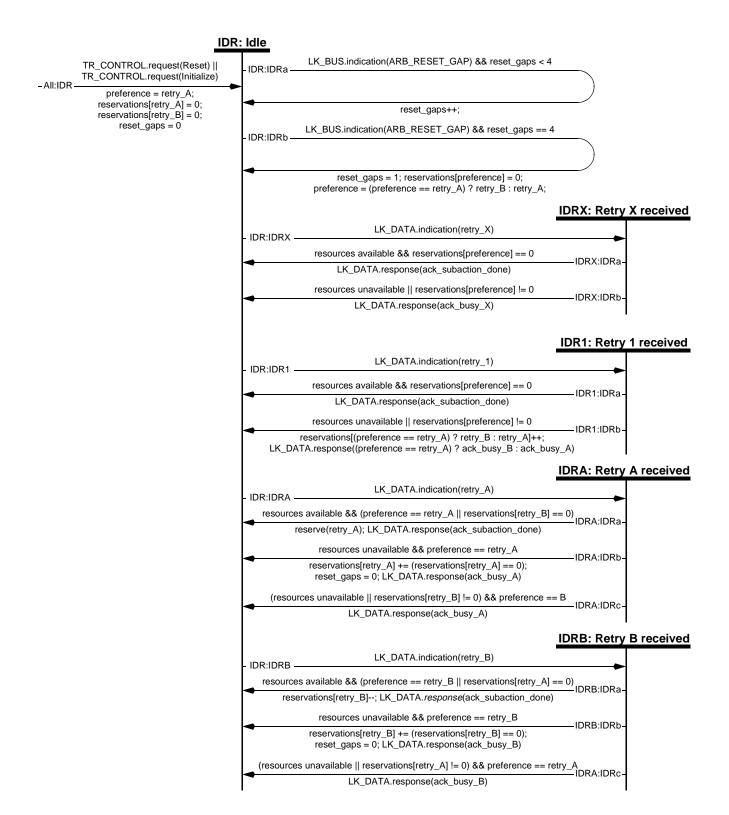

One opportunity to improve efficiency concerns response subactions. Since each response subaction is originally triggered by a request subaction, it is arguably true that fair arbitration for requests inherently limits the number of responses. Hence the new provision of this supplement that responses shall always be permitted to use priority arbitration.