#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Verification and Analysis of System Designs With Functional and Performance Constraints

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Computer Science**

by

Xi Chen

August 2005

Dissertation Committee: Dr. Harry Hsieh, Chairperson Dr. Felice Balarin Dr. Laxmi N. Bhuyan Dr. Frank Vahid

Copyright by Xi Chen 2005 The Dissertation of Xi Chen is approved:

Committee Chairperson

University of California, Riverside

#### ACKNOWLEDGMENTS

First and foremost, I would like to express my gratitude to Prof. Harry Hsieh, who has led me to the research field and guided me throughout the entire graduate career with his constant enthusiasm and patience. Harry has taught me almost everything about being a qualified researcher. Without his invaluable encouragement and support, I would not have been able to finish this work.

I am also grateful to Dr. Felice Balarin and Dr. Yosinori Watanabe from Cadence Berkeley Laboratories for their important advice and contributions to this work. I have benefited significantly from the collaboration and discussions with them. Their suggestions and comments have always substantially influenced and improved the final results.

I must also thank team members of the Metropolis project led by Prof. Sangiovanni-Vincentelli from University of California at Berkeley. The work presented here has mostly been done within the framework of the Metropolis project, and it has benefited greatly from many discussions with team members.

Thanks also go to the computer architecture group led by Prof. Laxmi Bhuyan for providing me with their network processor simulator NePSim, a comprehensive and realistic experimental platform for several case studies presented in this thesis. To my wife and parents.

#### ABSTRACT OF THE DISSERTATION

#### Verification and Analysis of System Designs With Functional and Performance Constraints

by

Xi Chen

#### Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, August 2005 Dr. Harry Hsieh, Chairperson

With the increasing complexity and heterogeneity of today's embedded systems, design methodologies at higher levels of abstraction become a necessity. It is expected that the next major productivity gain will come in the form of system level design since designing at the register transfer level or sequential C-code level is no longer efficient. It follows that new verification and analysis technologies have to be developed in each and every step of the design flow in order to catch design errors as early as possible and to reduce the overall design cost.

Simulation remains a major means of verification for complex system level designs, especially when designs are refined with more design details realized. In this work, a simulation verification methodology is proposed based on trace analysis and automatic trace checker generation. From formal specification of design constraints with mathematical logics such as Linear Temporal Logic (LTL) and Logic of Constraints (LOC), i.e. formal assertions, monitors or checkers are automatically generated and used to verify simulation traces during or after simulation. As a major contribution, LOC formalism is extensively studied, and an efficient checking algorithm is proposed. LOC is also used in automatic generation of distribution analysis tools, which have been exercised on low power techniques in network processor architectures. By utilizing formal assertions, a designer can easily verify both functional and performance constraints of a design in simulation. In addition, a deadlock analysis mechanism is proposed with built-in simulation monitors. This approach is demonstrated in the Metropolis design framework.

For small but important designs or library modules that will be instantiated many times, exhaustive verification is possible and useful. A formal verification methodology for system level design is therefore proposed, where an existing software formal verification tool (e.g. Spin) is utilized as the back-end verification engine, and an automatic translation mechanism from system specifications to verification models is developed. Furthermore, automatic abstraction propagation algorithms can be used to simplify the verification models. In this study, Metropolis is used as a major experiment platform, where a designer is allowed to formally verify design constraints specified with LTL and LOC within the integrated design framework.

# Contents

| Li | st of Figures xii    |                                        |    |  |  |

|----|----------------------|----------------------------------------|----|--|--|

| Li | ist of Tables        |                                        |    |  |  |

| 1  | Intr                 | oduction                               |    |  |  |

|    | 1.1                  | System Level Design                    | 2  |  |  |

|    | 1.2                  | Verification Methods                   | 3  |  |  |

|    | 1.3                  | Functional and Performance Constraints | 5  |  |  |

|    | 1.4                  | Metropolis Design Framework            | 10 |  |  |

|    |                      | 1.4.1 Framework and Design Methodology | 10 |  |  |

|    |                      | 1.4.2 Metropolis Meta-Model Language   | 11 |  |  |

|    | 1.5                  | Thesis Overview                        | 15 |  |  |

| 2  | Logic of Constraints |                                        | 18 |  |  |

|    | 2.1                  | Introduction to LOC                    | 18 |  |  |

|    | 2.2                  | LOC Syntax and Semantics               | 22 |  |  |

|   | 2.3 | Expressiveness of LOC                                               | <br>24 |

|---|-----|---------------------------------------------------------------------|--------|

|   | 2.4 | Checking LOC Formulas with Simulation                               | <br>27 |

|   |     | 2.4.1 Runtime Monitoring                                            | <br>30 |

|   |     | 2.4.2 Dealing with Memory Limitation                                | <br>31 |

|   |     | 2.4.3 A Case Study of FIR Filter                                    | <br>32 |

|   | 2.5 | Formal Verification of LOC Formulas                                 | <br>35 |

|   | 2.6 | Complexity of Verifying LOC Formulas                                | <br>38 |

| 3 | Sim | lation Verification and Analysis Based on Formal Assertions         | 50     |

|   | 3.1 | Methodology of Simulation Verification and Analysis                 | <br>50 |

|   | 3.2 | Simulation Verification in Metropolis                               | <br>52 |

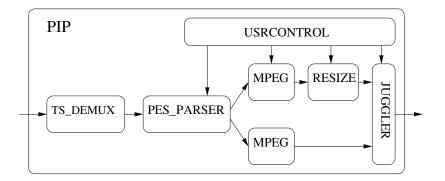

|   |     | 3.2.1 A Picture-in-Picture Design                                   | <br>53 |

|   |     | 3.2.2 A Function-Architecture Mapping Model                         | <br>56 |

|   | 3.3 | Verification for Network Processor Architectures                    | <br>58 |

|   |     | 3.3.1 Introduction to Network Processors                            | <br>59 |

|   |     | 3.3.2 Network Processor Model                                       | <br>61 |

|   |     | 3.3.3 Experimental Settings                                         | <br>63 |

|   |     | 3.3.4 Verification Studies                                          | <br>65 |

|   | 3.4 | Performance and Power Analyis for Network Processor Architectures . | <br>74 |

|   |     | 3.4.1 Experimental Settings                                         | <br>75 |

|   |     | 3.4.2 Dynamic Voltage Scaling                                       | <br>77 |

|   |      | 3.4.3   | Power Analysis                              | 78  |

|---|------|---------|---------------------------------------------|-----|

|   |      | 3.4.4   | Design Exploration for DVS                  | 81  |

| 4 | Dea  | dlock A | nalysis with Built-in Simulation Monitors   | 91  |

|   | 4.1  | Introd  | uction to Deadlock Analysis                 | 92  |

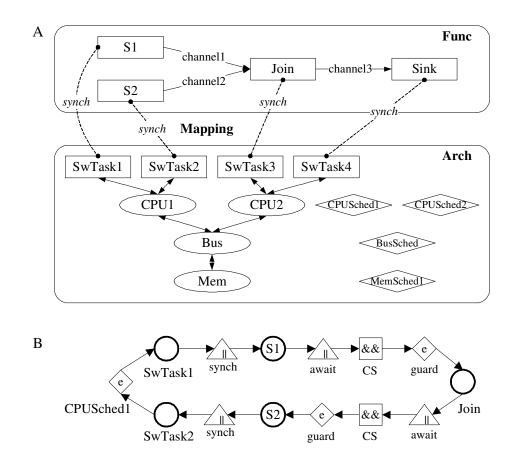

|   | 4.2  | Synch   | ronization in Metropolis                    | 95  |

|   |      | 4.2.1   | Synchronization Constructs                  | 95  |

|   |      | 4.2.2   | Deadlock in Metropolis                      | 98  |

|   | 4.3  | Synch   | ronization Dependency and Deadlock Analysis | 100 |

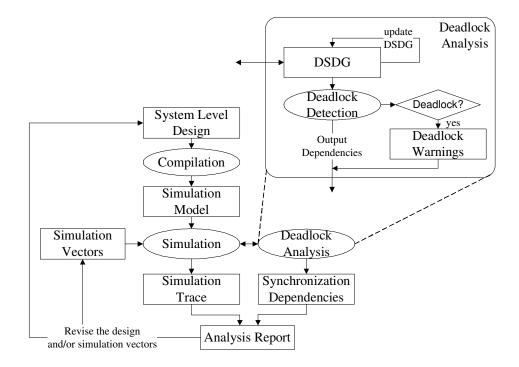

|   |      | 4.3.1   | Deadlock Analysis Methodology               | 100 |

|   |      | 4.3.2   | Dynamic Synchronization Dependency Graph    | 101 |

|   |      | 4.3.3   | Deadlock Detection Algorithm                | 105 |

|   |      | 4.3.4   | Implementation                              | 106 |

|   | 4.4  | Case S  | Studies of Deadlock Analysis                | 108 |

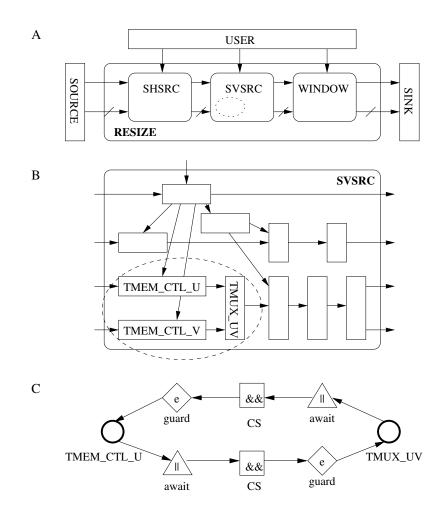

|   |      | 4.4.1   | A Function Model for Video Processing       | 108 |

|   |      | 4.4.2   | A Function-Architecture Mapping Model       | 111 |

| 5 | Form | nal Ver | ification for System Level Designs          | 114 |

|   | 5.1  | Introd  | uction to Formal Verification               | 115 |

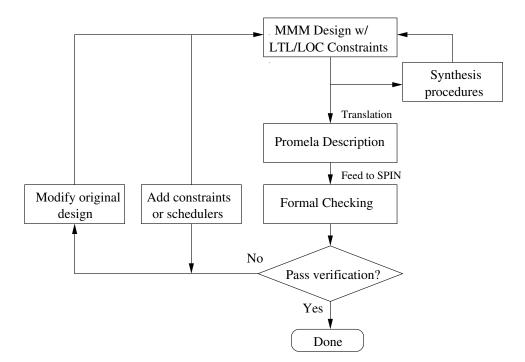

|   | 5.2  | Forma   | l Verification Methodology                  | 117 |

|   | 5.3  |         | ation from MMM to Promela                   |     |

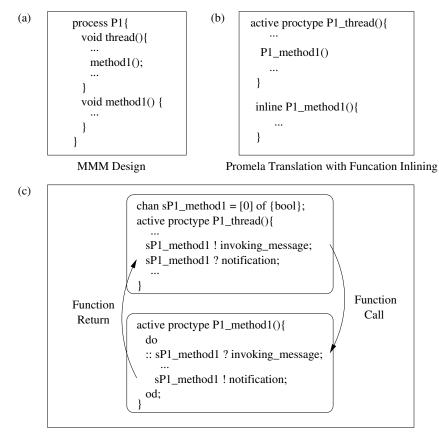

|   |      | 5.3.1   | MMM Processes                               | 121 |

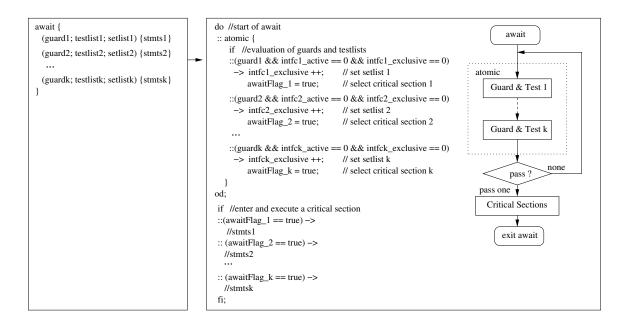

|     |        | 5.3.2    | Interfaces and Await Statements    | . 123 |

|-----|--------|----------|------------------------------------|-------|

|     |        | 5.3.3    | Dynamic Objects                    | . 124 |

|     |        | 5.3.4    | Function-Architecture Mapping      | . 125 |

|     | 5.4    | Produc   | er-Consumer Network                | . 126 |

|     |        | 5.4.1    | Verification of Data Integrity     | . 126 |

|     |        | 5.4.2    | Assumptions and Schedulers         | . 129 |

|     |        | 5.4.3    | Transformation and Refinement      | . 130 |

|     | 5.5    | Autom    | atic Abstraction and Propagation   | . 132 |

|     |        | 5.5.1    | Control and Data Dependency Graph  | . 135 |

|     |        | 5.5.2    | Abstraction Propagation Algorithms | . 137 |

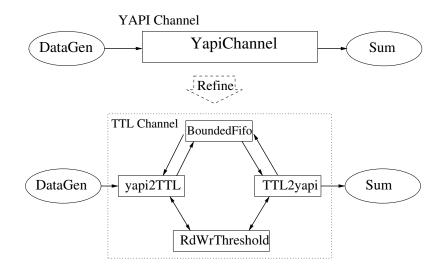

|     | 5.6    | Formal   | Verification for TTL Channel       | . 140 |

|     |        | 5.6.1    | A Deadlock Free Constraint         | . 141 |

|     |        | 5.6.2    | Checking Data Consistency          | . 143 |

| 6   | Cone   | clusions | 3                                  | 146   |

| Bil | bliogr | aphy     |                                    | 149   |

| A   | Forn   | nal LOO  | C Syntax and Semantics             | 154   |

|     | A.1    | Repres   | enting System Behaviors            | . 154 |

|     | A.2    | LOC S    | yntax                              | . 156 |

|     | A.3    | LOC S    | emantics                           | . 158 |

| B | Proof of LOC Verification Complexity |                    |     |  |  |

|---|--------------------------------------|--------------------|-----|--|--|

|   | B.1                                  | Proof of Theorem 1 | 162 |  |  |

|   | B.2                                  | Proof of Lemma 1   | 165 |  |  |

# **List of Figures**

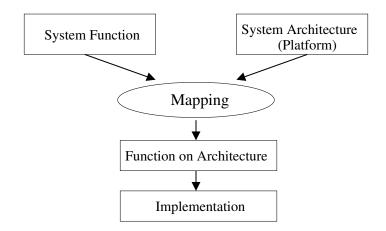

| 1.1 | System level design methodology                                                       | 3  |

|-----|---------------------------------------------------------------------------------------|----|

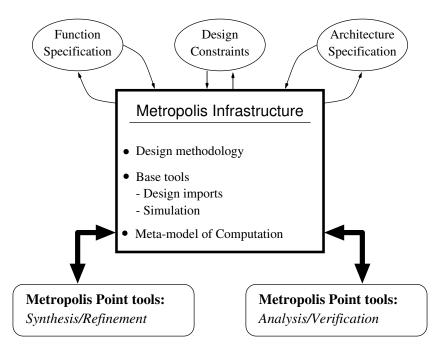

| 1.2 | Metropolis design framework                                                           | 11 |

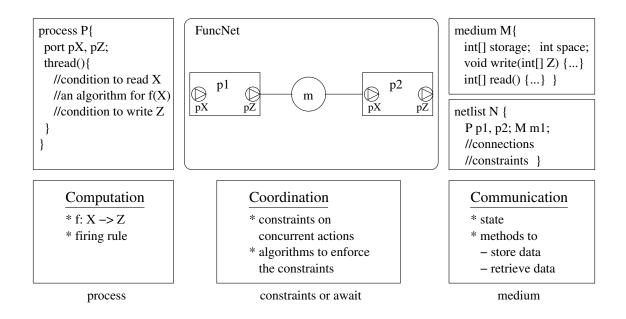

| 1.3 | An example of MMM specification                                                       | 13 |

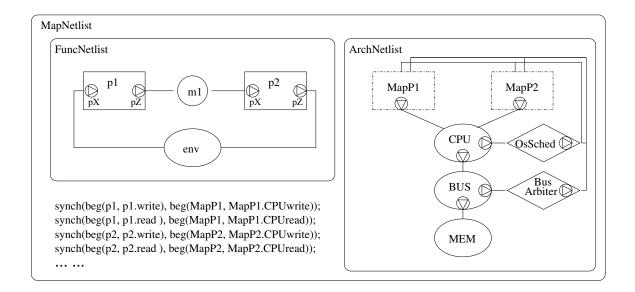

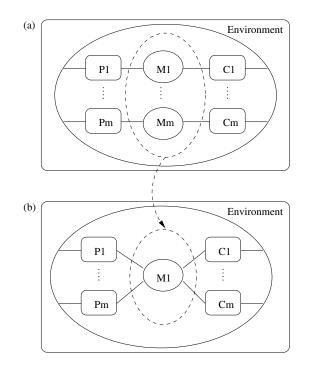

| 1.4 | Function-architecture mapping                                                         | 15 |

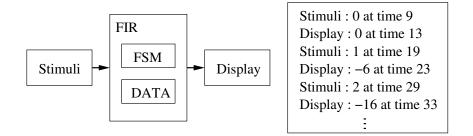

| 2.1 | A FIR design and its simulation trace                                                 | 32 |

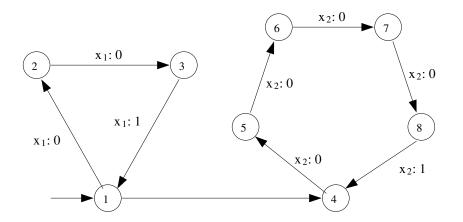

| 2.2 | A system generating 1 for every third value of $x_1$ and every fifth value of $x_2$ . | 44 |

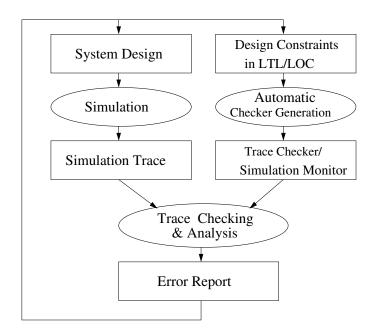

| 3.1 | Simulation verification and analysis based on formal assertions                       | 51 |

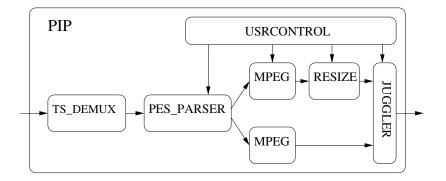

| 3.2 | Picture-in-Picture design                                                             | 53 |

| 3.3 | PiP simulation trace                                                                  | 54 |

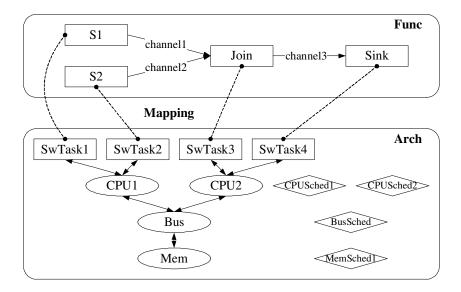

| 3.4 | A function-architecture mapping model                                                 | 56 |

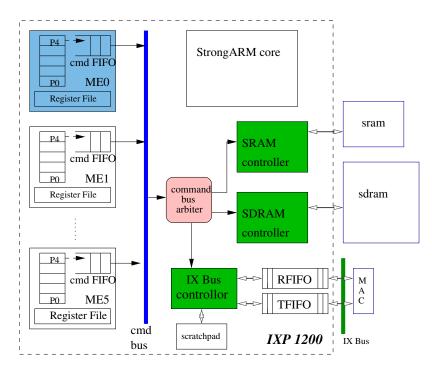

| 3.5 | IXP1200 architecture                                                                  | 62 |

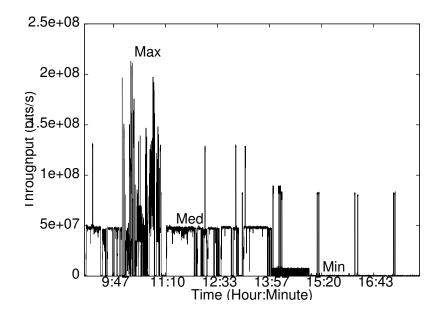

| 3.6 | NePSim simulation trace                                                               | 65 |

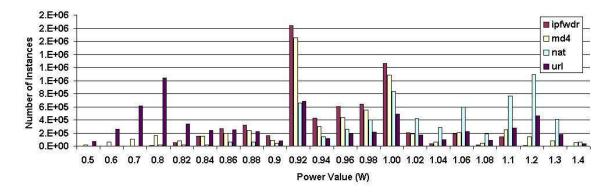

| 3.7 | Distribution of IP packets                                                            | 76 |

| 3.8 | NePSim simulation trace for performance and power analysis                            | 78 |

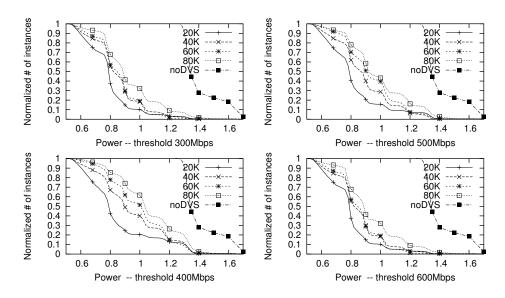

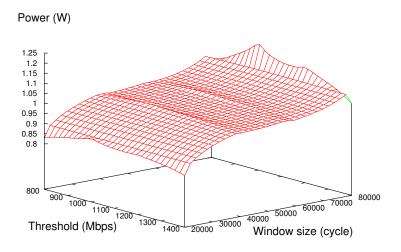

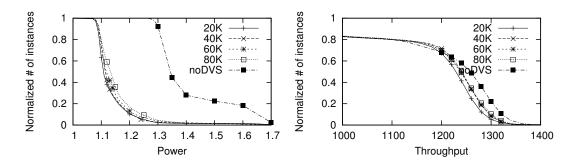

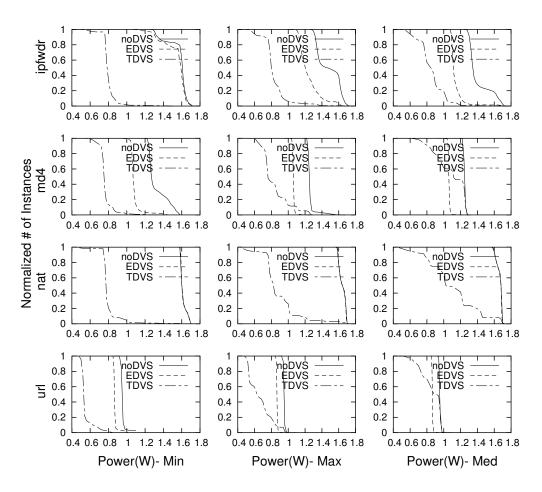

| 3.9  | Power distribution graph for 4 benchmarks                     |

|------|---------------------------------------------------------------|

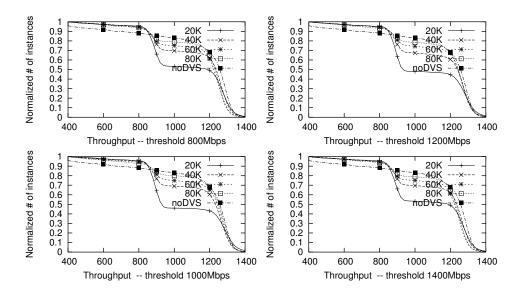

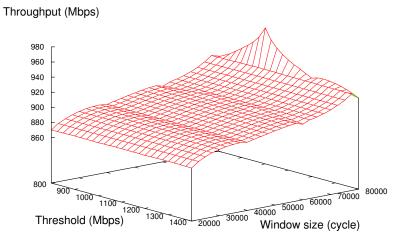

| 3.10 | Power under different design points with TDVS                 |

| 3.11 | Throughput under different design point with TDVS             |

| 3.12 | Power under different design points with TDVS                 |

| 3.13 | Throughput under different design points with TDVS            |

| 3.14 | Power and performance distribution for EDVS                   |

| 3.15 | Energy comparisons for employing DVS                          |

| 4.1  | An example of synch constraint                                |

| 4.2  | Deadlock analysis methodology                                 |

| 4.3  | DSDG examples                                                 |

| 4.4  | Picture-in-Picture design                                     |

| 4.5  | RESIZE unit and its synchronization dependencies              |

| 4.6  | A mapping model and its synchronization dependencies          |

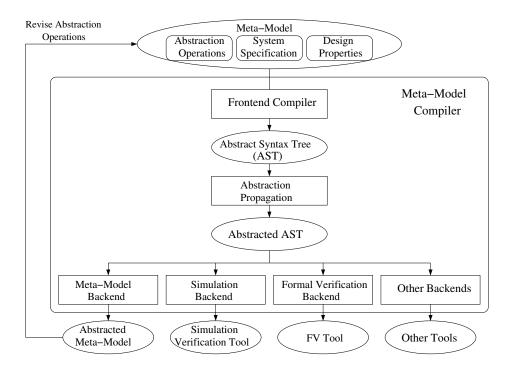

| 5.1  | Metropolis formal verification methodology                    |

| 5.2  | Example of a bytelink meta-model                              |

| 5.3  | Translations of MMM functions                                 |

| 5.4  | Translation of an await statement                             |

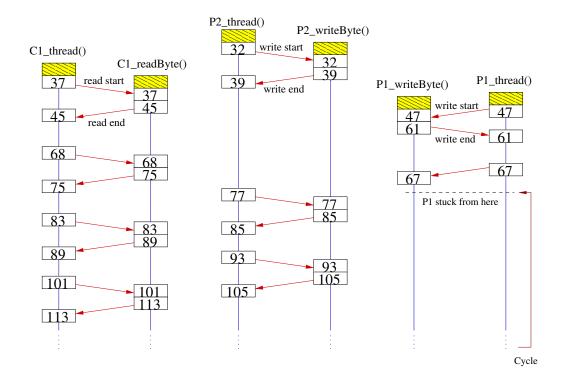

| 5.5  | Verification error trace produced by Spin                     |

| 5.6  | Example of a design refinement                                |

| 5.7  | Metropolis compiler architecture with abstraction propagation |

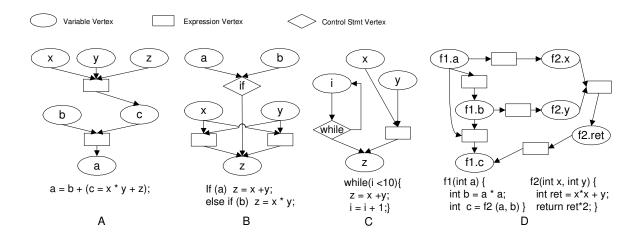

| 5.8 | CDDG examples        | 35 |

|-----|----------------------|----|

| 5.9 | API and TTL channels | 39 |

# **List of Tables**

| 2.1 | Costs of checking formulas (2.1)-(2.5) on FIR                              | 33  |

|-----|----------------------------------------------------------------------------|-----|

| 2.2 | Time usage of simulation and checking formula (2.2) on FIR $\ldots \ldots$ | 33  |

| 2.3 | Costs of checking constraint (2.7) on FIR                                  | 34  |

| 3.1 | Power and performance of Intel IXP NPUs                                    | 60  |

| 3.2 | List of events for verification                                            | 64  |

| 3.3 | Verification results for functional assertions                             | 70  |

| 3.4 | Verification results for performance assertions                            | 74  |

| 3.5 | List of events and event annotations for performance and power analysis    | 77  |

| 3.6 | Power values for the 4 benchmarks                                          | 79  |

| 3.7 | Voltage scaling values                                                     | 83  |

| 4.1 | Summary of deadlock analysis case studies                                  | 112 |

| 5.1 | Summary of verification for the producer-consumer network                  | 128 |

| 5.2 | Summary of formal verification for TTL channel                             | 142 |

| 5.3 | Summary of formal verification for data consistency                        | 145 |

|     |                                                                            |     |

## Chapter 1

# Introduction

The increasing complexity of embedded systems today demands more sophisticated design and verification methodologies. Systems are becoming more integrated as more and more functionalities and features are required for products to succeed in the market. Embedded system architectures likewise have become more heterogeneous as it is becoming more economically feasible to have various computational resources (e.g. microprocessor, digital signal processor, reconfigurable logics) all utilized on a single chip [62]. Designing at the register transfer level [38] or sequential C-code level is no longer efficient. More than ever, design and verification methodologies at higher levels of abstraction are required to fill the gap between the increasing semiconductor manufacturing capabilities and the lag-behind design productivity.

## **1.1 System Level Design**

The system level design methodology, based on orthogonalization of design concerns, as well as pre-defined platforms, has been proposed for the next major productivity gain [47]. To combat complexity and to explore design space effectively, it is necessary to represent systems at multiple levels of abstraction. Initial specification of the function and the architecture of a system is done at a high abstraction level without particular lower level implementation details. The function is then mapped onto the architecture after iterations of refinement procedures (see Figure 1.1). Significant advantages in design flexibility, as compared to the traditional fixed architecture and *a priori* partitioning approach, can result in significant advantages in the performance and design cost of the product.

Synthesis (i.e. steps taken toward implementation) is applied systematically to transform high level specifications to manufactured products. Synthesis steps may include structural transformations, a design is partitioned, composed, or otherwise altered; formal refinements, where possible behaviors of a design are formally refined through the use of constraints or implementation annotations; and mapping, where the functional specification at a particular abstraction level is mapped to an architectural specification at a particular abstraction level. There therefore exist multiple levels of abstraction in a design flow, which also indicates necessity for suitable verification techniques to be applied at each level. A formal grounding for all system representations and operations is essential for the ability to perform analysis and optimization with high degree of automation. Furthermore, abstraction is an effective oper-

Figure 1.1: System level design methodology

ation to manage complexity during verification procedures. The tendency is to abstract (or simplify) the design for verification purposes and to refine the design as more implementation details are determined.

## **1.2 Verification Methods**

In general, verification is a process to make sure if a design is what a designer intends to design. Due to the increasing complexity of today's embedded system designs, errors are likely to happen at all stages in the design flow. It has been reported that more than 70% of the development time is spent on design verification, and verification is becoming the bottleneck in the semiconductor industry according to International Technology Roadmap for Semiconductors (ITRS) [11]. This number is even expected to grow in the future and imposes yet unsolved challenges on tomorrow's design automation industry. Therefore, verification of system designs (embedded hardware/software systems) is one of the most important tasks

in the design process. To cope with the increasing complexity, various attempts have been made to increase design productivity.

Traditionally, most verification techniques have been based on simulation and testing methods [15, 40, 31]. At high levels of abstraction, executable simulation models are built from design specifications. Since it is usually prohibitive to exhaustively simulate all the possible execution paths of a simulation model, test cases are carefully designed or selected to achieve as much coverage as possible <sup>1</sup>. Testing is done at a lower abstraction level once a product prototype is available, and random test cases are automatically generated and used to check if the execution of the prototype is correct.

More recently, formal methods such as temporal property checking or symbolic model checking have become increasingly popular [51, 27]. Formal verification techniques attempt to overcome the weakness of non-exhaustive simulation by proving the correspondence between some abstract design specification and the original design. The abstract model of a design is represented symbolically or with efficient data structures such as hash tables, and then the entire state space is searched for any design errors or property violation. The complexity of searching the entire state space is at least exponential to the number of states, so formal verification techniques are expensive, and their applicability is currently restricted to small or medium sized designs or to a specific phase in the design cycle.

To make the practice of designing from high level system specification a reality, verification methods must accompany every step in the design flow. Specification at the system level

<sup>&</sup>lt;sup>1</sup>Verification coverage is the percentage of a design that is checked in the verification

makes formal verification possible. Designers can prove a property of a design by writing down the property they want to check in some logic (e.g. CTL [36] and LTL [59]), generate verification models from the design specification automatically or semi-automatically, and use a formal verification tool (e.g. the model checker SMV [55] and Spin [42]) to run exhaustive verification. Then the entire state space of the design can be searched to verify the specified property without any uncertainty.

As designs are refined with more implementation details realized, however, the complexity can quickly overwhelm the automatic tools, and simulation becomes the primary means for verification. The confidence of a simulation verification mainly depends on the design or selection of test cases. In order to uncover bugs of designs during simulation, designers can insert embedded assertions, i.e. formally specified design properties or constraints, into their design specifications in hardware description languages or high level modeling languages. Today's assertion languages capture those simple logics as language or platform specific library blocks. A set of extended temporal connectives or regular expression operators are then used to operate on those blocks for expressing more complex assertions. Examples of assertion languages include PSL [6] and OpenVera [4].

### **1.3 Functional and Performance Constraints**

In this work, Linear Temporal Logic (LTL) [59] and Logic of Constraints (LOC) [19] are two main logics used for specification of design constraints. It will be shown that LTL and LOC

have different domains of expressiveness and indeed complement each other quite well. At the verification stage, both static and runtime verification techniques can be used to check the design constraints and to report design errors if there is any constraint violation.

LTL is suitable for specifying functional constraints, such as mutual exclusion, liveness, and safety, and can effectively describe the temporal patterns of system state transitions. LTL is defined over *executions* of a system, i.e. linear sequences of *state transitions*. LTL formulas are constructed using terms, i.e. Boolean expressions on variables or system states, classical Boolean operators such as  $\neg$  (not),  $\lor$  (or),  $\land$  (and), and  $\rightarrow$  (imply), and the linear temporal operators G (always), F (eventually), X (next), and U (strong until). For example, G(A) is true if A is true for all states, F(A) is true if A eventually becomes true in a future state, X(A) is true if A is true in the following state, and A U B is true if B eventually becomes true in a future state and A is true from the current state to that future state.

It has been proved that LTL formulas can be translated to equivalent Büchi automata [63]. Based on this theory, formal techniques like model checking are developed and utilized for verification of both digital designs (e.g. SMV [55]) and software protocols(e.g. Spin [33]). LTL is also used as the basis for the formal constraint specification for simulation verification [4, 29], which is important to assure the integration and correctness of reusable IP (Intellectual Property) blocks. LTL has been a very popular and well studied logic for more than a decade, so its details will not be covered in this thesis.

We believe that the existing logics or hardware assertion languages are not natural to express more abstract constraints such as transaction level constraints, where only the events

observable from a system and their annotations are considered. Nor are they convenient to directly express performance constraints that are quantitative in nature (e.g. latency or throughput). To this end, we propose a constraint formalism: Logic of Constraints (LOC). LOC is designed for specification of performance constraints such as rate, throughput, and latency, as well as quantitative functional constraints such as I/O data consistency at the transaction level, where system events and their annotations are considered. It is very well-suited for analyzing traces from execution of higher, transaction level system models. LOC consists of all the terms and operators allowed in sentential logic [30], with additions that make it possible to specify quantitative constraints without compromising the ease of analysis. The basic components of an LOC formula include event names (e.g. *pipeline* and *sram\_enq*), instances of events (e.g. *pipeline*[4]), indices of event instances (e.g. 0, 1, ..., etc), the index variable *i*, and annotations (e.g. *cycle*, *pc*, and *addr*). LOC can be used to specify many important system level performance constraints that are inconvenient, and sometimes impossible, to specify with other logics. For example, the rate constraints:

$$cycle(pipeline[i+1]) - cycle(pipeline[i]) = 10$$

(1.1)

requires that the difference between the values of annotation *cycle* for any two consecutive instances of *pipeline* event should equal to 10. A complete study of LOC will be presented in Chapter 2.

Constraint definition is central to many methodologies. A general approach is taken by the Rosetta [16] language: different domains of computation are described declaratively and constraints can be expressed as predicates on some defined quantities. Constraints are then applied by combining the different domains. In this work, we restrict the scope of constraint definition in favor of a representation that is more natural to the designer and that is more computationally tractable.

Object Constraint Language (OCL) [1], part of the Unified Modeling Language (UML), takes a more restricted approach. OCL supports invariants, pre- and post-conditions, and guards, applied to classes, operations of classes, and states, respectively. Another related proposal is the Design Constraints Description Language (DCDL) [2] sponsored by Accellera, which is intended mostly for low-level (i.e. chip-level) constraints like clock slew, operating voltages, and port capacitances. In both of these approaches, constraints are specified for a collection of entities that represent a system (classes and their operations and states in case of OCL, and physical objects in case of DCDL). This facilitates specifying constraints associated with the system as a whole, e.g. area, yield, testability, and time to market. In contrast, we focus on specifying constraints for particular executions of a system, like response time, energy consumption, and memory usage. OCL also supports this, to some extent, through pre-conditions, post-conditions, and guards. However, while these constructs naturally express constraints on a single transition, LOC makes it easy to express constraints that span several transitions. In fact, in our approach, it is easy to specify constraints for which it is impossible to bound in advance the number of transitions needed to check them.

Many constraint formalisms have been proposed that are at most as expressive as  $\omega$ -regular languages (and in some case strictly less expressive). An incomplete list includes

S1S [22], LTL [59], PSL [6], HAAD [24], and many variants of finite-state automata on infinite words, e.g. [17, 37]. MONA [39], on the other hand, is based on regular languages and finite-state automata on finite words. It is believed that LOC is a good complement to all these approaches, as there are certain natural constraints (e.g. *data consistency* that are not  $\omega$ -regular, but can be expressed and verified (both formally and by simulation) using LOC.

Real-Time Logic (RTL) [45] is a formalism for expressing timing constraints in real-time systems. With RTL, the constraints are specified by means of timing relations on occurrences of events. RTL was primarily intended for formal reasoning, while LOC is more biased toward simulation monitoring. For example, RTL allows any number of index and time variables which can be arbitrarily quantified. This makes it very unsuitable for verification by simulation. In contrast, LOC allows only one index variable and no time variables or quantification. This choice is made precisely for the purpose of efficient simulation monitoring. Also, arithmetic in RTL is limited to Presburger arithmetic (i.e. linear inequalities), to ease formal reasoning, while LOC allows more complex expressions, because they can be handled quite easily in simulation. This separation of purposes is not total. When we consider a subset of LOC suitable for formal verification, we restrict LOC to Presburger arithmetic. Similarly, Mok and Liu have proposed a subset of RTL suitable for simulation monitoring [56, 57], and that subset indeed resembles LOC. However, they have not proposed any automatic formal verification technique for that subset. A subset of LOC suitable for formal verification can be seen as a generalization of the subset of RTL suitable for simulation monitoring, as it allows specification of constraints related to annotations other than time. In fact, data consistency,

one of the constraints that distinguish LOC from formalisms based on  $\omega$ -regular languages, also distinguishes it from RTL, as it does not involve time at all.

## **1.4 Metropolis Design Framework**

Metropolis is developed as an integrated and unified design framework for next generation system level design [20]. Metropolis allows designers to represent and manipulate their designs at multiple levels of abstraction and with multiple models of computation (MoC). Central to the design framework is a high level modeling language, Metropolis Meta-Model (MMM), and a set of back-end tools are integrated into the framework, with which one can simulate, synthesize, and verify a design at hand. Metropolis is used as the main experiment platform throughout this thesis.

### 1.4.1 Framework and Design Methodology

The integrated design environment consists of a design specification language, Metropolis Meta-Model (MMM), a front-end that constructs intermediate representations and analyzes static network structures, and a set of back-end tools that are responsible for simulation, synthesis, verification, and other tasks. Different high-level languages, models of computation, design constraints, as well as specifications of system functions, architecture platforms, and function-architecture mappings can be represented in MMM while retaining their precise semantics. Constructs in MMM are designed to facilitate transformations and refinements

Figure 1.2: Metropolis design framework

between different abstraction levels. Different design aspects are orthogonalized, such as computation versus communication, function versus architecture, and specification versus implementation. The design complexity can therefore be effectively reduced, and the design space can be efficiently explored. Figure 1.2 shows a flow diagram for the Metropolis framework.

### 1.4.2 Metropolis Meta-Model Language

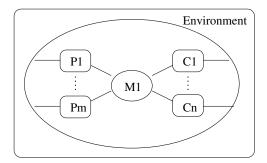

Metropolis Meta-Model is a system representation formalism capable of representing designs at different levels of abstraction. A description of a system (function and/or architecture) can be made in terms of computation, communication, and coordination.

#### **Processes, Media, and Netlists**

In Metropolis Meta-Model, systems are represented as networks of *processes* that communicate through *media* [18]. Processes and media are used to describe computation and communication respectively. The syntax of MMM is similar to Java but includes many system level modeling extensions. A process defines an active object and always includes a method called *thread* as the top-level method, where its behavior is specified. A communication medium implements a set of methods that are declared in *interfaces*. Processes connect to media through *ports*. Each port has a type that must be an interface implemented by the medium to which the port is connected. Processes communicate to each other by invoking interface methods implemented in the shared media through these ports.

In MMM, objects such as processes, media, and their connectivities can be grouped in a *netlist*, which is used to model a complete network. Figure 1.3 shows an example of a functional netlist *FuncNet*. The netlist defines two processes, p1 and p2, communicating through a medium m1. A netlist can also contains other netlists to form a hierarchical network. In addition, refinement constructs are available to specify that one netlist is the formal refinement of another within a network.

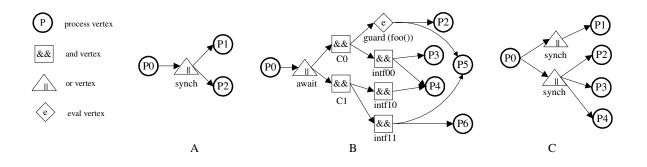

#### Coordination

Processes run concurrently, each at its own pace. The relative speed of processes may arbitrarily change at any time, unless they synchronize with each other using the synchronization primitive called *await*, or if *constraints* are specified in the system. The await statement can

Figure 1.3: An example of MMM specification

be used to make a process wait until some condition holds and establish critical sections that guarantee mutual exclusion among different processes. To limit the behavior of processes, a designer can also specify high-level LTL (Linear Temporal Logic) [59] or LOC (Logic of Constraints) [19] constraints and leave the implementation of these constraints to the detail design stage.

The await statement is used to establish mutually exclusive sections and synchronize processes. It contains one or more statements called *critical sections*, each controlled by a triple (*guard*; *testlist*; *setlist*), where the guard is a Boolean expression, and the testlist and setlist denote sets of interface methods that other processes can call. A critical section is said to be *enabled* if its guard is true, and none of the interface methods in the testlist are being executed at that moment. A critical section may start executing only if it is enabled. In addition, while the critical section is being executed, no interface methods included in

the setlist can begin their executions. Whenever an await is encountered in the execution flow, one and only one of the enabled critical sections is executed. If no critical section is enabled, the execution blocks. If more than one critical sections are enabled, the choice is non-deterministic.

#### Function, Architecture, and Mapping

The function-architecture separation and mapping are natively supported in the Metropolis Meta-Model language. The function and architecture of a system are defined independently at a high level of abstraction. The function is then mapped to the architecture in order to arrive at a given implementation.

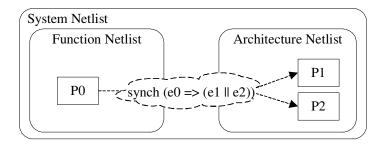

Both the function and architecture of a system are modeled as separate networks of processes communicating through media. In an architectural network, resources are typically modeled with media, services that the architecture can provide are modeled with so called *mapping processes*, and arbitrators among multiple architectural resources are modeled with *quantities*. A third network can be defined to encapsulate the functional and architectural networks and to *relate* the two by synchronizing events between them with *synch* constraints.

Figure 4.6 shows a mapping network *MapNetlist* that correlates the functional network *FuncNetlist* with the architectural network *ArchNetlist*. The functional network includes two processes *p1* and *p2* communicating through media *m1* and *env*. The architectural network contains media *CPU*, *BUS* and *MEM*, and the corresponding mapping processes. The synch constraints are used to synchronize the events from the functional processes and the mapping

Figure 1.4: Function-architecture mapping

processes. Schedulers *OsSched* and *BusArbiter*, which are modeled with quantities, coordinate the architectural resources and provide performance models to the architectural network. During execution, architectural media and mapping processes can request the quantitative annotations from the quantities.

## 1.5 Thesis Overview

In this thesis, we present a complete study of system level verification and analysis techniques based on formal specification of design constraints. The focus is to automate the verification and analysis process at different stages of the design flow. The rest of the thesis is organized as follows. In the next chapter, a complete study of LOC formalism is presented. The syntax, semantics, and verifiability of LOC are discussed in detail. In addition, the verification and analysis algorithms for LOC formulas are proposed. In Chapter 3, we focus on assertion-based simulation verification and analysis for system level designs. We discuss how assertion languages based on mathematical logics such as LOC and LTL are used in simulation verification for both functional and performance design constraints. Furthermore, LOC formulas are shown to be useful in design exploration with performance and power trade-off analysis by automatically generating quantitative distribution analyzers. The techniques are demonstrated with case studies of a network processor architecture design.

A simulation-based deadlock analysis mechanism is presented in Chapter 4. We show that, for certain common design constraints such as deadlock or starvation, a built-in detection and analysis method based on simulation is more efficient to use than general assertion languages or formal methods. The causes of deadlock problems are analyzed, and data structures and algorithms are proposed for simulation time deadlock monitoring and analysis. The experiments are done within the Metropolis framework and used to show the effectiveness of the approach.

In Chapter 5, we propose a formal verification methodology for system level designs. In this approach, an existing software formal verification tool is utilized as the back-end verification engine, and system specifications are automatically translated into lower level verification models. A designer is then allowed to verify formally specified design constraints, and to refine the design or the constraints according to the verification results. In addition, an automatic abstraction propagation technique is proposed to simplify verification models. By implementing this methodology, a verification back-end tool is integrated in the Metropolis framework, and its usefulness and effectiveness are demonstrated through several case studies.

Chapter 6 concludes the thesis and summarizes the contributions of this work.

## Chapter 2

# **Logic of Constraints**

In this chapter, we introduce our quantitative constraint formalism, Logic of Constraints (LOC). LOC is particularly suited for specification and simulation analysis of performance constraints at the transaction level, where only the events observable from the system and their annotations are considered, as will be shown later in this chapter.

## 2.1 Introduction to LOC

The LOC formalism is compatible with a wide range of functional specification formalisms that describe a system as a network of components communicating through fixed interconnections. The observed behavior of the system is usually characterized by sequences of values observed at the interconnections. LOC is a formalism designed to reason about traces from the execution of a system. It consists of all the terms and operators allowed in sentential logic, with additions that make it possible to specify system level quantitative functional and performance constraints without compromising the ease of analysis. LOC can be used to specify many common and useful real-time performance constraints.

• rate, e.g. "*Display*'s are produced every 10 time units":

$$t(Display[i+1]) - t(Display[i]) = 10 , \qquad (2.1)$$

• latency, e.g. "Display is generated no more than 25 time units after Stimuli":

$$t(Display[i]) - t(Stimuli[i]) \le 25 \quad , \tag{2.2}$$

• jitter, e.g. "every *Display* is no more than 4 time units away from the corresponding tick of the real-time clock with period 10":

$$|t(Display[i]) - (i+1) * 10| \le 4$$

, (2.3)

• throughput, e.g. "at least 100 *Display* events will be produced in any period of 1001 time units":

$$t(Display[i+100]) - t(Display[i]) \le 1001$$

, (2.4)

• burstiness, e.g. "no more than 1000 *Display* events will arrive in any period of 9999 time units":

$$t(Display[i+1000]) - t(Display[i]) > 9999$$

. (2.5)

In addition, LOC can also be used to specify quantitative functional constraints such as the data consistency, e.g. "the input data should be the same as the output data":

$$data(input[i]) = data(output[i]) .$$

(2.6)

It should be emphasized that time is only one of the possible annotations. Any value that may be associated with an event (e.g. power, area, data value) can be used as an annotation. In the case of concurrent events, the values of time annotation should be the same. The indices of instances of the same event denote the strict order as they appear in the execution trace. There is no implied relationship between instances of different events. LOC can be used to express relationship between the annotations of the different instances of the same event (e.g. rate), or instances of different events (e.g. latency).

The latency constraint above is truly a latency constraint only if the *Stimuli* and *Display* are kept synchronized. Generally, we will need an additional annotation that denotes which instance of *Display* is "caused" by which instance of the *Stimuli*. If the *cause* annotation is available, the latency constraint can be more accurately written as:

$$t(Display[i]) - t(Stimuli[cause(Display[i])]) \le 25 , \qquad (2.7)$$

and such an LOC formula can easily be analyzed with simulation. However, it is the responsibility of the designer, the program, or the simulator to generate such an annotation.

A constraint formalism is not meaningful unless there exists a clear and efficient path to verification. An efficient simulation-based approach is proposed for analyzing LOC formulas

(see Section 2.4). C++ trace checkers are automatically generated from LOC formulas. The checkers analyze the simulation traces and report any constraint violations. In most cases, the traces are scanned only once and memory usage is very low. The automatic checker generation is parameterized, so it can be customized for fast analysis for specific verification environments (e.g. memory limitation). The choice of C++ for the checkers is a matter of convenience. It allows us to tightly integrate the checkers with the SystemC [7] simulator for runtime monitoring. No major difficulty exists to generate checkers in HDLs for integration with hardware simulators, or in Java for concurrent execution with the software simulators.

A simulation-based approach can only disprove the LOC formula (if a violation is found), but it can never prove it conclusively, as that would require analyzing the design space exhaustively. However, for small but important designs or library modules that will be instantiated many times across different designs, it may be necessary to formally prove the desired properties. Formal verification is more expensive though the designers can be more confident about the result. It should be used only for small but important design modules (e.g. Task Transition Level (TTL) channel [32]), possibly in concert with simulation verification of the entire system. An exact verification algorithm exists for a broad class of LOC formulas (see Section 2.5). However, due to the high complexity of this algorithm, an alternative is provided in this study. We propose a formal verification approach where LOC formulas are translated into verification models in Promela (Spin's modeling language [42]) and LTL formulas. This approach is complete for a restricted subset of LOC. It can also be applied to a wider subset, but results might then be inconclusive, i.e. the verification is only partial. While similar in spirit to the hardware embedded assertion languages, our LOC formalism and simulation verification approach are indeed useful in at least three fundamental aspects. First, Logic of Constraints is designed for specifying all quantitative performance and functional constraints, not just functional ones. This means that one can easily specify requirements on timing or power consumption of the systems being designed, in addition to those on the functional correctness. Second, LOC can be used to specify performance constraints effectively, while many LOC properties cannot be expressed with LTL directly. Third, system level functional and performance constraints written in LOC can be automatically and efficiently synthesized into static checkers, runtime monitors, or formal verification modules.

# 2.2 LOC Syntax and Semantics

Here we give an informal overview of LOC syntax and semantics. Full details are given in Appendix A. The basic blocks of LOC formulas are terms, which can be either:

- constants, or

- integer variable *i* (the only index variable that can appear in an LOC formula), or

- expressions of the form a(e[n]), where a is an annotation name, e is an event name, and *index expression* n is an integer-valued term, or

- combination of simpler terms using usual arithmetic operators.

We interpret a(e[n]) as the value of annotation a of the n-th occurrence of event e. All other terms are interpreted naturally. Terms can be combined using relational operators to create atomic LOC formulas. Finally, LOC formulas are standard Boolean expressions over atomic formulas.

LOC formulas may contain only one index variable, namely *i*. Having only one index variable may seem very restrictive, but so far we have not found a natural constraint that required more than one. In effect, the ability of defining annotations allows one to specify formulas that otherwise require more than one index variable. On the other hand, having only one index variable enables efficient simulation monitoring.

Models of LOC formulas contain a sequence of occurrences for each event name in the formula. Such structures are called *annotated behaviors*. Each occurrence may be annotated with some annotation, but we do not require each annotation appearing in the formula to be defined. This feature is important for our design methodology, where performance requirements are specified early in the process, even though they can be evaluated much later, when many implementation details are set.

Given an annotated behavior, the formula is evaluated for each value of index variable *i*. This is done in quite a standard fashion, except that we need to consider the fact that some terms may not be defined (either because there are only finitely many occurrences of an event, or because an annotation is not defined for an existing event occurrence). To deal with this, the third logical value *undef* is introduced. In general, all operators (including Boolean) return *undef* if one of their operands are *undef*. The only exceptions are conjunction with

*false* (which is *false*), and disjunction with *true* (which is *true*). Finally, the annotated behavior satisfies the formula if it does not evaluate to *false* for any value of i.

# 2.3 Expressiveness of LOC

In this section, we discuss the expressiveness property of LOC especially in its relationship with the well known Linear Temporal Logic (LTL). It should be noted that LTL is defined on the state transition level where any change at the system state is accounted for, while LOC works on a higher abstraction level, in which only the events observable from the system and their annotations are considered. This apparent difference, however, is just a technicality, because it is not difficult to hide state transitions so that LTL and LOC are defined over the same kind of objects.

Through several examples and claims, it is concluded that LOC and LTL are incomparable and have different domains of expressiveness.

#### Claim 1 There are LOC formulas that can be expressed with LTL.

Since both LOC and LTL contain basic Boolean expressions, a subset of LOC constraints that specify simple global Boolean conditions can be expressed in LTL also. For example, the constraint, "the annotation *data* of the event *Display* is always greater than 100", is expressed in LOC as:

$$data(Display[i]) > 100 \quad . \tag{2.8}$$

If we use a variable *Display\_data* to store the value of *data* in the design, and use a flag *Display\_occur* to indicate that an instance of the event *Display* occurs, this constraint can be easily expressed in LTL as:

$$G(Display\_occur \Longrightarrow (Display\_data > 100))$$

. (2.9)

#### Claim 2 There are LOC formulas that cannot be expressed with LTL.

Many quantitative constraints that can be easily expressed by LOC are not suitable for LTL. Specifically, when more than one events need to be compared in the same constraint (e.g. the latency constraint), LTL is not expressive enough to be used. For example, the data consistency constraint:

$$data(input[i]) = data(output[i])$$

(2.10)

requires comparing each instance of *output* with the instance of *input* with the same instance index. After the *n*-th *input* occurs, it is unknown when the *n*-th *output* will occur, i.e. the number of *input* instances that may occur before the *n*-th instance of *output* is arbitrarily large. Therefore, this constraint cannot be modeled by a finite-state system, and it is impossible to express it using any formalism based on  $\omega$ -regular languages, such as LTL or PSL.

It is interesting to note that there are simple LOC formulas that cannot be expressed by LTL even though they are  $\omega$ -regular. For example, the property "the value of event A on every even occurrence is 1", can be expressed by LOC formula data(A[2i]) = 1, as well as with a simple two-state automaton, but it is well known that it cannot be expressed by LTL [64].

To show that some LTL formulas cannot be expressed in LOC, we first recall that any property can be expressed as a conjunction of a *safety* and a *liveness* property. Safety properties are those which can always be shown violated by a finite trace. For example, any execution that does not satisfy the property "the value of A is never 1" must have a finite prefix which ends with the value of A being 1. On the other hand, liveness properties can never be violated by a finite trace. For example, the property "for every request there is a response" can never be violated by a finite trace because there is always a chance that a response may come some time in the future. <sup>1</sup>

#### Claim 3 LOC can express only safety properties.

Indeed, if a trace does not satisfy an LOC formula, then there must exist an i for which the formula is false. We can evaluate all index expressions for that value of i. Since there can only be finitely many of these expressions, there must exist some point in the execution such that, for that particular i, the formula does not refer to any event occurrence beyond that point. Clearly, the execution prefix up to that point is sufficient to disprove the property.

On the other hand, LTL is capable of expressing some liveness properties, for example GF(A), i.e. "A occurs infinitely often".

*Conclusion:* From claims (2) and (3), we conclude that LOC and LTL are incomparable.

<sup>&</sup>lt;sup>1</sup>To disprove a liveness property, we need to show that the system can enter an infinite cycle in which there are unfulfilled requests.

Generally, LOC is designed for the specification of quantitative performance and functional constraints at the transaction level where system events and their annotations are considered. Because of the use of index variable *i*, LOC is beyond the finite automata domain. On the other hand, LTL is suitable for the specification of functional constraints, and can effectively express the temporal patterns for system state transitions. Because of this difference, LOC can express important properties that cannot be expressed with LTL, on which the traditional property specification languages are based.

In fact, it has been shown that LOC is incomparable with any formalism capable of expressing  $\omega$ -regular properties. From the theoretical point of view, it may be interesting to establish whether LOC can express all regular properties, i.e. whether LOC is more expressive than WS1S. However, for the methodology proposed here, that question is hardly relevant, because LOC is proposed as a complement to and not a replacement for existing property languages capable of expressing regular properties.

# 2.4 Checking LOC Formulas with Simulation

In simulation verification, we automatically generate simulation trace checkers from LOC formulas. In the LOC checker, we use a linear-time algorithm to check the simulation trace, which could be infinite, and see if an LOC formula can be satisfied for all possible values of index i. Although the algorithm is linear in time, memory space usage is dependent on the formula heavily. To reduce the running time, we try to scan the whole trace only once

and store the annotation information that is expected to be useful in the future. Therefore, a memory recycling procedure has to be invoked frequently to release unnecessary memory space to obtain space efficiency.

The algorithm of LOC checking progresses based on the index variable *i*. Each LOC formula instance is checked sequentially with the value of *i* being 1, 2, ... etc. A formula instance is a formula with *i* evaluated to some fixed positive integer value, e.g. Display[30] - Display[29] = 10 is the 29th instance of the formula (2.1). Starting with *i* equal to 1, the LOC checker scans the trace sequentially. If any relevant data is read in, the checker stores it into a queue and checks the formula in the following manner (Algorithm 1).

| Algorithm 1 Check an LOC formula.        |

|------------------------------------------|

| procedure CHECK_LOC_FORMULA()            |

| while can evaluate formula instance i do |

| evaluate formula instance i;             |

| i++;                                     |

| memory recycling                         |

| end while                                |

| end procedure                            |

The time complexity of the algorithm is linear in the size of the trace since evaluating a particular Boolean expression takes constant time. The memory usage, however, may become prohibitively high if we try to keep the entire trace in the queue for analysis. As the trace file is scanned in, the checker attempts to store only the useful annotations, and in addition, to evaluate as many formula instances as possible, and to remove from the memory parts of the annotations that are no longer needed (memory recycling).

For many LOC formulas (e.g. constraints (2.1), (2.3) - (2.5) in Section 2.1), the algorithm

uses a fixed amount of memory no matter how long the traces are (see Table 2.1).<sup>2</sup> Memory efficiency of the algorithm comes from being able to free stored annotations as their associated formula instances are evaluated. This ability is directly related to the choice made in designing LOC. From an LOC formula, we can conservatively identify what annotation data will not be useful anymore once all the formula instances with indices less than a certain number are all evaluated. For example, consider an LOC formula:

$$t(Display[i+10]) - t(Stimuli[i+5]) < 300$$

, (2.11)

and let the current value of i be 100. Because the value of i increases monotonically, we know that event *Display*'s annotation t with index less than 111 and event *Stimuli*'s annotation twith index less than 106 will not be useful in the future, and their memory space can be released safely. Each time an LOC formula is evaluated with a new value of i, the memory recycling procedure is invoked, which ensures minimum memory usage.

As described in Section 2.2, the LOC semantics allows us to evaluate an LOC formula even if some of its expressions are not defined. When an annotation with a particular index value is not yet available from the trace, or when the index has an invalid value (e.g. negative value), the Boolean expression that contains this annotation is evaluated to *undef*. The entire LOC formula could then be evaluated according to the standard three-value logic [54]

<sup>&</sup>lt;sup>2</sup>The verification of the constraint (2.2) may also have constant memory usage if the given trace has a certain regular structure.

evaluation. For example, given the following LOC formula:

$$t(A[i+10]) > 100 \lor t(B[i-5]) < 300$$

, (2.12)

let the current value of *i* be 10. If we know, from the trace, that the value of t(A[20]) is 200, the formula can already be evaluated to *true* even if the value of t(B[5]) is still not available at this point in the simulation (trace). Thus LOC formula instances can be evaluated as soon as possible, which further minimizes the memory usage. Also, if we let the current value of *i* be 4, -1 is then an invalid index for annotation *t* of event *B*. The expression t(B[-1]) < 300is evaluated to *undef*, and the whole formula can be evaluated to *true* if the evaluation of t(A[14]) > 100 is *true*, or *undef* otherwise.

#### 2.4.1 Runtime Monitoring

The static trace checking technique, as described above, assumes that a simulation trace is first generated and the subsequent LOC checking parses the trace and looks for constraint violation. How the trace is generated is immaterial as long as the format is correctly specified in the definition file. The trace file for a realistic design, however, can frequently occupy several gigabytes of disk space. It may be desirable to compile the checker as a runtime monitor to run concurrently with the simulator through a Unix pipe. Alternatively, the checker can be compiled into the compiled-code simulator for higher efficiency and tighter integration. As an example of such tight integration, the checker generator has been extended to gener-

ate LOC checkers as SystemC modules [7]. During the simulation, other SystemC modules (representing the design) can pass the events and annotations directly to the monitor modules through channels. A case study of this approach is reported in Section 2.4.3. Runtime monitoring is more efficient than static checking, but then obviously the simulation need to be repeated if some new formula need to be checked later. Furthermore, the trace is no longer kept so any debugging has to rely solely on the error report.

#### 2.4.2 Dealing with Memory Limitation

Despite the memory efficiency for most LOC formulas, some LOC formulas may require high memory usage that the verification environment cannot support. To deal with the case of preset memory limitation, another extension has been added to the checker generator. Generally, the checker tries to read the trace and store the annotations only once. However, if the preset memory limit has been reached, it stops storing the annotation and instead, scans the rest of the trace looking for needed events and annotations for evaluating the current formula instance (with the current value of *i*). After freeing some memory space, the algorithm resumes storing annotations and reading the trace again from the same location. The analysis time can certainly be impacted (see the case study in Section 2.4.3) and may no longer be of linear complexity. However, the verification can continue and the constraint violations can be checked under the memory limitation of the verification environment.

#### 2.4.3 A Case Study of FIR Filter

We use a register transfer level model of a *finite impulse response (FIR)* filter written in SystemC to show how LOC can be used to efficiently check real time performance constraints. Figure 2.1 shows a 16 tap FIR filter that reads in samples when the input is valid and writes out the result when output is ready. The filter design is divided into a control FSM and a data path. The test bench feeds sampled data of arbitrary length, and the output is displayed with the simulator.

Figure 2.1: A FIR design and its simulation trace

We use our automatic trace checker generator to verify the properties specified in constraints (2.1) - (2.5) (in Section 2.1). The same trace files are used for all the analyses, and each constraint is checked one at a time. The time and maximum memory usage are shown in Table 2.1. We can see that the time required for analysis grows linearly with the size of the trace file, and the maximum memory requirement is formula dependent but stays fairly constant. Using LOC for common real-time constraint verification is indeed very efficient.

Given the large file size, runtime monitoring (see Section 2.4.1) may reduce the total verification time (simulation and checking) since no trace file needs to be actually generated. For

| Lines of Trace |         | $10^{5}$ | $10^{6}$ | $10^{7}$ | $10^{8}$ |

|----------------|---------|----------|----------|----------|----------|

| C1             | Time(s) | 1        | 8        | 89       | 794      |

|                | Memory  | 28B      | 28B      | 28B      | 28B      |

| C2             | Time(s) | 1        | 12       | 120      | 1229     |

|                | Memory  | 28B      | 28B      | 28B      | 28B      |

| C3             | Time(s) | 1        | 7        | 80       | 799      |

|                | Memory  | 24B      | 24B      | 24B      | 24B      |

| C4             | Time(s) | 1        | 7        | 77       | 803      |

|                | Memory  | 0.4KB    | 0.4KB    | 0.4KB    | 0.4KB    |

| C5             | Time(s) | 1        | 7        | 79       | 810      |

|                | Memory  | 4KB      | 4KB      | 4KB      | 4KB      |

Table 2.1: Costs of checking formulas (2.1)-(2.5) on FIR

the latency constraint (the formula (2.2)), we implement the checker as a SystemC module, and the simulation trace is no longer written to a file but passed to the monitoring module directly. Table 2.2 lists CPU times used for simulation, trace checking, and simulation with runtime monitoring for the formula (2.2) on the traces of different lengths. For the trace size of 100 million lines, the static checking approach requires 1404 seconds of simulation time and 1229 seconds of checking time for a total of 2633 seconds. Runtime monitoring requires only 1420 seconds for both simulation and monitoring. If a simulation trace is really long (e.g. hundreds of gigabytes), runtime monitoring can significantly save CPU time compared to off-line trace checking.

Table 2.2: Time usage of simulation and checking formula (2.2) on FIR

| Lines of Trace                        | $10^{5}$ | $10^{6}$ | $10^{7}$ | $10^{8}$ |

|---------------------------------------|----------|----------|----------|----------|

| Simulation w/o Runtime Monitoring (s) | 1        | 14       | 148      | 1404     |

| Static Trace Checking Only (s)        | 1        | 12       | 120      | 1229     |

| Simulation w/ Runtime Monitoring (s)  | 2        | 14       | 145      | 1420     |

We also verify constraint (2.7) to illustrate verification with memory limitation since this constraint is particularly expensive to check in terms of memory usage. Table 2.3 shows that the simulation time grows linearly with the size of the trace file. However, due to the use of an annotation in an index expression, memory can no longer be recycled and we see that it also grows linearly with the size of the trace file. Indeed, since we will not know what annotation will be needed in the future, we can never remove any information from the queue. If the memory is a limiting factor in the simulation environment, the analysis speed must be sacrificed to allow the verification to continue, as discussed in Section 2.4.2. The result is shown in Table 2.3 where the memory usage is limited to 50KB. We see that the analysis takes more time when the memory limit has been reached. Information about trace pattern can be used to dramatically reduce the running time under memory constraints. Aggressive memory minimization techniques and data structures can also be used to further reduce time and memory requirements. For most LOC formulas and simulation traces, however, the memory space can be recycled and the memory requirements are small.

| Lines of Tra | 2       | 3  | 4  | 5   |      |

|--------------|---------|----|----|-----|------|

| Unlimited    | Time(s) | <1 | <1 | <1  | 1    |

| Memory       | Mem(KB) | 40 | 60 | 80  | 100  |

| Mem Limit    | Time(s) | <1 | 61 | 656 | 1869 |

| (50KB)       | Mem(KB) | 40 | 50 | 50  | 50   |

Table 2.3: Costs of checking constraint (2.7) on FIR

## **2.5** Formal Verification of LOC Formulas

Although our trace analysis enables efficient verification of LOC formulas in a simulation environment, formal verification may still be valuable and sometimes even necessary. We propose to apply formal verification to small designs that are re-used many times, such as library modules. Because they are small, formal verification is practically possible. On the other hand, they are intended to be used in many environment, some of which will be designed long after the module itself is designed and verified. Therefore, it is hard to imagine all simulation scenarios that need to be verified. It is better to characterize the modules with a set of constraints that it satisfies. This will not only increase the confidence in the correctness, but these constraints can be used as a precise specification of a design's behavior as well. The lack of such a specification is a major source of design errors, because informal specifications of library modules are often ambiguous and misunderstood.

Unfortunately, it is undecidable whether a system satisfies an LOC formula, even if some strong restrictions are placed on the system specification and the formula (see Section 2.6). On the positive side, for a significant subset of LOC, it is possible to decide whether a finite-state system satisfies an LOC formula. The decision procedure is based on constructing a formula of Presburger arithmetic that is satisfied if and only if the formula is violated by some behavior of the system. The LOC subset that can be verified in this way includes all formulas described in Section 2.1, except the latency constraint (2.7).

Manipulating Presburger formulas is very expensive in practice, so we propose an alter-

native formal verification approach based on existing finite-state model checking tools. Our approach represents a complete verification procedure for a subset of LOC that defines  $\omega$ -regular properties. We will show in the next section that rate (2.1), throughput (2.4), and burstiness (2.5) belong to this subset, but other formulas in Section 2.1 do not. The proposed approach may still be applied to these formulas, but the procedure is incomplete in this case, because it can terminate with an inconclusive result.

The simulation approach described in Section 2.4 suggests our formal verification approach. A trace checker can be interpreted as an automaton accepting executions. We could thus use existing model-checking tools to verify that each execution of the system is accepted by the trace checker. In the example shown in this chapter, the translation was manual. However, there is no technical difficulty in automatically generating such descriptions in a language understood by a model checking tool through modifying our trace checker generator.

The only significant difference between a simulation trace checker and an automaton description suitable for model checking is that the former can rely on dynamic memory allocation to store trace data that may be needed, while the latter must have all memory space statically allocated. Unfortunately, as we have shown in Section 2.3, for some LOC formulas it is not possible to determine memory requirements *a priori*. Our approach is to fix the memory size anyway and to designate special states where checking the formula would require allocating additional memory, but none is available. Such a state may or may not be reached during the reachability analysis. If it is, the result of the formula verification is inconclusive. More precisely, the verification of an LOC formula can have one of three outcomes:

- a counter-example is found showing that the system does not satisfy the constraint,

- the constraint is satisfied, all reachable state are searched without finding a counterexample, or reaching a state where memory is exhausted,

- inconclusive, analysis finds no counter-examples, but states where memory is exhausted are reachable.

For example, the latency constraint:

$$t(Display[i]) - t(Stimuli[i]) \le 25 \tag{2.13}$$

cannot be modeled by any finite automata because there can be arbitrarily many occurrences of *Stimuli* before x-th occurrence of *Display* (intuitively, we assume that Display[x] always occurs after *Stimuli*[x]). However, if we limit the number of stored time stamps of *Stimuli* to, say, 50, then we can simultaneously check the following two constraints:

- **P1:** There are never more than 50 occurrences of *Stimuli* between *x*-th occurrences of *Stimuli* and *Display*.

- **P2:** If **P1** holds, then (2.13) holds.

Obviously, if **P1** and **P2** both hold, then so does (2.13), and if **P2** is *false*, so is (2.13). However, if **P2** holds, but **P1** does not, the result is inconclusive.

To specify **P1** and **P2**, assume that the trace checker keeps 51 most recent time stamps for Stimuli and Display in arrays  $Display_t$  and  $Stimuli_t$  such that x-th time stamp is stored at position (x mod 51) of the array. Also assume that variable *Display\_i* and *Stimuli\_i* (which take values from 0 to 50) keep the index of the most recent time stamps in the arrays. Finally, assume that binary variables *Display\_occur* and *Stimuli\_occur* are *true* when *Display* and *Stimuli* occur, respectively, and that integer variable *diff* counts the difference between the numbers of occurrences of the *Stimuli* and *Display* events, i.e. it is initialized to 0, incremented on each *Stimuli\_occur*, and decremented on each *Display\_occur*. Then, **P1** can be specified with the following state predicate:

$$diff \le 51 \quad . \tag{2.14}$$

Constraint (2.13) can be expressed as follows:

$$Display\_occur \implies Display\_t[Display\_i] - Stimuli\_t[Display\_i] \le 25$$

, (2.15)

and finally P2 can be expressed as follows:

$$Assumption (2.14) \Longrightarrow Formula (2.15) . \tag{2.16}$$

# 2.6 Complexity of Verifying LOC Formulas

In this section, we address the following fundamental question: How hard is it to check if a system satisfies an LOC formula? This question has many versions, depending on how the

system is represented, and what subset of LOC formulas is being considered. We present answers for several versions. Some versions of the problem are undecidable, and some are decidable, but with very complex algorithms. These "negative" results are used to justify the development of efficient algorithms which may not always give the full answer. These algorithms, based either on simulation, or partial formal verification, are described in previous sections.

In the most general case, systems are represented by arbitrary programs, and annotations can be of any type. This case is clearly expressive enough to encode the halting problem [44], so checking LOC formulas is undecidable in this case.

The first restriction we consider is to limit system specification to a *infinitely-valued* finite-state system, where the number of states of a system is finite, but value domains of annotations can be infinite. Unfortunately, this case is also undecidable. To show this we can encode two counter machines using a finite-state system, two integer annotations to represent counters, and an LOC formula to ensure that counters are incremented or decremented as necessary.

The next restriction we consider are so-called *finitely-valued* finite-state systems, where annotations and event values are required to be finitely valued. With regards to annotation specification, three cases will be considered:

(1) annotations completely undefined,

- (2) annotation must satisfy certain axioms, expressed by an LOC formula,

- (3) annotations defined by a finite state system.

The third case is typical of later design stages. At that point annotations can be considered as part of event values, so we will not study it separately.

The first case is typical at the beginning of the design process, where constraints on annotations are stated, but nothing is yet known about their actual values. At that point, annotations are uninterpreted functions, but they still have to satisfy constraints of equalities. For example, the formula  $\overline{f(e[3i])} = f(e[i+2])$  is not satisfied by any behavior in which e occurs at least 3 times.

We consider the second case because, even if the values of annotations are not known, some constraints, captured by axioms, may be. Consider, for example, time annotations. All possible timing annotations share certain constraints, e.g. time can never decrease. Just from these basic constraints of time, we could deduce some system constraints, which are then valid for any timing. Therefore, it is useful to be able to express constraints that all annotations of certain type must have. Specifying axioms could be done in many ways. For example, an extended version of LOC is used for this purpose in Metropolis [18]. However, the following results state that checking an LOC formula is undecidable even if annotation axioms are restricted to the basic LOC.

**Theorem 1** It is undecidable whether a finitely-valued finite-state system with LOC axioms satisfies an LOC formula with a single event indexed by expression *i*.

As usual, the proof proceeds by reducing a known undecidable problem to LOC checking. The details are given in Appendix B. At first glance, it may appear that checking an LOC formula  $\phi$  for a finite state system with annotation axioms  $\alpha$  may be reduced to checking that the system satisfies implication of  $\phi$  by  $\alpha$  without any axioms. Unfortunately, this approach does not work, and to see why we will for a moment make quantification over *i* appear explicitly in the syntax. Thus, the axioms can be written as  $\forall i : \alpha$ , and the formula can be written as  $\forall i : \phi$ . Solving the problem requires checking ( $\forall i : \alpha$ ) $\Longrightarrow$ ( $\forall i : \phi$ ), but LOC can only express  $\forall i : (\alpha \Longrightarrow \phi)$ , which is not the same. In fact, this seemingly minor restriction makes the problem decidable, as stated by Theorem 2.

We now turn our attention to the case without axioms, where annotations are either completely unconstrained or folded into event values.

**Theorem 2** It is decidable whether a finitely-valued finite-state system without annotation axioms satisfies an LOC formula, in which all index expressions are of the form ai + b, where a and b are integer constants, and variable i appears only in such expressions and linear inequalities.

The proof consists of a decision algorithm. To describe the algorithm, we need some notation. An *event expression* is an LOC term of the form  $val(e[\tau])$ , or of the form  $f(e[\tau])$ , where  $\tau$  is an integer-valued term, e is an event name, and f is an annotation. Note that conditions in Theorem 2 restrict  $\tau$  to be a linear expression, i.e. it must be of the form ai + b, where a and b are constants. The *value domain* of an event expression is the set of values it can take, i.e. it is the value domain of e if the expression is of the form  $val(e[\tau])$ , and it is the value domain of f if the expression is of the form  $f(e[\tau])$ . Given an LOC formula  $\phi$ , we use  $\mathcal{E}_{\phi}$  to denote the set of event expressions appearing in it. An *interpretation* of a set of event expressions is a function that assigns to each expression in the set a value from its value domain. Since Theorem 2 requires the system to be finitelyvalued, there can be only finitely many distinct interpretations of  $\mathcal{E}_{\phi}$ . Given an LOC formula  $\phi$ , and an interpretation I of  $\mathcal{E}_{\phi}$ , we use  $\phi_I$  to denote the formula obtained from  $\phi$  by replacing each event expression  $\epsilon$  in  $\phi$  by the value  $I(\epsilon)$ . We call  $\phi_I$  an interpretation of  $\phi$ . Note that because  $\phi_I$  contains no event expressions,  $\mathcal{V}^n_{(\beta,A)}[\![\phi_I]\!]$  actually depends only on n and must be either *true* or *false*.