# The Design and Implementation of Compression Techniques for Profile Guided Compilation

by

Youtao Zhang

A Dissertation Submitted to the Faculty of the

DEPARTMENT OF COMPUTER SCIENCE

In Partial Fulfillment of the Requirements For the Degree of

DOCTOR OF PHILOSOPHY

In the Graduate College THE UNIVERSITY OF ARIZONA

$2 \ 0 \ 0 \ 2$

Get the official approval page from the Graduate College *before* your final defense.

## STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced degree at The University of Arizona and is deposited in the University Library to be made available to borrowers under rules of the Library.

Brief quotations from this dissertation are allowable without special permission, provided that accurate acknowledgment of source is made. Requests for permission for extended quotation from or reproduction of this manuscript in whole or in part may be granted by the head of the major department or the Dean of the Graduate College when in his or her judgment the proposed use of the material is in the interests of scholarship. In all other instances, however, permission must be obtained from the author.

SIGNED:

To my parents, Yurong Zhang and Xuexia Yuan. To my wife, Jun Yang.

### ACKNOWLEDGEMENTS

My special thanks are for my advisor Dr. Rajiv Gupta. I thank him for his guidance in selecting research topics and refining approaches. During the years in pursuing my degree, he always encouraged me and took great patience to help me in writing papers and giving presentations. It is a privilege to have him as my advisor.

I feel grateful for my wife, Jun Yang. She gave me huge support in these years while she had to work hard on her Ph.D. dissertation research. I wish her a successful career.

I would also like to take this chance to thank other members in my committee Dr. Peter Downey and Dr. Samuya Debray. I also thank Xiangyu Zhang and all the people who helped me over the years.

# TABLE OF CONTENTS

| List of Figures                                          | . 9  |

|----------------------------------------------------------|------|

| LIST OF TABLES                                           | . 11 |

| Abstract                                                 | . 12 |

| Chapter 1. Introduction                                  | . 13 |

| 1.1. Program profiling and profile guided optimizations  |      |

| 1.2. Overview of the research                            |      |

| 1.2.1. Representation of profiling data                  |      |

| 1.2.2. Profiling for value redundancy detection          |      |

| 1.3. Organization                                        |      |

| Chapter 2. Background                                    | . 19 |

| 2.1. Program profiles                                    |      |

| $2.1.1.$ Type of profiles $\ldots$                       |      |

| 2.1.2. Collecting profiles                               |      |

| 2.2. Profile guided optimizations                        |      |

| 2.2.1. Profile guided control flow related optimizations |      |

| 2.2.2. Profile guided value optimizations                |      |

| 2.2.3. Profile guided memory optimizations               |      |

| CHAPTER 3. COMPRESSING THE CONTROL FLOW TRACE            | . 30 |

| 3.1. TWPP: Timestamped whole program path                | . 31 |

| 3.2. Implementation and experiments                      |      |

| 3.3. Conclusion                                          |      |

| CHAPTER 4. COMPRESSING THE MEMORY DEPENDENCE TRACE       | . 46 |

| 4.1. TWPP+: TWPP with memory dependence edges            | . 48 |

| 4.2. Implementation and experiments                      |      |

| 4.2.1. Compression results using TWPP+                   |      |

| 4.2.2. Average scan length                               |      |

| 4.3. Related work                                        |      |

| 4.4. Conclusion                                          |      |

| CHAPTER 5. APPLICATIONS OF TWPP+                         | . 60 |

| 5.1. Exploring LOAD/STORE redundancy                     | . 61 |

| 5.1.1. Identifying a redundant LOAD/STORE instruction    |      |

| 5.1.2. Identifying redundant loads from TWPP+            |      |

# TABLE OF CONTENTS—Continued

|       | 5.1.3. Identifying redundant stores from $TWPP + \ldots \dots \ldots$ | 65  |

|-------|-----------------------------------------------------------------------|-----|

|       | 5.1.4. Experimental results                                           | 66  |

| 5.2.  | Frequency of data flow facts                                          | 69  |

|       | 5.2.1. Timestamp annotated dynamic CFG                                | 70  |

|       | 5.2.2. Demand-driven analysis                                         | 71  |

| 5.3.  | Dynamic program slicing with TWPP                                     | 75  |

|       | 5.3.1. Precise dynamic slicing with TWPP+                             | 75  |

|       | 5.3.2. Approximate dynamic slicing with TWPP+                         | 80  |

| 5.4.  | Conclusion                                                            | 81  |

| Снарт | er 6. Profiling dynamically allocated data objects                    | 82  |

| 6.1.  | Type based profiling                                                  | 84  |

| 6.2.  | Experimental framework                                                | 85  |

| 6.3.  |                                                                       | 88  |

| 6.4.  | Choosing the compression scheme                                       | 89  |

|       | 6.4.1. Potential savings in space due to redundancy removal           | 91  |

|       | 6.4.2. Potential costs of redundancy removal                          | 92  |

| 6.5.  | 0 1                                                                   | 96  |

| 6.6.  | Conclusion                                                            | 98  |

| Снарт | er 7. Profile-guided data compression transformations                 | 100 |

| 7.1.  | Data compression transformations                                      | 101 |

| 7.2.  | 1 1                                                                   | 104 |

| 7.3.  | 1 11                                                                  | 109 |

| 7.4.  | 1 1                                                                   | 111 |

|       | 7.4.1. Experimental setup                                             | 111 |

|       | 7.4.2. Impact on storage needs                                        | 112 |

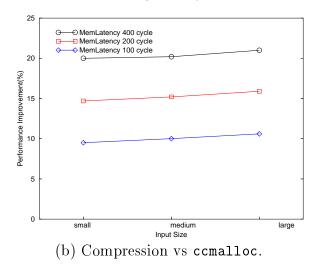

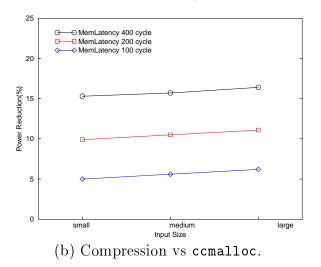

|       | 7.4.3. Impact on execution time                                       | 116 |

|       | 7.4.4. Impact on power consumption                                    | 117 |

|       | 7.4.5. Impact on cache performance                                    | 117 |

| 7.5.  | Related work                                                          | 120 |

| 7.6.  | Conclusion                                                            | 121 |

| Снарт | ER 8. EXPLOITING VALUE REPRESENTATION REDUNDANCY IN HARD-             |     |

| WAF   |                                                                       | 123 |

| 8.1.  | Compression enabled partial cache line prefetching                    | 125 |

|       | 8.1.1. Value representation in hardware                               | 125 |

|       | 8.1.2. Partial cache line prefetching                                 | 126 |

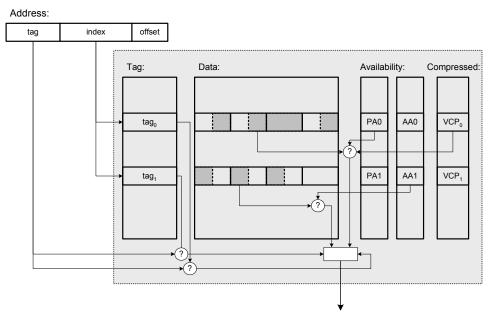

|       | 8.1.3. Cache design details                                           | 129 |

|       | 8.1.4. Dynamic value representation                                   | 131 |

|       |                                                                       |     |

# TABLE OF CONTENTS—Continued

|        | 8.1.5. | Cache access policy        | 132 |

|--------|--------|----------------------------|-----|

| 8.2.   | Implen | nentation and experiments  | 133 |

|        | 8.2.1. | Experimental setup         | 133 |

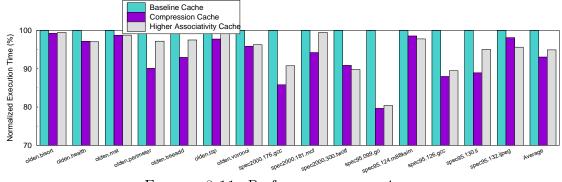

|        | 8.2.2. | Overall performance        | 133 |

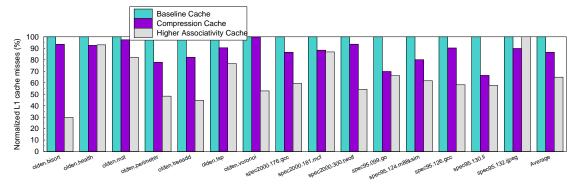

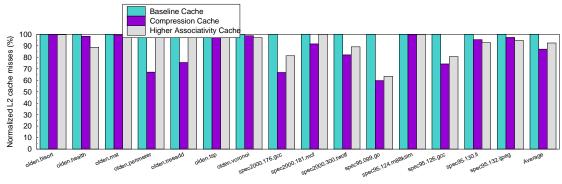

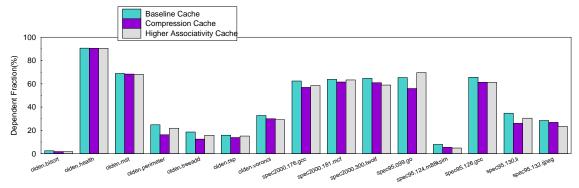

|        | 8.2.3. | Cache miss comparison      | 134 |

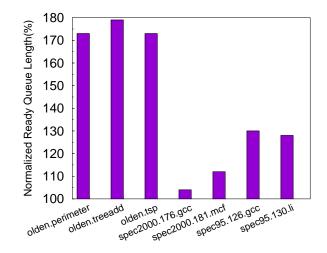

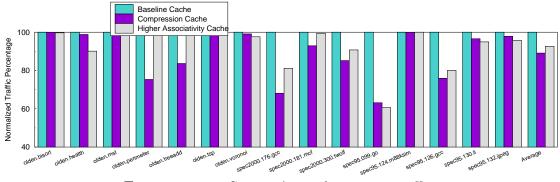

|        | 8.2.4. | Memory traffic             | 138 |

| 8.3.   | Relate | d work                     | 139 |

| 8.4.   | Conclu | asion                      | 140 |

| Снарт  | er 9.  | CONCLUSION AND FUTURE WORK | 141 |

| 9.1.   | Summ   | ary of contributions       | 141 |

| 9.2.   | Future | e work                     | 144 |

| Referi | ENCES  |                            | 146 |

# LIST OF FIGURES

| FIGURE 1.1.<br>FIGURE 1.2.<br>FIGURE 1.3.                                                                                                           | Overview of profile-guided compilation                                                                                                                                                                                                                                                                                        | $13 \\ 17 \\ 17 \\ 17$                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| FIGURE 2.1.<br>FIGURE 2.2.<br>FIGURE 2.3.                                                                                                           | Value profiles                                                                                                                                                                                                                                                                                                                | 21<br>23<br>29                                     |

| Figure 3.1.<br>Figure 3.2.<br>Figure 3.3.<br>Figure 3.4.<br>Figure 3.5.<br>Figure 3.6.<br>Figure 3.7.<br>Figure 3.8.<br>Figure 3.9.<br>Figure 3.10. | An uncompacted control flow trace                                                                                                                                                                                                                                                                                             | 32<br>33<br>35<br>35<br>37<br>38<br>39<br>42<br>43 |

| FIGURE 4.1.<br>FIGURE 4.2.<br>FIGURE 4.3.<br>FIGURE 4.4.<br>FIGURE 4.5.<br>FIGURE 4.6.                                                              | Importance of data flow information.An example of a memory dependence trace.Eliminating explicit addresses.Creating memory access dictionary.Representation for timestamped memory dependence edges.Compressing each subsequence using Sequitur.                                                                              | 46<br>48<br>49<br>50<br>51<br>52                   |

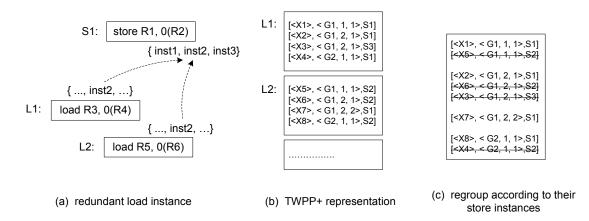

| Figure 5.1.<br>Figure 5.2.<br>Figure 5.3.<br>Figure 5.4.<br>Figure 5.5.<br>Figure 5.6.<br>Figure 5.7.<br>Figure 5.8.<br>Figure 5.9.                 | Redundant LOAD/STORE instructionsDetermining a redundant loadDetermining all redundant stores from TWPP+Ideal LOAD redundancy.Ideal STORE redundancy.Dynamic slicing examplePrecise dynamic slicing algorithm with TWPP+Implementing A&H's dynamic slicing algorithm 3Implementing A&H's imprecise dynamic slicing algorithms | 62<br>65<br>66<br>67<br>68<br>76<br>77<br>79<br>80 |

| FIGURE 6.1.<br>FIGURE 6.2.<br>FIGURE 6.3.<br>FIGURE 6.4.<br>FIGURE 6.5.                                                                             | Type based profiling framework                                                                                                                                                                                                                                                                                                | 85<br>90<br>91<br>92<br>94                         |

# LIST OF FIGURES—Continued

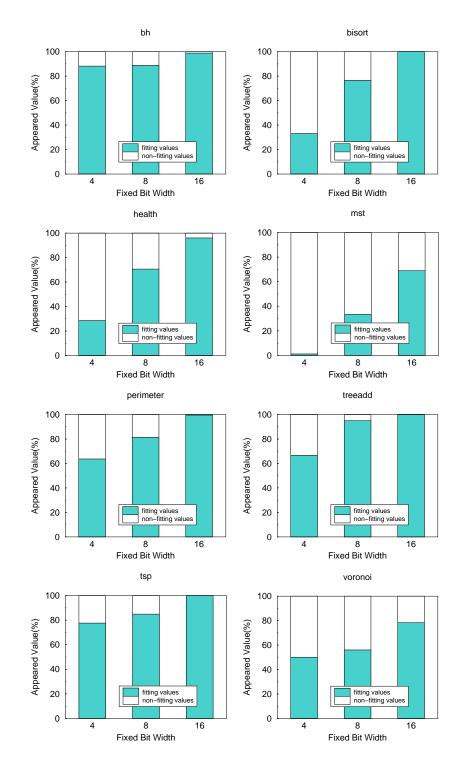

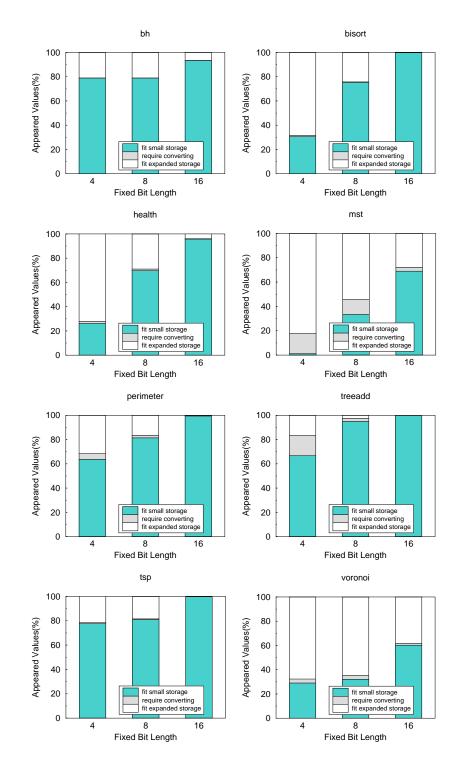

| FIGURE 6.6.     | Distribution of values with fixed storage           | 95  |

|-----------------|-----------------------------------------------------|-----|

| FIGURE 6.7.     | Deciding the time for compression                   | 97  |

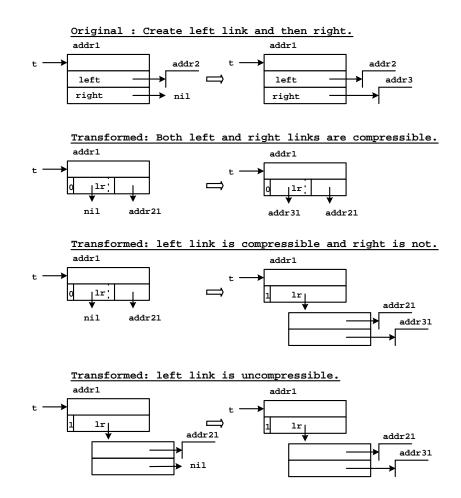

| Figure 7.1.     | Dealing with incompressible data                    | 104 |

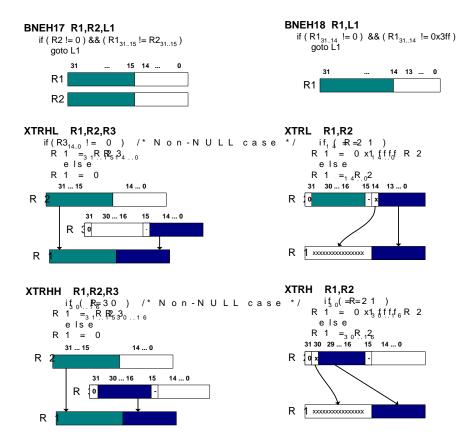

| FIGURE 7.2.     | DCX instructions.                                   | 106 |

| FIGURE 7.3.     | An example.                                         | 108 |

| FIGURE 7.4.     | Experimental setup.                                 | 112 |

| FIGURE 7.5.     | Applied transformations                             | 113 |

| FIGURE 7.6.     | Impact on storage.                                  | 114 |

| FIGURE 7.7.     | Impact on object code size.                         | 115 |

| FIGURE 7.8.     | Change in execution time due to data compression    | 118 |

| FIGURE 7.9.     | Impact on power consumption                         | 119 |

| FIGURE 7.10.    | Change in cache misses - configuration 1            | 120 |

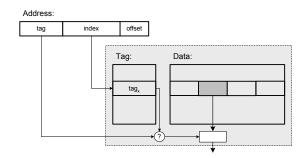

| FIGURE 8.1.     | Memory address and cache access.                    | 123 |

| FIGURE 8.2.     | Values encountered during program execution         | 124 |

| FIGURE 8.3.     | Representing a 32-bit value with fewer than 32 bits | 125 |

| FIGURE 8.4.     | Representing compressed values in hardware          | 126 |

| FIGURE 8.5.     | Compressing data in the cache to hold more words    | 127 |

| FIGURE 8.6.     | Dynamic data structure declaration.                 | 128 |

| FIGURE 8.7.     | Cache layout before and after compression.          | 129 |

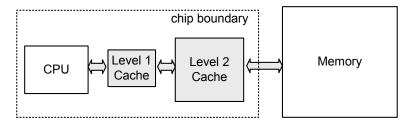

| FIGURE 8.8.     | Two level compression cache design.                 | 129 |

| FIGURE 8.9.     | Compression cache                                   | 131 |

|                 | Baseline experimental setup                         | 133 |

| Figure $8.11$ . | Performance comparison.                             | 134 |

| Figure $8.12$ . | Comparison of L1 cache misses                       | 135 |

| Figure $8.13$ . | Comparison of L2 cache misses                       | 135 |

| Figure $8.14$ . | The estimation of cache miss importance             | 137 |

|                 | Average miss cycle ready queue length               | 138 |

| FIGURE 8.16.    | Comparison of memory traffic.                       | 139 |

# LIST OF TABLES

| Sample input traces used in the experiments                    | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WPP trace compaction due to various transformations            | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Overall compaction factor.                                     | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Extraction times for a single function                         | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Compacted trace sizes and extraction times.                    | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Memory trace characteristics                                   | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Distribution of load and store accesses.                       | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Dictionary size for memory access points                       | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Distribution of static load and store points                   | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Dynamic behavior and removed edges                             | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Compression results using Sequitur and TWPP+                   | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Average items scanned before finding a memory dependence edge. | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Sizes of static and dynamic flow graphs                        | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Olden Benchmark Summary                                        | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                | WPP trace compaction due to various transformations.Overall compaction factor.Extraction times for a single function.Compacted trace sizes and extraction times.Memory trace characteristics.Distribution of load and store accesses.Dictionary size for memory access points.Distribution of static load and store points.Dynamic behavior and removed edges.Compression results using Sequitur and TWPP+.Average items scanned before finding a memory dependence edge.Sizes of static and dynamic flow graphs. |

## Abstract

Advances in program profiling techniques have led to advances in compiler optimization techniques, and *vice versa*. This dissertation makes contributions in the areas of program profiling as well as profile guided optimizations. More specifically, it designs and evaluates a new compressed representation for profile data such that profile guided optimizations can benefit from it. A type-based value profiling technique is also developed such that new data compression techniques can be designed to exploit value redundancy present in program data.

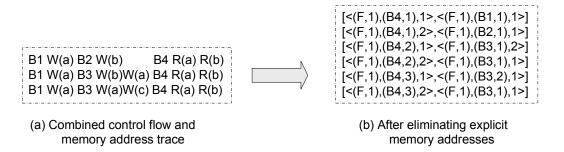

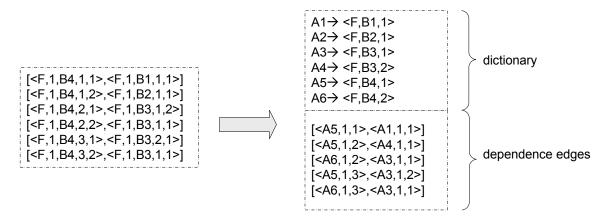

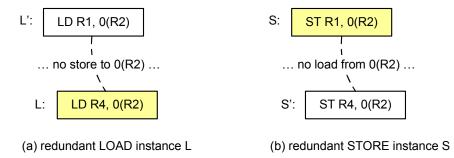

A timestamped whole program path (TWPP+) representation is proposed to compress program traces which contain both control flow and memory address information. Instead of considering a trace as a stream of symbols, TWPP+ divides a complete trace into a control flow trace part and a memory dependence trace part; each part is then reorganized to allow fast retrieval of information during data flow analyses. Execution profiles can thus be integrated to help a broad range of compiler analyses and optimizations. Three different applications are shown to demonstrate the strength of this new representation.

A type-based value profiling framework is developed to help identify redundancy in data values and thus design new data compression techniques for improving memory behavior. Two types of redundancies are identified in representations of small values and pointer addresses respectively. Both software and hardware approaches are proposed and evaluated to exploit these opportunities. The software approach through data compression transformations greatly reduces the memory footprint and speeds up the program executions with the help of six specially designed data compression instructions. The hardware approach employs compression to enable partial cache line prefetching resulting in consistent improvements in the program's execution time and reduction in memory traffic.

# CHAPTER 1 INTRODUCTION

Traditionally compile-time optimization algorithms are applied only in situations where it is known that the optimization is definitely applicable and will generate beneficial results. However, such a conservative approach fails to exploit many valuable optimization opportunities. A profile-guided optimizer uses the information of a program's past executions in two ways to aggressively optimize the program. First the profiles can be used to identify new optimization opportunities that are frequently observed during program execution but are not detected by static analyses. Second the profiles can be used to carry out sophisticated cost-benefit analysis to apply transformations that improve the performance of one part of the program at the expense of a performance loss in another part of the program.

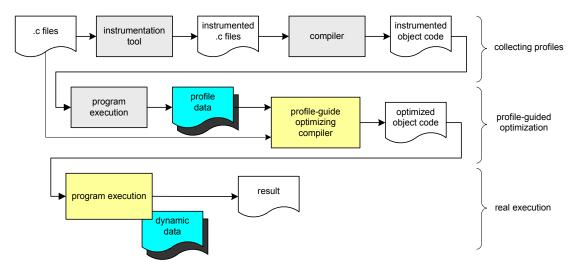

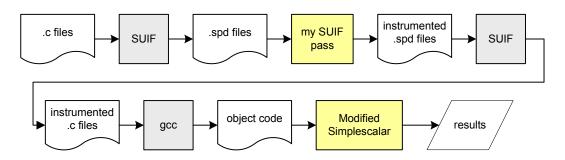

FIGURE 1.1. Overview of profile-guided compilation.

Figure 1.1 summarizes the steps of a typical profile-guided compilation. Before performing any optimization, an instrumented version of the program is generated.

The instrumented program is executed on one or more sets of representative inputs and the profiles for these executions are collected. With the help of profiles, an optimizing compiler recompiles the program and generates the optimized object code. The optimized object code is then used in all future executions with real inputs. Typically, *simple* representative sets of inputs are used in collecting profiles and profiling executions are much *shorter* than real executions. During the execution, the amount of profile data that is generated from a profiling execution is significantly *less* than that from a real execution.

# 1.1 Program profiling and profile guided optimizations

There is a close interaction between the research in program profiling and the research in the development of new profile guided optimization techniques. Advances in one area help create advances in the other, and *vice versa*.

On the one hand, one research trend in profiling is to collect more kinds of detailed and accurate profiling information from which more optimization opportunities can be discovered. Powerful optimization algorithms can then be developed to exploit these opportunities. On the other hand, with the rapid advances in computer architecture and system designs, many kinds of optimization opportunities are known to exist in many programs. However, profiling techniques are needed to collect information that can guide the design of cost-benefit analyses to effectively exploit these opportunities.

Let us consider the situations where profiling research has greatly influenced optimization research. Simple profiles were collected in earlier days and they worked well in finding more optimization opportunities than static analyses. For example node profiles consisting of execution frequencies of basic blocks in a control flow graph were collected. Compilers could be directed to optimize most frequently executed regions so that for a given fixed amount of compilation time, the improvement in program performance could be maximized. Slightly more complicated edge profiles, which count the execution frequencies of each edge in a control flow graph, can be used to enable more complex optimizations (e.g., Young *et al.* [62] proposed the use of edge profiles for interprocedural branch alignment). More complex path profiles [4], which consist of execution frequencies of acyclic sequences of basic blocks are also collected. Gupta *et al.* [22, 24, 23] used path profiles to enhance traditional optimization techniques as well as develop new ones.

Now let us consider some situations in which optimization research has driven research into new profiling techniques. Programs and architectures are increasing in complexity and creating new challenges for developing optimizing compilers. Dynamically allocated data objects are frequently used and they often lead to poor cache performance. A better data layout scheme could greatly reduce the number of cache misses and improve the overall performance. However, to assist the design of different memory layout optimizations, new types of profiling techniques are needed. Calder *et al.* [13] suggested to collect a temporal relation graph (TRG) which summarizes the usage relationship between different objects. New memory allocation policy can then be designed to allocate affiliated objects close to each other. Recent research reveals that dynamic optimizations, which optimize the program during the execution, have many advantages. However, given the restricted runtime constraints, there is demand for new profiling techniques which are cheap and yet sufficiently accurate. To support optimization in a dynamic optimization environment, Arnold [2] proposed a counter-based sampling technique that can perform effective runtime profiling.

## 1.2 Overview of the research

This dissertation further illustrates the close interaction between research in profiling techniques and profile-guided optimization opportunities. It designs and evaluates compressed representation for profiling data allowing profile-guided optimizations to benefit from this advance in program profiling. The newly developed representation is demonstrated to help in the design of new optimization algorithms. A type-based value profiling technique is also developed such that new data compression techniques can be designed to exploit value redundancy present in program data.

#### 1.2.1 Representation of profiling data

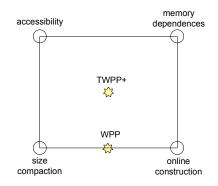

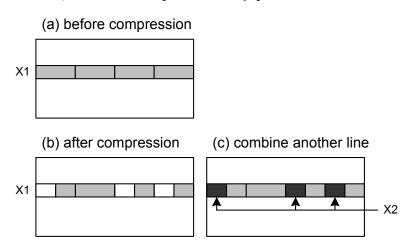

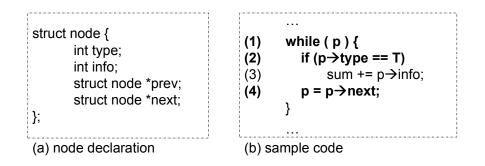

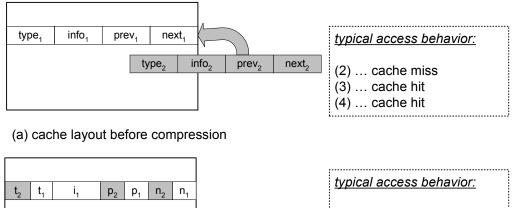

Traditional compiler optimizations perform data flow analyses based on program control flow graphs. A recent advance in profiling proposed collection of the whole program path (WPP) profiles [32] which is a compressed form of the program's control flow trace. Although WPP contains complete and accurate dynamic control flow information, it can be up to several gigabytes in uncompressed form and hundreds of megabytes in compressed form. Information retrieval is very slow using WPP. As a result, it is difficult for compiler optimizations to take advantage of this new advance in program profiling. Moreover, data dependence information is needed for inferring certain data flow facts. In this dissertation, a new representation TWPP+ is proposed to address these problems. Given a complete program trace that contains control flow trace and address trace, TWPP + explicitly separates the control flow and memory dependence information from each other. Each type of information is organized in a way that assists later compiler analyses and optimizations. Figure 1.2 compares this new representation with the whole program path (WPP) technique. While the WPP representation tries to achieve the highest possible compression ratio, the new representation puts more emphasis on accessibility, that is, the ease use of the information. Besides, the WPP representation does not consider dynamic memory dependence information which is also very important for some analyses and optimizations.

FIGURE 1.2. Comparison with whole program path.

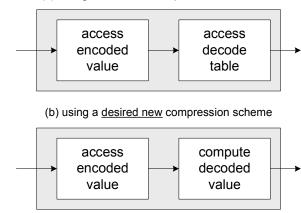

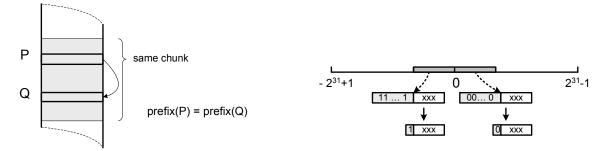

#### 1.2.2 Profiling for value redundancy detection

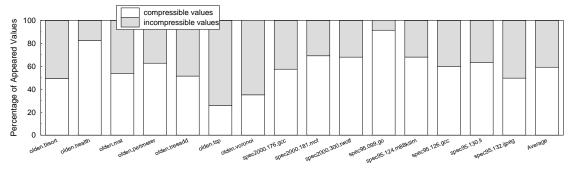

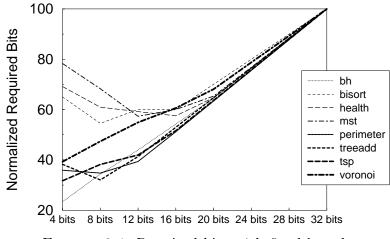

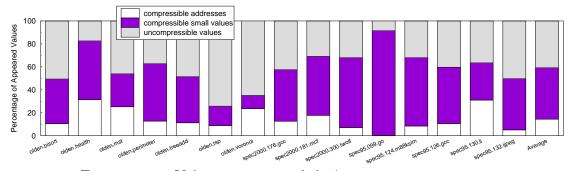

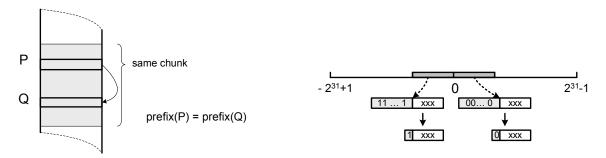

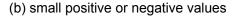

Over the last decade, while the processor speed has been improved 55% each year, the memory speed has been improved only 7% each year [43]. As a result, the memory system has become a major bottleneck in improving system performance. The situation is worsened by the fact that machine word size has increased from 8 bits to 64 bits. Recent research [64, 61] has found that there is a significant level of redundancy in dynamic value representation. Figure 1.3 shows that for a 32-bit machine, and for a spectrum of benchmark programs, on an average 59% of all accessed 32-bit values can be effectively represented by half of their original size, that is, using 16 bits.

FIGURE 1.3. Values compressible to half of their size.

By removing redundancy through dynamic data compression, cache performance could be greatly improved. However, there are no available profiling techniques aimed at catching this type of optimization opportunity. Moreover, critical runtime constraints restrict the runtime application of traditional compression techniques. In this dissertation, a new type-based profiling technique is developed to assist in the design of new dynamic data compression techniques. The potential of the new compression is further exploited through both software and hardware techniques.

# 1.3 Organization

The rest of this dissertation is organized as follows. Background research on program profiles and profile-guided optimizations is presented in Chapter 2. A timestamped whole program path (TWPP+) representation for compressing program profiles is developed and evaluated in Chapters 3, 4 and 5. Chapter 3 discusses how to compress control flow traces into TWPP. Chapter 4 enhances TWPP to include compressed memory dependence profiles. Three applications are discussed in Chapter 5 to illustrate the use of information contained in a TWPP+ representation.

A type-based profiling technique for finding value representation redundancy is proposed in Chapter 6. Using the data collected from profiling, both software and hardware data compression techniques are developed to exploit the opportunities in removing value representation redundancy. The software approach based upon data compression transformations, is discussed in Chapter 7. The hardware approach that employs compression to enable partial cache line prefetching, is discussed in Chapter 8. Conclusions and future research are discussed in Chapter 9.

# Chapter 2 Background

In this chapter, an overview of program profiling and profile-guided optimization is given. Section 2.1 reviews the types of program profiles and the commonly used techniques to collect program profiles. In section 2.2 different profile-guided optimization techniques using these profiles are briefly reviewed.

# 2.1 **Program profiles**

Program profiles provide summary information on past program executions. In practice, *different* types of profiles are collected at *different* levels of granularity and used to guide *different* program optimizations.

### 2.1.1 Type of profiles

Three types of profiles are usually used in practice: control flow profiles, value profiles and address profiles.

**Control flow profiles.** Programs are usually represented by their control flow graphs (CFGs) during compiler analyses and optimizations. A control flow trace (CFT) remembers, in their execution order, all visited basic blocks in the CFG. By examining a CFT we can compute the execution frequency of any given program subpath. As expected CFTs can be extremely large in size and a number of approximations of CFT have been proposed and used to directly measure the execution frequencies of selected program subpaths. These profiles differ in the degree of approximation involved and the costs for collecting them. The proposed approximations of control flow profiles include the following:

- *Node profiles* provide the execution frequencies of the basic blocks in the control flow graph. Such profiles are adequate for some optimizations.

- *Edge profiles* provide the execution frequencies of each edge in the control flow graph. The overhead for collecting edge profiles is comparable to node profiles. However, edge profiles are superior to node profiles because edge profiles cannot always be computed from node profiles while node profiles can always be computed from edge profiles. Edges profiles are widely used.

- *Two-edge profiles* [36] provide the execution frequencies of each pair of consecutive edges in the control flow graph. Edge profiles can always be computed from two-edge profiles but the reverse is not true. Two-edge profiles derive their increased power from their ability to capture the correlation between the executions of consecutive conditional branches and they are used in a probabilistic data flow analysis framework [36] for computing frequencies of data flow facts.

- *Path profiles* [4] provide the execution frequencies of subpaths in the control flow graph that are acyclic and intraprocedural. Since a path is acyclic, it does not include a loop back edge and since it is intraprocedural, it terminates if an entry or an exit node of a procedure is reached. Path profiles are more precise than two-edge profiles for acyclic components of a control flow graph because they capture correlation across multiple conditional branches within an acyclic graph. However, two-edge profiles can capture correlation among a pair of conditional branches along a cyclic and interprocedural paths while path profiles cannot do so.

Since all of above profiles are approximations of original traces, some research has been done to evaluate how they differ from each other. Ball *et al.* [5] gave an algorithm to estimate the lower and upper bounds of path frequencies from edge profiles. Their results show that if a large percentage of a program's total flows are definite, the estimated path frequencies from edge profiles can still identify *hot* paths. Otherwise more powerful path profiles should be used to identify *hot* paths.

Approximations are used in above profiles because the complete trace is large and it was believed to be too expensive to collect and use. This problem was addressed by Larus in [32]. He proposed to collect and compress the complete control flow graph trace using the Sequitur [40] algorithm. The compression result, identified as the *whole program path*, is a context free grammar that generates a single string which is the original control flow trace for the program. The redundancy in the original trace comes from frequently executed subpaths and it is removed by creating and reusing production rules.

**Value profiles.** Value profiles identify the specific values encountered as operands of an instruction and the frequencies with which these values are encountered. The example in Figure 2.1 illustrates the form of these profiles.

| Code:                  | Value profile:          |                                    |  |

|------------------------|-------------------------|------------------------------------|--|

|                        | (instruction, register) | Profiles (value,freq)              |  |

| <br>I1: load R3, 0(R4) | (I1,R3)                 | (0xb8d003400,10)                   |  |

| l2: R2 ← R3 & 0xff     |                         |                                    |  |

|                        | (I1,R2)                 | (0,1000)                           |  |

|                        | (l2,R3)                 | (0,100),(0x8900,200),,(0x2900,100) |  |

FIGURE 2.1. Value profiles.

Since the number of instructions in a program is large, and each operand of an instruction may potentially hold a very large number of values, collection of complete value profiles is not practical. Therefore to reduce the size of the profile data and the execution time overhead of profiling, the following two steps are taken.

First only the most frequently appearing N values are collected for a given operand. Calder et al.[11] have proposed maintaining a top-n-value table (TNV) for a register being written by an instruction. Each TNV table entry contains a pair of values: the value and the frequency with which that value is encountered. A least frequently used (LFU) replacement policy is used to choose an entry for replacement when the table is full. If we exclusively use the LFU policy for updating the TNV, the values that are encountered later in the execution may not be able to reside in the table even if they are frequently encountered. This is because they may be repeatedly replaced. To avoid this situation, at regular intervals the bottom half of the table is cleared. By clearing part of the table, free entries are created that can be used by values encountered later in the program. Both the number of entries in the table and clearing interval are carefully tuned to get good results. Collecting only the top N values not only reduces the profiling overhead, but also makes convergence to a steady state faster.

The second complimentary approach in reducing profiling overhead is to collect value profiles for only interesting instructions. Watterson and Debray [58] use a costbenefit model to identify interesting instructions. The cost is that to test whether a register has a special value; the benefit is the direct and indirect instruction savings that can be achieved by optimizing the program with this information. Control flow profiles are collected first to carry out cost-benefit analysis and to identify candidates for value profiles.

Address profiles. Address profiles can be collected in the form of a stream of memory addresses that are referenced by a program. These profiles are usually used to apply data layout and placement transformations for improving the performance of the memory hierarchy. Depending upon the optimization, the address traces can be collected at different levels of granularity. At the finest level of granularity, each memory address can be traced. Coarser level traces record references to individual objects rather than individual addresses.

A complete address trace of a program run can be extremely large. In order to compress the size of the address trace, Chilimbi [15] has proposed using the Sequitur algorithm to generate a compressed whole program stream (WPS) representation of the address trace in much the same way as Sequitur is used to compress a program's control trace. To guide the application of data layout and placement transformations, the WPS representation is analyzed to identify hot address streams. These streams represent subsequences of addresses that are encountered very frequently during the program run.

| Declarations:                          | Sample code:                                                                                                                                                                                                           | Address profile | <u>.</u>            |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|

| int flag;                              | <pre>for(i=0;i&lt;2000;i++) {     swtich (flag) {     case 1:         xa = *pa;; break;     case 2:         xb = *pb;; break;     case 3:         xc = *pc;; break;     case 4:         xd = *pd;; break;     } </pre> | Relationship    | Profiles(frequency) |

| int *pa,*pb,*pc,*pd;<br>int buf[2000]; |                                                                                                                                                                                                                        | (A(xa),A(pa))   | 500                 |

|                                        |                                                                                                                                                                                                                        | (A(xb),A(pb))   | 20                  |

| int xa,xb,xc,xd;                       |                                                                                                                                                                                                                        | (A(xc),A(pc))   | 2                   |

|                                        |                                                                                                                                                                                                                        | (A(xd),A(pd))   | 10                  |

|                                        |                                                                                                                                                                                                                        |                 |                     |

|                                        |                                                                                                                                                                                                                        | (A(pa),A(buf))  | 2000                |

|                                        |                                                                                                                                                                                                                        |                 |                     |

|                                        | <br>pa = buf[i]                                                                                                                                                                                                        |                 |                     |

|                                        |                                                                                                                                                                                                                        |                 |                     |

FIGURE 2.2. Address profiles.

While the above approach first collects complete address profiles and then processes them to identify information useful in guiding data layout and placement transformations, another approach is to directly identify the useful information. Calder *et al.* [13] have proposed an algorithm based upon such an approach. The information that they collect is represented by a graph named the temporal relationship graph (TRG). The nodes in this graph are data items of interest. Weighted links are established between pairs of nodes. If references to a pair of data items are separated by fewer than a threshold number (say N) of other data references, then the weight associated with the link between the two items is incremented. To maintain the weights of all the links, an N-entry queue is maintained which records the latest N data items that are referenced by the program. The weights on the links at the end of the program run can be used by the compiler to identify data items that should be placed close to each other for achieving good cache behavior. Figure 2.2 shows an example of the information collected using this approach.

#### 2.1.2 Collecting profiles

Programs have to be executed in order to collect the program profiles. Three approaches are commonly used in practice for collecting profiles.

Instrumentation of the original program with new code to generate the profile data is the most widely used method. The introduced instrumentation code depends upon the types of profiles being collected. There are two possible ways to insert the instrumentation code. One way is to instrument at source or intermediate code level by modifying compilers [54, 55]. The instrumented source programs are then compiled normally to generate the executable code. The other way is to use a binary level instrumentation tool [19, 51] and insert the code directly into the executable code. While high level instrumentation can trace semantic information more easily, lower level instrumentation is sometimes easier to use and flexible.

The instrumented program is slower than the original version. While usually, the overhead of instrumented code is linear in the length of the execution, techniques have been proposed to reduce its overhead. Sarkar [48] proposed a technique to reduce the overhead in collecting control flow profiles. A counter is introduced for each control dependence region in the program; since they are far fewer than the basic blocks, the profiling overhead is reduced. Ball *et al.* [4] presented an algorithm to reduce the number of profiling points during the collection of path profiles.

Hardware profiling collects execution profiles with hardware support. Most modern processors [37, 26, 27] provide some hardware mechanisms for counting various types of dynamic information, such as cache misses, memory coherence operations, branch mispredictions, and issued and committed instructions. MIPS R10000 [37] provides two 32-bit counters which can be used by the user to monitor 30 different events. Similarly, the event monitoring mechanism in the Intel Pentium 4 and Xeon processors [27] provides the flexibility to use 18 performance counters and to select 45 different events to be monitored. Hardware profiling is easy to use and incurs the least overhead. However, the counter based hardware profiling approaches lack the flexibility to monitor new events.

Simulation is another widely used approach in collecting and studying program profiles. It is especially important if we are studying the software and hardware interactions or if the target architecture does not exist. For example, Simplescalar [10], FAST [41] and RSIM [42] are cycle level architectural simulators; they provide ways to specify the features of simulated architectures. The advantage of this approach is that we can run the same program many times with different hardware configurations and study software and hardware interactions. The disadvantage is that it is very slow.

## 2.2 Profile guided optimizations

Different types of profiles are used to expose different optimization opportunities and assist in the development of different optimization techniques. These opportunities become available because of the dynamic inequality characteristics, e.g. some paths are executed more frequently than others, some variables are nearly constant, some data objects are referenced together, etc. A more precise cost-benefit model could be set up to evaluate this inequality and optimization transformations could thus be developed to generate more efficient code. This section reviews the optimization techniques proposed in the literature.

#### 2.2.1 Profile guided control flow related optimizations

Control flow profiles are most widely used in optimization. Techniques are designed through *code specialization*, a technique that creates both optimized and unoptimized copies of statements and appropriate copy of the statement is executed depending upon the conditions that hold. Different code specialization algorithms are categorized primarily into two classes of transformations that are used to carry out code replication and enable specialization of conditionally optimizable code: code motion of different types and control flow restructuring with varying scope.

The basic form of code motion, namely safe code motion, in addition to honoring the program's data dependences, guarantees that for every execution of a statement during the execution of the optimized code, there exists a corresponding execution of the statement during the execution of the unoptimized code. As a consequence, it must be the case that if an exception occurs during the execution of optimized code, it would have also occurred during the original execution. Hardware support present in modern processors such as IA-64 [21] allows relaxation of the above constraint. In particular, *speculative code motion* allows the compiler to introduce executions of a statement in the optimized code that are not present in the unoptimized code. *Predicated code motion* [21] creates more opportunities by moving code out of control structures but still under correct predicates.

Control flow restructuring creates unoptimized and optimized copies of the statement and places them along the incoming edges. The primary cost in restructuring is the growth of code size. Control flow restructuring can be performed at different control flow granularities and scopes. Increasing the scope of restructuring also increases the growth of code size. Function inlining is one way to achieve interprocedural control flow restructuring. To limit code growth while performing interprocedural optimizations a couple of alternative techniques have been proposed: partial inlining of frequently executed paths through a procedure [25] and creating procedures with multiple entries and multiple exits [6].

Existing transformations are enhanced and new transformations are developed to take advantage of profiles. They are used to develop a more precise cost-benefit model and estimate whether the benefit achieved from a particular transformation outweighs the cost that it introduced. For example, partial redundancy elimination (PRE) is traditionally performed using safe code motion [29]. The use of speculation was first proposed in [24, 23]. A control flow restructuring approach was proposed in [52]. A combination of all above transformations to achieve greater benefits at lower cost is discussed in [7].

#### 2.2.2 Profile guided value optimizations

Value profiles can be used to identify almost invariant variables for constant folding, strength reduction, code specialization, adaptive execution and guiding dynamic compilation.

Muth, Watterson and Debray [39] introduced a value profile based code specialization technique which has in three steps. First, using basic block profiles, program points and registers are identified where specialization might be profitable. Second value and expression profiles are obtained for these program points. Third, these collected profiles are used to carry out specialization for those program points that are deemed profitable.

Dynamic optimization [3] and adaptive execution [28] generate specialized code either from scratch or from a statically generated template. Value profiles can help to identify the semi-invariant variables statically and reduce greatly the optimization cost at runtime.

Calder and Feller *et al.* [12] discussed different computer architecture components that can benefit from value profiles. Hardware value predictors [34], for example, can benefit in several ways from value profiles. By classifying instructions into predictable, not predictable, or hard to predict, one can determine which instructions to statically predict or not to predict. Value profiling can even be used to classify instructions indicating which type of predictor would better predict the instruction in a hybrid predictor. This increases the prediction accuracy and decreases the conflicts or aliasing in a prediction table.

#### 2.2.3 Profile guided memory optimizations

Over the past decade, while the processor speed have risen by 55% each year, the memory speeds have only improved by 7% each year. As a result, the memory becomes a major bottleneck in performance improvement and so has drawn a lot of attention. The techniques proposed to optimize memory performance span a wide range of categories.

- Object placement. This type of technique determines a better placement scheme of data objects to improve cache behavior. Memory forwarding proposed by Luk and Mowry [35] attached one bit to each word in the memory. An object can be migrated dynamically according to its runtime behavior. After its migration, the memory address where it previously resided saves an indirect pointer to the new address. The additional bit is set to indicate that the object has moved. Other approaches try to place an object in a desired places. *Ccmalloc* [17] for example enhanced the system memory allocator by one more parameter used as its parent pointer. Whenever possible, the new object is placed into the same cache block as the existing object. The address profiles can be used to identify objects that are accessed contemporaneously.

- **Object layout.** This type of technique determines a layout of fields within a large data object to improve cache locality. A data structure is often defined by the programmer to support code readability. The compiler simply uses a memory layout for the fields which mirror the order they are declared. However,

FIGURE 2.3. A ccmalloc example.

this order may not be consistent with the order that incurs fewer cache misses. Truong *et al.* [56] evaluated an approach to reorder the fields and showed that a node that spans several cache blocks can take advantage of cache line prefetching and reduce cache pollution, thus improving cache performance.

• <u>Hybrid scheme</u>. This type of technique combines the object placement and layout approaches to further improve the performance. In [16], object splitting technique was proposed to split an object into two parts: the hot primary part and the cold secondary part. Hot fields are accessed directly while the cold ones are accessed through a pointer stored in the hot part. Locality is improved by reducing the data object size and benefits most memory accesses for hot fields.

# CHAPTER 3

# Compressing the control flow trace

A control flow trace is a sequence of basic block instances in their execution order. Node, edge or path profiles can be viewed as lossy compressed representations of the control flow trace. Until recently, it was believed that a complete control flow trace is too expensive to collect and use. However, Larus [32] recently demonstrated that it is feasible to effectively collect a whole program path (WPP), which is the compressed form of a complete control flow trace. By using the Sequitur [40] algorithm, Larus showed that a control flow trace which is typically very large (100's of MBytes), can be compressed (10's of MBytes) and saved for future analysis.

While the compression algorithm proposed by Larus is highly effective, the compression is accompanied with a loss in ease of accessibility to information. For example, path traces pertaining to a particular function cannot generally be obtained without examining the entire compressed WPP representation. This is a serious drawback because typically an application using the WPP can be expected to make a series of requests for profile data for individual functions, that is, each request asks only for a small subset of the overall information contained in a WPP. Repeated extraction operations to satisfy these requests are likely to result in high analysis time costs. Therefore it is important to design a representation from which path traces of individual functions can be rapidly accessed.

The above loss of accessibility is a natural consequence of of treating the entire control flow trace as a single data stream during *compression*. As a result the information corresponding to a given function is scattered throughout the compressed trace and can in general be located only by examining the entire compressed trace.

In order to solve this problem a new compression approach is proposed in this

dissertation which aims at simultaneously reducing the size of the control flow trace and providing easy access to subsets of information within the compressed trace. The approach organizes the information contained in a complete trace as follows. The control flow trace is first broken into *path traces* corresponding to individual function calls, and all of the path traces for a given function are stored together as a block. Therefore information regarding a specific function can be readily accessed. In order to ensure that the complete control flow can be reconstructed from individual path traces, a *dynamic call graph* which links the *path traces* together is also maintained. The detailed compression algorithm for control flow traces is presented in this chapter.

The rest of this chapter is organized as follows. Section 3.1 introduces the new timestamped whole program path (TWPP) representation. The algorithm steps are given to convert a control flow trace into the final representation. Section 3.2 presents the experimental results, comparing the compression ratio as well as the access time using different compression algorithms. Section 3.3 summarizes the chapter.

## 3.1 TWPP: Timestamped whole program path

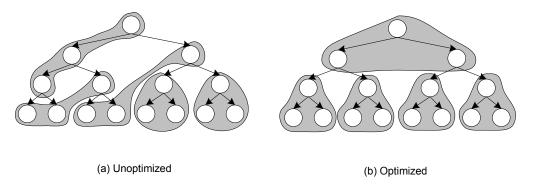

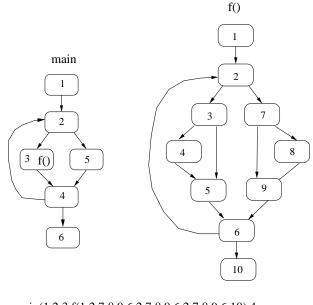

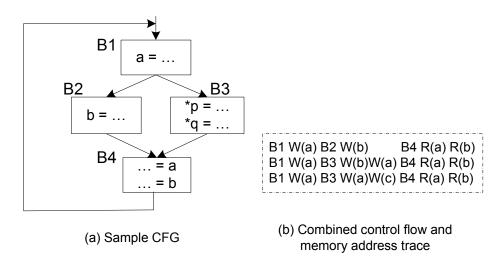

As mentioned earlier, a whole program path (WPP) is the compressed form of a control flow trace from a program execution. Consider the program and a sample control flow trace shown in Figure 3.1. The trace shows that the loop in main iterates 5 times and in each iteration the function **f** is called. The loop in function **f** iterates 3 times for each call. Looking at the WPP for a small program we observe two things: WPPs for real applications can be expected to be quite large (e.g., 100's of MBytes) and in its current linear form WPP is difficult to use (e.g., in order to extract trace information for a subpath in main or function **f**, we must examine the entire WPP). Next we present a step by step transformation of the above WPP to achieve two goals: compaction of the WPP to reduce memory requirements and organization of the WPP information for faster access to path traces of individual functions.

$\begin{array}{l} \text{main}(1.2.3.f(1.2.7.8.9.6.2.7.8.9.6.2.7.8.9.6.10).4.\\ 2.3.f(1.2.7.8.9.6.2.7.8.9.6.2.7.8.9.6.10).4.\\ 2.3.f(1.2.3.4.5.6.2.3.4.5.6.2.3.4.5.6.10).4.\\ 2.3.f(1.2.7.8.9.6.2.7.8.9.6.2.7.8.9.6.10).4.\\ 2.3.f(1.2.3.4.5.6.2.3.4.5.6.2.3.4.5.6.10).4.\\ \end{array}$

FIGURE 3.1. An uncompacted control flow trace.

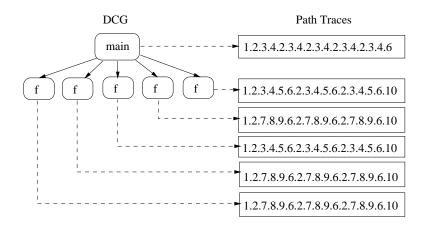

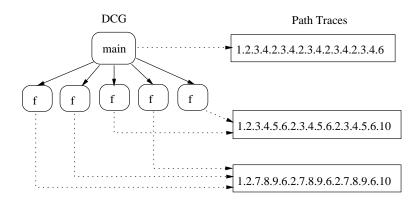

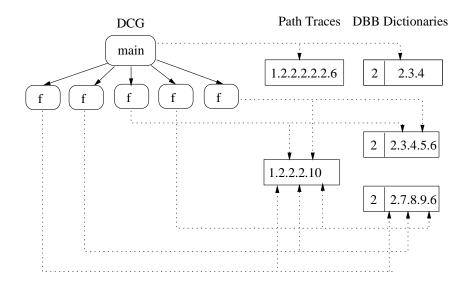

**Partitioning WPP into path traces.** We partition the WPP into *path traces* corresponding to individual function calls and all of the path traces for a given function are stored together as a block. Therefore information regarding a specific function can be readily accessed. In order to ensure that the complete WPP can be reconstructed from individual path traces, a *dynamic call graph* (DCG) which links the *path traces* together is also maintained. Figure 3.2 shows this representation of the WPP for our example program. Clearly from this representation the WPP form of Figure 3.1 can be easily constructed. More importantly one can rapidly search for occurrences of a given path (intraprocedural or interprocedural). The path traces of interest are located and then examined for desired information. To search for an occurrence of a path in main we need to only examine one-sixth of the total trace in Figure 3.2.

FIGURE 3.2. WPP organized using the DCG.

FIGURE 3.3. WPP after redundant path trace removal.

Eliminating redundant path traces. The WPP can be greatly reduced in size by eliminating duplicate path traces generated by different calls to the same function. In Figure 3.2, corresponding to the 5 calls to function **f**, there are only two unique path traces. Therefore the WPP representation can be transformed to eliminate redundant path traces as shown in Figure 3.3. This technique is very effective because although many functions are called numerous times, they tend to follow one of a small subset of paths through the function body. For example, in a WPP collected from executing gcc we found that function \_rtx\_equal\_p was called 355189 times but it generated only 35 unique path traces.

<u>Creating dictionaries of dynamic basic blocks.</u> Another technique that we employ replaces a sequence of static basic block ids that correspond to a *dynamic basic block* by a single id. A *dynamic basic block* (DBB) belonging to a path trace is a sequence of static basic blocks that is always entered from the first block and exited from the last block in the path trace. Since DBBs can often appear inside loops, they are often repeated many times in a path trace. Thus, replacing them by a single id can significantly reduce the size of the WPP.

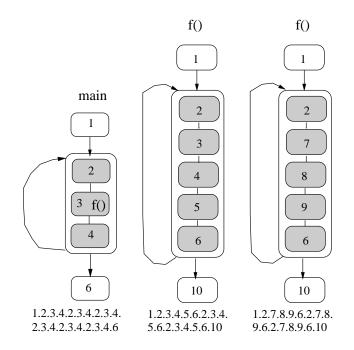

Each path trace is processed as follows: a dictionary of DBBs is created by constructing a dynamic control flow graph and finding chains of static blocks representing DBBs in it. Each DBB is assigned the block id of the first static block in it and accordingly the path trace is modified by deleting all but the first id in each occurrence of a DBB. Once all compacted path traces and dictionaries are obtained, duplicate path traces and dictionaries are also eliminated. In this transformed form, each node in the dynamic call graph has an associated tuple (t, d) where t is a path trace and d is a dictionary. Figure 3.4 shows the chains of static basic blocks that form dynamic basic blocks for the three path traces in Figure 3.3. After creating dictionaries and compacting path traces, we are left with one path trace and two dictionaries for function f as shown in Figure 3.5.

FIGURE 3.4. DBBs and dynamic control flow graphs.

FIGURE 3.5. WPP after creating dictionaries of DBBs.

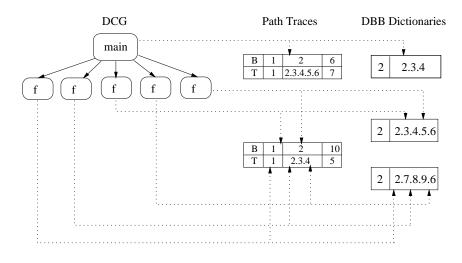

**Timestamped WPP representation.** In the WPP representation described so far, the execution trace of a given function invocation is represented by a sequence of basic blocks visited during its execution. While such a path trace representation is adequate for identifying hot paths through a program, it is not the most appropriate for performing data flow analysis. Since profile-limited data flow analysis is carried out from the perspective of basic blocks, it is more appropriate to organize the traces from the perspective of dynamic basic blocks. Next we describe the *timestamped* WPP (TWPP) representation which achieves this goal.

The execution of the function can be viewed from the perspective of time steps, where each time step corresponds to the execution of a dynamic basic block. Therefore a path trace for a function call in a WPP representation can be viewed as a mapping between time steps, or *timestamps*, and dynamic basic blocks. In contrast, the TWPPs represent a mapping between dynamic basic blocks and an ordered sets of timestamps. Let  $\mathcal{T}$ ,  $\mathcal{B}$ , and  $\mathcal{P}(\mathcal{T})$  denote the set of timestamps, set of dynamic basic blocks, and the power set of timestamps associated with the path trace of a given function call f. A path trace in WPP and TWPP forms is represented by the following mappings:

# $WPPPathTrace_{f}: \mathcal{T} \to \mathcal{B}$ $TWPPPathTrace_{f}: \mathcal{B} \to \mathcal{P}(\mathcal{T})$

Consider the WPP of Figure 3.5. The WPP trace 1.2.2.2.2.2.6 corresponds to the following  $\mathcal{T} \to \mathcal{B}$  mapping:  $\{1 \to 2, 2 \to 2, 3 \to 2, 4 \to 2, 5 \to 2, 6 \to 2, 7 \to 6\}$ . When transformed to TWPP form it is represented by the following  $\mathcal{B} \to \mathcal{P}(\mathcal{T})$  mapping:  $\{1 \to \{1\}, 2 \to \{2,3,4,5,6\}, 6 \to \{7\}\}$ . The complete uncompacted TWPP for this example is shown in Figure 3.6.

**Compacting TWPP path traces.** The path traces in TWPP form can be further compacted because often a subsequence of timestamp values corresponding a

FIGURE 3.6. TWPP form.

dynamic basic block forms an arithmetic series. This situation arises particularly when the same path within a loop body is traversed repeatedly during different loop iterations. The subsequences that form arithmetic series are compacted yielding a sequence of entries which are of the following form: l (singleton), l : h (l.l + 1.l + 2...h, i.e., series with step 1), or l : h : s (l.l + s.l + 2s...h, i.e., series with step s). As we can see, depending upon its form, an entry is represented using one, two or three positive integer values. We store the timestamps corresponding to a block merely as a sequence of integers. For correct interpretation of the information we need to encode the boundaries that separate the variable length entries. This information is encoded in the signs (+ or -) of the values and therefore it does not require any increase in the size of the path trace. In particular, the last number in a each entry is stored as a negative number. By using the sign to encode the end of an entry we limit the largest timestamp value that is available to us since we can no longer use unsigned integers. However, our experience with the benchmarks considered shows that the timestamp value does not overflow because individual path traces are much smaller than the complete WPP.

Notice that the sequence of timestamps assigned to dynamic basic block 2 in Figure 3.6 form an arithmetic series since block 2 is executed repeatedly during suc-

FIGURE 3.7. Compacted TWPP.

cessive loop iterations. Therefore the TWPP can be compacted into:  $\{1 \rightarrow \{-1\}, 2 \rightarrow \{2: -6\}, 6 \rightarrow \{-7\}\}$ . Notice that the last number in each sequence is a negative number. The complete compacted form of TWPP for our running example is shown in Figure 3.7.

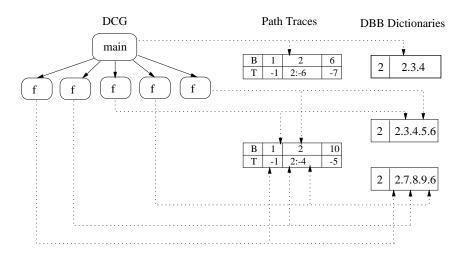

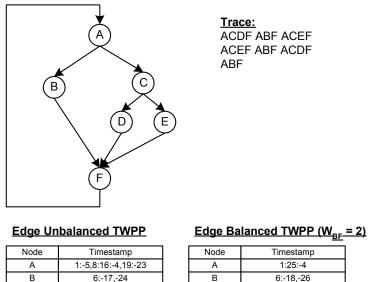

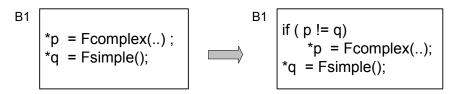

It is also possible to increase the compressibility of timestamps associated with basic blocks using a simple technique. Consider a situation in which different paths through a loop body of a function contain different numbers of nodes. For example, in Figure 3.8, there are three paths from A to F: paths ACDF and ACEF contain three nodes while ABF contains 2 nodes. Even though nodes A and F are executed along each of these paths, their timestamps are irregular due to the different number of nodes along the paths. However, if all paths contained the same number of nodes, then no matter which path is taken during each loop iteration, the nodes A and F would have had perfectly compressible series of timestamps. To address this problem we associated weights to edges where the weights are used to generate timestamps. In particular, the weight of an edge represents the amount by which the timestamp is incremented when the edge is traversed. By assigning weights to edges such that sum of weights of edges along each of the paths through the loop is the same, we can

| ~ | 13,0.104,1323          |

|---|------------------------|

| В | 6:-17,-24              |

| С | 2:-9,13:-20            |

| D | 3:-21                  |

| E | 10:-14                 |

| F | 4:-7,11:-15,18:-22,-25 |

|   |                        |

FIGURE 3.8. Balancing example.

guarantee that nodes that are visited along each path have compressible timestamps. In our example the edge BF is assigned the weight 2 while all the other edges are assigned the weight of 1 in order to balance the paths. The result is that the timestamps for nodes A and F can now be compressed and the size of TWPP representation of nodes A and F is further reduced.

**Compacting the DCG.** The dynamic call graphs resulting from executions of large application programs can also be quite large. Therefore in addition to compacting the path traces, we also compress the DCG. For this purpose we considered the popular dictionary based approaches proposed by Ziv and Lempel [65, 66]. In particular, we used Welch's variation of Ziv and Lempel's adaptive dictionary based technique which is also referred to as the LZW algorithm [60].

# **3.2** Implementation and experiments

The TWPP algorithm has been implemented and evaluated to compact whole program paths for several benchmark programs from the SPECint95 suite [50]. The original WPPs used in the experiments were generated using the Trimaran compiler infrastructure [55]. A WPP consists of two parts: the dynamic call graph (DCG) and the individual traces for function calls (which are collectively referred to as the WPP traces). The sizes of WPPs used in the experiments are shown in Table 3.1. The experiments are aimed at studying the effectiveness of our compaction techniques in reducing memory requirements and the effectiveness of organization of the WPP information for faster access.

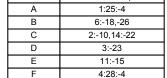

| Program   | DCG  | WPP         | Total     |

|-----------|------|-------------|-----------|

|           | (MB) | traces (MB) | size (MB) |

| 099.go    | 6.0  | 170.0       | 176.0     |

| 126.gcc   | 34.7 | 489.5       | 524.2     |

| 130.li    | 6.6  | 78.3        | 84.9      |

| 132.ijpeg | 1.7  | 266.9       | 268.6     |

| 134.perl  | 3.4  | 41.5        | 44.9      |

TABLE 3.1. Sample input traces used in the experiments.

|           | WPP tr       | ace after     | Compacted    | OWPP / |

|-----------|--------------|---------------|--------------|--------|

| Program   | Redundancy   | Dictionary    | TWPP trace   | CTWPP  |

|           | removal - MB | creation - MB | - MB         |        |

| 099.go    | 27.0 (x6.30) | 17.1 (x1.58)  | 17.6 (x0.97) | 9.7    |

| 126.gcc   | 86.5 (x5.66) | 50.8 (x1.70)  | 32.9(x1.54)  | 14.9   |

| 130.li    | 8.5 (x9.21)  | 5.3 (x1.60)   | 1.1 (x4.81)  | 71.2   |

| 132.ijpeg | 28.1 (x9.50) | 20.8 (x1.35)  | 5.7 (x3.65)  | 46.8   |

| 134.perl  | 7.2 (x5.76)  | 1.7 (x4.24)   | 0.02 (x85.0) | 2075   |

TABLE 3.2. WPP trace compaction due to various transformations.

| Program   | Compacted | Compacted TWPP (MB) |              | Total | Compaction |

|-----------|-----------|---------------------|--------------|-------|------------|

|           | DCG (MB)  | Traces              | Dictionaries | (MB)  | factor     |

| 099.go    | 6.6       | 17.6                | 2.3          | 26.5  | 7          |

| 126.gcc   | 13.8      | 32.9                | 4.9          | 51.6  | 10         |

| 130.li    | 5.3       | 1.1                 | 0.04         | 6.4   | 13         |

| 132.ijpeg | 1.0       | 5.7                 | 0.6          | 7.3   | 37         |

| 134.perl  | 0.7       | 0.02                | 0.02         | 0.7   | 64         |

TABLE 3.3. Overall compaction factor.

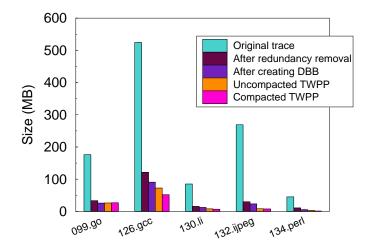

**Compaction study.** Table 3.2 shows the sizes of the WPP traces in their various forms. As we can see, the three compacting transformations, removal of redundant path traces, creation of DBB dictionaries, and transformation to compacted TWPP form are all very effective in reducing the WPP trace size. The ratio of the sizes of original WPP traces (OWPP) and compacted TWPP traces (CTWPP) gives us the compression factor which varies from 9.7 to 2075 for our sample traces. The sizes of the WPP traces after each of the three transformations as well as the compression factors corresponding to each of the transformations are also shown separately in parenthesis in Table 3.2. The results show that each of the transformations is an important source of compaction.

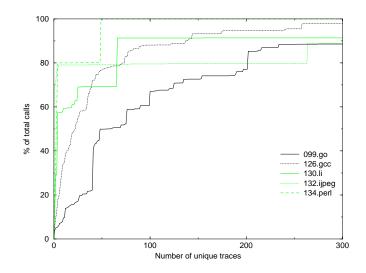

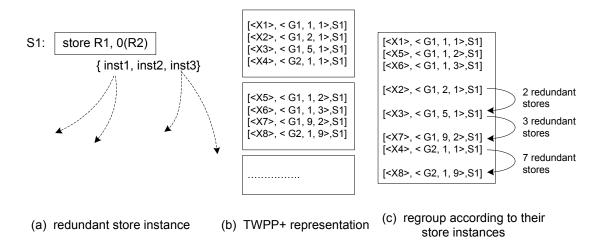

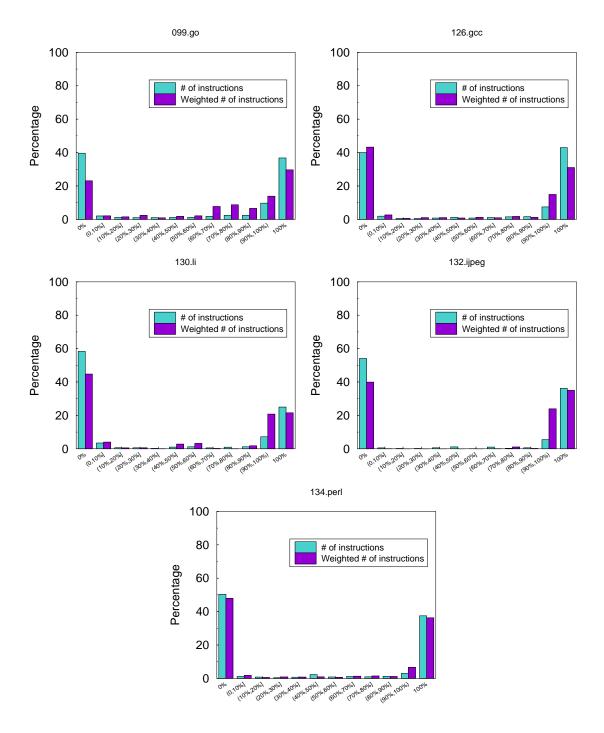

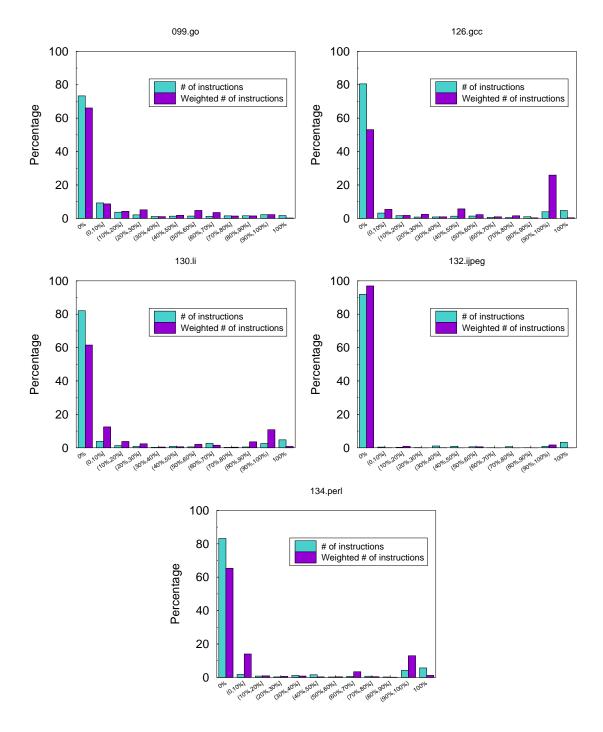

A large factor of size reduction comes from removing redundant path traces (5.66 - 9.50). The reason for this large reduction becomes clear when the data in Figure 5.1 is examined. This figure gives the percentage of total function calls (plotted along Y-axis) that can be attributed to functions with at most N unique path traces (N is plotted along the X-axis). For 130.li, 132.ijpeg, and 134.perl programs 57-80% of all function calls are attributable to functions with at most 5 unique path traces. For 126.gcc and 099.go over 50% of function calls are attributable to functions with at most 5 unique path traces that most 25 and 50 unique traces respectively. Given that the number of function calls made during the runs of these benchmarks were in hundreds of thousands, we can see that the degree of redundancy in path traces is very high.

FIGURE 3.9. Trace redundancy.

The creation of dictionaries results in compaction of WPP traces by factors ranging from 1.35 to 4.24. The conversion into compacted TWPP form results in further reductions. For four out of five benchmarks, compacted TWPP traces provide reductions in the sizes of WPP traces by factors ranging from 1.54 to 85. The only case in which compacted TWPP trace is slightly larger is the 099.go program where the compacted TWPP trace was 3% larger than the compacted WPP trace prior to its conversion to TWPP form. These results are very encouraging because not only is the TWPP representation suitable for profile-limited data flow analysis, it is also compact.

The compacted sizes at different algorithm steps are plotted in Figure 3.10 which gives a visual comparison. The step to eliminate redundant path traces is very effective and the step to convert to TWPP representation also contributes a lot to the compression.

The breakdown of different components of a WPP and the overall compaction factors for the complete WPP (DCG + WPP trace) are given in the Table 3.3. For the sample WPPs used in these experiments the overall WPP compaction factor ranges from 7 to 64.

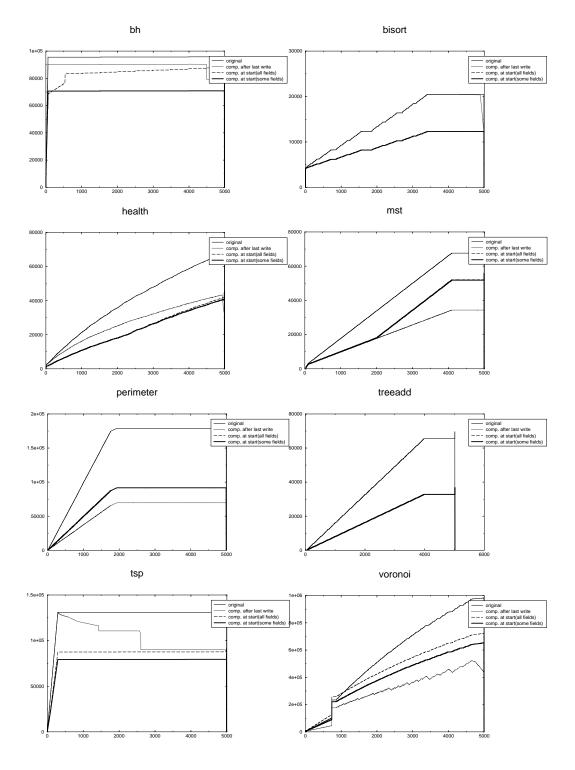

FIGURE 3.10. Compacted size at each TWPP step.